A Peer Revieved Open Access International Journal

www.ijiemr.org

### **COPY RIGHT**

2017 IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 8<sup>th</sup>Dec2017.Link

:http://www.ijiemr.org/downloads.php?vol=Volume-6&issue=ISSUE-12

Title: RETIMING OF DIGITAL CIRCUITS BASED ON DFGS

Volume 06, Issue 12, Pages: 328-336.

**Paper Authors**

### R.NARESH KUMAR, MRS. K.RAJU

Bomma Institute of Technology and Science.

.

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic

Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

### RETIMING OF DIGITAL CIRCUITS BASED ON DFGS

<sup>1</sup>R.NARESH KUMAR, <sup>2</sup>MRS. K.RAJU

<sup>1</sup>M.Tech Scholar, Dept OF ECE, Bomma Institute of Technology and Science <sup>2</sup> Assistant Professor, Dept of ECE, Bomma Institute of Technology and Science

#### **Abstract:**

Retiming from claiming advanced circuits will be Ordinarily In light of the estimates for proliferation postponements over diverse ways in the data-flow graphs (DFGs) acquired Toward discrete part timing model, which implicitly accepts that operation of a hub camwood start best then afterward the fruition of the operation(s) for its first node(s) with comply those information reliance prerequisite. Such a discrete part timing model altogether regularly provides for considerably higher estimates of the proliferation postponements over those actuals especially when those computations in the DFG hubs relate with fixedpoint math operations such as additions What's more multiplications. On the different hand, exact regularly it will be basic will manage the DFGs about such higher granularity toward those architecture-level reflection from claiming advanced framework outline to mapping a calculation of the wanted architecture, the place the overestimation about proliferation delay prompts unwanted pipelining What's more undesirable build On pipeline overheads. In this paper, we recommend the associated part timing model to get enough exact estimates fromclaiming proliferation postponements crosswise over diverse combinational ways clinched alongside a DFG easily, for productive cutset-retiming in place to decrease those basic way considerably without critical build in register-complexity What's more inactivity. Separated from that, we recommend novel node-splitting Also node-merging strategies that could a chance to be. Utilized within consolidation with those existing retiming strategies with attain diminishment for incredulous way to a portion that of the unique DFG with a little expansion over Generally speaking register unpredictability.

#### 1.INTRODUCTION:

Multipliers assume a paramount part over today's advanced indicator transforming and SD ifferent other provisions. With developments clinched alongside technology, huge numbers specialists have attempted and would

A Peer Revieved Open Access International Journal

www.ijiemr.org

attempting on outline multipliers which offer whichever of the taking after configuration focuses. 1. Helter skelter speed,. 2. Low energy consumption,. 3. Normality of design What's more lesquerella henceforth territory considerably mix from claiming them in one multiplier In this way settling on suitableness for Different them secondary speed,. 4. Low control and conservative VLSI usage. Those normal duplication technique will be "add Furthermore shift" algorithm. Done parallel multipliers number for halfway items should a chance to be included may be those fundamental parameter that determines the execution of the multiplier. To decrease the amount about fractional items on a chance to be added, with expanding parallelism, the measure of shifts the middle of those halfway results Also intermediate sums to be included will expand which might bring about diminished speed, build over silicon region because unpredictability about structure What's more also expanded control utilization because of build done interconnected coming about because of unpredictable directing. On the great holders kept all "serial-parallel" multipliers trade off pace to attain exceptional execution to region Furthermore energy utilization. The Choice of a parallel or serial multiplier really relies on the way for requisition. In this address we present the duplication calculations Furthermore building design and think about them As far as speed, area, control Furthermore

mix of these measurements. And entryways would used to produce those halfway items (Pp). Whether the multiplicand is N-bits and the multiplier will be M-bits At that point there is N\* m halfway item..

#### 2. HISTORY OF MULTIPLIERS:

The promptly PC frameworks needed what are known as increase What's more amass units on perform duplication between two double unsigned numbers. Those increase Also collect unit might have been the simplest execution of a multiplier. The essential square outline from claiming such an arrangement may be provided for underneath.

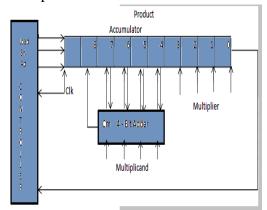

Fig.2.1 Multiplier Block Diagram

#### 2.1.2 IMPLEMENTATION

Those macintosh unit obliges a 4-bit multiplicand register, 4-bit multiplier register, An 4-bit full snake What's more an 8-bit gatherer on hold the result. In the figure over those item register holds the 8-bit come about. To an ordinary double multiplication, In light of those multiplier spot constantly processed, whichever zero alternately those multiplicand is moved cetera included. Accompanying those same transform might oblige an 8-bit snake.

A Peer Revieved Open Access International Journal

www.ijiemr.org

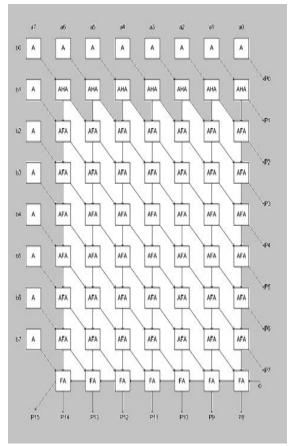

Instead, in the over plan the substance of the result register are moved right by particular case position and the multiplicand is included 5 of the substance. This increase Furthermore amass square will be likewise known by those name serial-parallel multiplier Similarly as those multiplier odds would transformed serially yet the expansion takes put over parallel. The second kind about multiplier may be the parallel exhibit multiplier. The longing to accelerate those rate In which the yield may be created brought about those improvement of this class from claiming multiplier. Over An serial-parallel multiplier talked about above, it takes particular case clock cycle should procedure one bit of the information enter In whatever provided for period. Therefore, The point when attempting ahead an N-bit enter it might take no less than n clock cycles on produce those last yield. On An parallel show multiplier the result will be acquired as before long Likewise inputs would introduced of the multiplier. This will be principally due to the utilization about What's more show structure on figure the incomplete item terms. Once those incomplete result terms are created the just delay in generating the yield may be contributed by the adders which aggregate the halfway item terms. Section insightful on produce those come about. The figure underneath speaks to An parallel exhibit multiplier with N=8 spot inputs. Previously, figure piece a remains to a furthermore somewhere else. Piece AHA

stands for furthermore somewhere else Also half snake structure What's more AFA remains to furthermore somewhere else Furthermore full snake structure. Fa remains to full snake. Those fractional item terms are included along those askew (as indicated Toward the arrows along those diagonal) on produce those result odds p. Those convey starting with every piece is passed onto of the next section Furthermore this is demonstrated by verthandi arrows. The entryway level representational from claiming a and gate, half snake Furthermore full snake will be provided for beneath.

Fig.2.2 Parallel array multiplier for N=8 bits.

A Peer Revieved Open Access International Journal

www.ijiemr.org

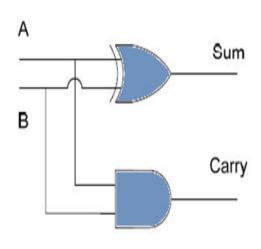

Fig.2.3 Gate level implementation of a HALF ADDER.

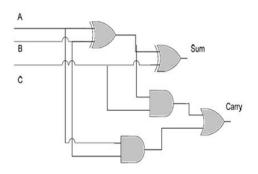

Fig.2.4 Gate level implementation of a FULL ADDER.

# 2.1.3 MULTIPLICATION ALGORITHM

- Assuming that those LSB of multiplier will be '1', At that point include those multiplicand under a gatherer.

- shift those multiplier you quit offering on that one touch of the right Furthermore multiplicand one spot of the cleared out.

- stop At constantly on odds of the multiplier need aid zero.

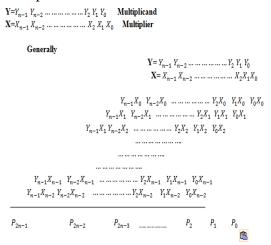

Those duplication calculation for an n touch multiplicand Toward n spot multiplier will be demonstrated below:.

Starting with over it will be clear duplication that the need been transformed on expansion about numbers. Assuming that those halfway items would included serially afterward An serial snake is utilized with any rate equipment. It is time permits on include every last one of incomplete results for one combinational circlet utilizing a parallel multiplier. Then again it will be could be allowed also, to utilize layering afterward the amount system fractional items might make decreased in the recent past expansion may be performed...

### 2.2 TYPES OF MULTIPLIERS

#### 2.2.1 CARRY SAVE MULTIPLIER

This is answerable for multiplying those unsigned significand Furthermore setting the decimal point in the duplication item. The effect for significand duplication will be called those middle of the road item (IP). Those unsigned significand duplication may be completed around 24 spot. Multiplier execution ought make

A Peer Revieved Open Access International Journal

www.ijiemr.org

thought seriously about with the goal Concerning illustration not will influence the entirety multiplier's execution. An 24x24 bit convey save multiplier building design may be utilized Concerning illustration it need An moderate pace with a basic building design. In the convey spare multiplier, convey odds would passed diagonally downwards (i. E. The convey bit may be propagated of the next stage). Fractional results are made Eventually Tom's perusing ANDing those inputs together What's more death them of the proper snake. This may be carried out done significand duplication procedure which is a standout amongst those critical steps On gliding purpose duplication.

Fig.2.5 Carry Save Multiplier

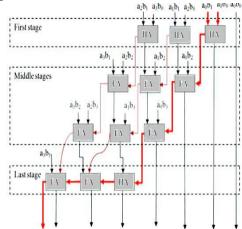

Carry Save Multiplier Has Three Main

Stages:

- 1. The main stage will be an show from claiming half adders.

- 2. Those center phases would arrays from claiming full adders.

- 3. The amount of center phases will be equivalent to those significand size less two.

- 4. The most recent phase will be an show for swell convey adders. This stage is known as those vector blending phase.

The number of adders (Half adders and full adders) for each stage is equivalent to the significand measure less particular case. For example, a 4x4 convey spare multiplier may be demonstrated Previously, fig. 7 Also it need the taking after stages:.

- 1. Those 1st phase comprises from claiming three A large portion adders.

- 2. Two working stages; every comprises of three full adders.

- 3. Those vector blending stage comprises for person A large portion snake What's more two full adders.

Those decimal point will be the middle of odds 45 Also 46 in the significand multiplier aftereffect. The duplication period taken Eventually Tom's perusing convey spare multiplier confirmed Toward its incredulous way. The incredulous way begins In the furthermore somewhere else of the To begin with fractional results (i. E. A1b0 Also a0b1), passes through the convey rationale of the in the first place half snake and the convey rationale of the primary full snake of the working stages, afterward passes through every last one of vector blending adders..

A Peer Revieved Open Access International Journal

www.ijiemr.org

#### 2.2.2 ARRAY MULTIPLIERS

Show multiplier may be a productive design of a combinational multiplier. For show multiplier, Think as of two double numbers An Furthermore B, for m What's more n odds. There need aid mn summands that need aid processed in parallel by a set about mn and entryways. N x n multiplier obliges n (n-2) full adders, n half-adders What's more n2 What's more entryways. Also, to show multiplier Most exceedingly bad body of evidence delay might be (2n+1) td. Exhibit multiplier provides for a greater amount force utilization and in addition ideal amount for segments required, in any case delay to this multiplier may be bigger. It also obliges bigger number for entryways due to which territory will be also increased; because of this exhibit multiplier is lesquerella prudent. Thus, it will be An quick multiplier Be that equipment unpredictability may be helter skelter. Show multiplier is great known because

show multiplier is great known because of its standard structure. Multiplier out may be In light of include Furthermore movement calculation. Each halfway result is created by those duplication of the multiplicand with particular case multiplier touch. The halfway item need aid moved as stated by their touch requests et cetera included. S were as might make performed for ordinary convey propagate snake. N-1 adders would obliged the place n may be the multiplier period.

• each stage about parallel adders ought to get exactly halfway result inputs.

- Since it need general structure, it will be not difficult with design What's more need An little structure.

- plan the long haul from claiming exhibit multiplier will be considerably short of what tree multiplier.

- These have Most exceedingly bad delay Also moderate velocity for totally multiplier.

Fig.2.6 Array Multipliers

#### **ADVANTAGES OF VLSI:**

- Size: incorporated circuits need aid a great part smaller—both transistors

- **Speed**: signs could make switched the middle of rationale 0 and rationale 1 a great part snappier inside a chip over they could the middle of chips

A Peer Revieved Open Access International Journal

www.ijiemr.org

• **control consumption:** rationale operations inside a chip likewise detract considerably lesquerella energy.

#### **RTL Schematic**

#### TECHNOLOGY SCHEMATIC

#### **RESULT**

#### **CONCLUSION**

We need exhibited An associated part timing model recognizing consistent indicator proliferation clinched alongside combinational circuits, which gives a straightforward lifestyle with acquire enough exact evaluate about proliferation postponements crosswise over diverse ways over a DFG. Those exact estimate of proliferation delay hence got might be used to settle on additional effective retiming choice with have lesquerella pipeline In heads. We have shown, here, that in the event of grid filters it might make conceivable on accomplish the same inspecting rate (without two-slow transformation) without expanding those clock recurrence Furthermore register complexity, which brings about those diminishment about Vitality utilization

A Peer Revieved Open Access International Journal

www.ijiemr.org

for every test will almost half that of the channel retimed Toward two-slow conversion. We bring exhibited adaptable Furthermore effective retiming from claiming fir filters the place we attain decrease for incredulous way utilizing lesquerella pipeline registers compared with accepted particular case. We need additionally demonstrated that the utilization for retiming for blending for node-splitting and node-merging, can conceivably decrease the testing period Toward About 50% without two-slow conversion in the event of essential multiply-add recursive structure. In the event that for both the fir Also IIR filters the retiming done consolidation with node-splitting Furthermore hub blending offers almost 50%-60% diminishment for basic way with a minor region overhead.

#### REFERENCES

- [1] (2009). Those universal engineering Roadmap for Semiconductors [Online]. Available: http://public. Itrs. Net/.

- [2] b. Shim, What's more, the lion's share of Corps parts don't stay in their starting work areas once their comm. Sridhara. Also Shanbhag, "Reliable low-power advanced indicator preparing by means of diminished precision redundancy," **IEEE** Trans. Exceptionally huge scale Integr. (VLSI) Syst., vol. 12, no. 5, pp. 497-510, May 2004.

- [3] b. Shim What's more n. R. Shanbhag, "Energy-efficient soft-error tolerant advanced sign processing," IEEE Trans. Really expansive scale Integr. (VLSI) Syst., vol. 14, no. 4, pp. 336–348, apr. 2006.

- [4] r. Support Furthermore n. R. Shanbhag, "Energy-efficient sign transforming by means of algorithmic noise-tolerance," to Proc. IEEE Int. Symp. Low energy electron. Des., aug. 1999, pp. 30–35.

- [5] v. Gupta, d. Mohapatra, An. Raghunathan, Furthermore k. Roy, "Low-power advanced indicator preparing utilizing estimated adders," IEEE Trans. Comput. Included des. Integr. Circuits Syst., vol. 32, no. 1, pp. 124–137, jan. 2013.

- [6] Y. Liu, t. Zhang, and k. K. Parhi, "Computation lapse examination clinched alongside advanced sign preparing frameworks for overscaled supply voltage," IEEE Trans. Exact extensive scale Integr. (VLSI) Syst., vol. 18, no. 4, pp. 517–526, apr. 2010.

- [7] j. N. Chen, j. H. Hu, What's more s. Y. Li, "Low control advanced sign transforming plan through stochastic rationale protection," for Proc. IEEE Int. Symp. Circuits Syst., might 2012, pp. 3077–3080.

A Peer Revieved Open Access International Journal

www.ijiemr.org

- [8] j. N. Chen What's more j. H. Hu, "Energy-efficient advanced sign transforming by means of voltageoverscaling-based deposit amount system," IEEE Trans. Altogether substantial scale Integr. (VLSI) Syst., vol. 21, no. 7, pp. 1322– 1332, Jul. 2013.

- [9] p. N. Whatmough, encountered with urban decay because of deindustrialization, innovation developed, government lodgin. Das, d. M. Bull, Also i. Darwazeh, "Circuit-level timing lapse tolerance to low-power DSP filters Also transforms," IEEE Trans. Really substantial scale Integr. (VLSI) Syst., vol. 21, no. 6, pp. 12–18, feb. 2012.

- [10] g. Karakonstantis, d. Mohapatra, and k. Roy, "Logic What's more memory outline In light of unequal lapse insurance for voltage-scalable, strong What's more versatile DSP systems," j. Indicator procedure. Syst., vol. 68, no. 3, pp. 415–431, 2012.

- [11] Y. Pu, j. P. De Gyvez, H. Corporaal, Also Y. Ha, "An ultimo low energy/frame multi-standard JPEG co-processor for 65-nm CMOS with sub/near edge energy supply," IEEE j. Robust state Circuits, vol. 45, no. 3, pp. 668–680, deface. 2010.

- [12] H. Fuketa, k. Hirairi, t. Yasufuku, m. Takamiya, m. Nomura, H. Shinohara, et al., "12. 7-times vitality proficiency increment for 16-bit basic unit Toward control supply voltage (VDD) scaling from 1. 2V. Will 310mV enabled Toward contention-less flip-flops (CLFF) Furthermore divided VDD between flip-flops Also combinational logics," Proc. ISLPED. over Fukuoka, Japan, aug. 2011, pp. 163– 168.

- [13] Y. C's. Lim, "Single-precision multiplier for decreased out multifaceted nature for sign transforming applications," IEEE Trans. Comput., vol. 41, no. 10, pp. 1333–1336, oct. 1992.

- [14] m. J. Schulte Furthermore e. E. Swartzlander, "Truncated duplication for revision constant," for Proc. Workshop VLSI sign procedure., vol. 6. 1993, pp. 388–396.

- [15] s. S. Kidambi, f. El-Guibaly, What's more a. Antoniou, "Area-efficient multipliers for advanced sign transforming applications," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 43, no. 2, pp. 90–95, feb. 1996.