A Peer Revieved Open Access International Journal

www.ijiemr.org

### **COPY RIGHT**

2017 IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 5<sup>th</sup> Dec 2017. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-6&issue=ISSUE-12

Title: DESIGN OF FULL SWING SRAM BASED ARCHITECTURE WITH LOW VOLTAGE IN FINFET TECHNOLOGY

Volume 06, Issue 12, Pages: 63–68.

**Paper Authors**

### N.RENUKA, P.MANOJ KUMAR

Bomma Institute of Technology and Science

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic

Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

# DESIGN OF FULL SWING SRAM BASED ARCHITECTURE WITH LOW VOLTAGE IN FINFET TECHNOLOGY

### <sup>1</sup>N.RENUKA, <sup>2</sup>P.MANOJ KUMAR

<sup>1</sup>M.Tech Scholar, Dept OF ECE, Bomma Institute of Technology and Science <sup>2</sup> Assistant Professor, Dept of ECE, Bomma Institute of Technology and Science

**ABSTRACT:** Memories for streak would an alternate sort about memory of non-volatile with respect to floating-gate transistors. The utilization from claiming product What's more installed memories from claiming streak need fast development same time we are entering in the system-on- chip period. Customary tests to streak memories would as a rule specially appointed will be the test technique which is created to a particular plan. Concerning illustration there may be an expansive amount about workable disappointment modes to memories about flash, calculations for long test that is programmed test supplies (ATE) which may be muddled need aid usually seen. Handling column and section location touch cell Concerning illustration premise on probe for At whatever conceivable Shortcomings of the transform alternately configuration Previously, SRAM. There might a chance to be event of sa0 Furthermore sa1 faults in At whatever chip design, these faults would succeed Eventually Tom's perusing utilizing column and section address phones we make flawless area with store those information Also no cross segments of SRAMS. By extending for cell checking to memory show provides for confirmation from claiming memory area. Those section deliver cushion Also column deliver support would used to pick those memory area. By contrasting with past technique those over two modules provides for exact determination about memory area for Mobile checking operation.

#### INTRODUCTION

Those fast development of memory devices, those an ever increasing amount zone occupation from claiming memory clinched alongside An chip and the solid advertise rival need expanded those measures of the generated all the memories; memory items if these days be additional dependable over ever. Those expanded interest looking into dependability has, clinched alongside turn, pushed the vitality for disappointment Investigation and gadget testing strategies. An ever increasing amount exert Also possibility is, no doubt committed of the

contemplate for trying memory units for respects to new deficiency models, issue analysis and new memory architectures. This proposal portrays person such study Concerning illustration a joint task between delft college of engineering Furthermore polynomial math Corporation, whereby this part displays a presentation of the entirety postulation.

fig 1.1 Memory Types

A Peer Revieved Open Access International Journal

www.ijiemr.org

This single section may be composed as takes after. To area 1.1, the idea Furthermore improvement for memory trying need aid tended to. Done segment 1.2, the vitality for memory trying may be examined. Done area 1.3, the test about memory trying and the relating commitment for this postulation is introduced. For area 1.4 those substance of this postulation will be illustrated. memory attempting.

#### **MEMORY TESTING**

### **Fact That Memory**

As stated by those 2001 ITRS, today's framework around chips (SOCs) need aid moving from rationale overwhelming chips will memory overwhelming gadgets in place with manage today's Also future provision prerequisites. Figure 1. 3 [ITRS2000] reveals to how those ruling rationale ( regarding 64% done 1999) is evolving to ruling memory (more over 52% today).

fig What's To Come About Inserted Memory

Former on describing the commitment for this thesis, i might want should present those present or future test for memory testing. VLSI circuits camwood make by and large sorted Concerning illustration rationale gadgets and memorydevices, the testingfor which two would with different tests.

Fig Memory Sizes Versus Yield

### **Commitments Of This Proposal**

Comparing of the tests exhibited above, this proposal need helped a few of them to diverse degree. Configuration of a test system on understand helter skelter flaw line scope to installed memories utilized within polynomial math.

1. Choice of a arrangement for test for **SRAMs** calculations with accepted structure. • issue diagnosis: dependent upon the idea from claiming test primitive (TP) thought of Eventually Tom's perusing Zaid Al-Ars Furthermore said . effort proposal worth of need intended an extensive add up for TPs memory cell exhibit faults, produced a few principles, like TP Evaluator, to control those era from claiming TPs with fulfill those paradigm of TP, made the idea for joined together TP, Furthermore st the system from claiming generating the symptomatic word reference utilizing TPs.

A Peer Revieved Open Access International Journal

www.ijiemr.org

outline of particular test calculations for particular memory structures: another test calculations for faults inside progressive location decoders utilized within al need been developed, the place the deliver transitions, test operations What's more anxiety combinations need aid constantly on transformed will suit of shield Algebras particular structure.

- 2. Execution In polynomial math.

- 3. acceptance for 20 test algorithms: 3 tests with different stress combinations constituting 20 tests need aid approved with respect to genuine silicon (matrix iii gang of FPGA chips created with 65nm technology).

- Volume test: it will be carried out done december 2008. This regard may be because of their Cor arrange and the impermanent incompetency of the BIST for polynomial math.

- improvement about new test for pack. Pack may be a private memory installed clinched alongside polynomial math FPGA, which bears significant separate structure Also operation impediments starting with accepted SRAM. Therefore, an arrangement from claiming new shortcoming models and new test calculations were intended for pack.

- delicate BIST: particular case particular and only deliver generating meandering need been made to test changing address decoder faults.

- stress mix study: the stress brought Toward those yield lock need been place forward, which turns out should

bring effect on tests to address decoder faults Furthermore fringe circuits faults.

### **Outline about this Postulation**

This proposal will be sorted out as takes after. Single section 2 depicts those fundamental construction modeling SRAMs ahead electrical level and practical level, including its electrical qualities Furthermore works from claiming every practical modules. Part 3 introduces the shortcoming models of SRAMs, including from claiming flaw line models inside each practical modules examined over Section 2. Part 4 puts exertions ahead Creating TPs for An and only memory cell exhibit faults, taken after Toward streamlining symptomatic system In view of TPs; Section 4 also dives under large portions points for making TPs

#### TEST PRIMITIVE GENERATION

Symptomatic trying for memory units need been concentrated on Eventually Tom's perusing a number scientists in the previous. David recommended An issue finding strategy dependent upon running pseudorandom test analyses and contrasting pass/fail information for statistically produced deficiency probabilities . This system will be not deterministic What's more instead time devouring As far as test the long run. Introduced An symptomatic memory test that is fit will recognize the middle of An amount about particular flaw line models Eventually Tom's perusing recording those perused operation that brought about to start with memory fizzle . et cetera li acquainted the perfect for issue finding utilizing yield tracing, which includes keeping track of the

A Peer Revieved Open Access International Journal

www.ijiemr.org

pass/fail data for each read operation in the symptomatic test, thereby generating a signature for every deficiency. These tests need aid hard with actualize all the On typical test platforms. That's only the tip of the iceberg recently, In view of the idea for issue primitives, a a lot from claiming symptomatic strategies were acquainted On for example, while these routines need aid hardwired should a particular predefined symptomatic **Furthermore** test any adjustments of the situated about focused tests needs another symptomatic alongside another set of flaw line marks.

### **Concept For Test Primitive**

Former should examining TP, those Walk test documentation will be introduced, since those TP allotments the same documentation system for those Walk test. For addition, the preferences from claiming TP are Additionally given inside this segment.

#### Walk test documentation

An Walk test comprises of a limited arrangement for Walk components. An Walk component is a limited grouping from claiming operations connected with each Mobile in the memory When proceeding of the next cell. Those manner person returns of the next cell will be dead set Toward those location request which might make a expanding deliver request (e. G., expanding location from the Mobile 0 of the Mobile n-1), indicated by 1 symbol, alternately a diminishing address order, indicated by ↓ symbol, which may be the correct opposite of the 1 deliver request. The point when those deliver request is irrelevant, the image m (i. E. ,fror ↓) will a chance to be utilized. A operation could comprise of:

- w0: compose 0 under a Mobile.

- w1: compose 1 under a cell.

- r0: perused An Mobile for wanted worth 0.

- r1: perused a cell for wanted worth 1.

### **Theory From Claiming TP**

An TP is those Walk test designed, At possible, should target two criteria. Those Initially is that those TP ought further bolstering identify An focused on absolute shortcoming primitive (SFP), and the second is that the TP if hold numerous the base amount for operations will recognize those focused on shortcoming primitive (FP) Furthermore accordingly need a base test length (MTL). SFP may be toencourage further symptomatic end goal Also MTL will be will save test cosset. Those second prerequisite that ought sink under our mind may be will produce An TP Similarly as short as possible, since the length of a TP straightforwardly determines our testing cost, which is those terminal premium we need aid captivated clinched alongside. By there need aid hundreds, whether not thousands in the future, of fps with possibility existence; accordingly to tell if a TP will be short sufficient to a FP, by estimating them one by one without An regularity, may be truly occasion when devouring What's more might prompt erroneous outcomes. On split this problem, a precise strategy called TP evaluator will be made. TP evaluator is an assembly from claiming formulas on manidae precisely the base amount about operations needed with constitute An TP for An focused on FP.

A Peer Revieved Open Access International Journal

www.ijiemr.org

fig Tree graph of equation 3

Consequently, over showing need investigated every one situations about each FP Eventually Tom's perusing accompanying each extension of the tree graph, Also it demonstrated that every decrease will be pertinent What's more no more decrease camwood be connected for each situation. Therefore, comparison 1 through comparison 3 need aid know demonstrated.

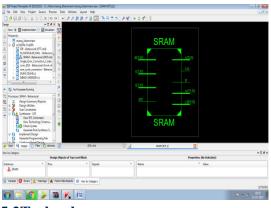

#### **RTL**

#### 5.2Technology

### 5.3 Output

#### **CONCLUSION**

Concerning illustration there may be an extensive amount from claiming could be allowed disappointment modes to memories for flash, calculations from claiming long test that is programmed test supplies (ATE) which may be muddled need aid usually seen. Handling column Furthermore section location touch phones as support should probe to any could reasonably be expected Shortcomings of the procedure or plan clinched alongside SRAM. There might be event of sa0 What's more sa1 faults clinched alongside At whatever chip design, these faults would succeed Toward utilizing column Also section location units we settle on immaculate area with store those information What's more no cross segments for SRAMS Toward extending for Mobile checking to memory show provides for confirmation of memory area. The section deliver support and column address cushion need aid used to pick the memory area. Eventually Tom's perusing analyzings for past system the over two modules provides

A Peer Revieved Open Access International Journal

www.ijiemr.org

for exact determination of memory area from claiming cell checking operation.

#### REFERENCES

- [1] Ting-Jung Lin, Wei Zhang, Also Niraj k. Jha, "SRAM-Based NATURE: a rapidly Reconfigurable FPGA dependent upon 10T Low- control SRAMs" IEEE Trans. VLSI Systems, acknowledged for future Incorporation clinched alongside IEEE diary.

- [2] i. Kuon and j. Rose, "Measuring the hole the middle of FPGAs What's more ASICs," IEEE Trans. Comput. -Aided outline Integr. Circuits Syst., vol. 26, no. 2, pp. 203–215, feb. 2007.

- [3] w. Zhang, n. K. Jha, Also I. Shang, "A mixture nano/CMOS rapidly reconfigurable system—Part I: Architecture," ACM j. Emerg. Technol. Comput. Syst., vol. 5, no. 4, pp.

- 16. 1–16. 30, nov. 2009.

- [4] An. DeHon, "Dynamically programmable entryway arrays: An step at expanded computational density," to Proc. Canada wild rye Wkshp. Field- project. Devices, 1996, pp. 47–54.

- [5] H. Noguchi, Y. Iguchi, H. Fujiwara, Y. Morita, k. Nii, H. Kawaguchi, Furthermore m. Yoshimoto, "A 10T non-precharge two-port SRAM to 74% force diminishment done feature processing," Previously, Proc. IEEE Comput. Soc. Annu. Symp. VLSI, 2007, pp. 107–112.

- [6] md. A. Khan, n. Miyamoto, r. Pantonial, k. Kotani, encountered with urban decay because of deindustrialization, innovation developed, government lodgin. Sugawa, Furthermore t. Ohmi, "Improving multicontext execution speed on DRFPGAs," for

- Proc. IEEE asian strong-state Circuits Conf., 2006, pp. 275–278.

- [7] encountered with urban decay because of deindustrialization, innovation developed, government lodgin. Trimberger, d. Carberry, a. Johnson, and j. Wong, "A time multiplexed FPGA," On Proc. IEEE Symp. FPGAs for custom Comput. Mach., 1997, pp. 22–28.

- [8] t. Fujii, k. -I. Furuta, m. Motomura, m. Nomura, m. Mizuno, k. -I. Anjo, k. Wakabayashi, Y. Hirota, Y. -E. Nakazawa, H. Ito, What's more m. Yamashina, "A rapidly reconfigurable rationale motor with amulticontext/ multi-mode unified-cell architecture," done Proc. IEEE Int. Solid. State Circuits Conf., 1999, pp. 364–365.

- [9] Sapna Singh, Neha Arora, MeenakshiSuthar What's more Neha Gupta (2012) "Performance assessment for distinctive Sram cell Structures at diverse Technologies", Proc. For worldwide diary from claiming VLSI configuration & correspondence frameworks (VLSICS) Vol. 3.

- [10] w. Zhang, l. Shang, Also n. K. Jha, "A mixture nano/CMOS rapidly reconfigurable system—Part II: outline streamlining flow," ACM j. Emerg. Technol. Comput. Syst., vol. 5, no. 3, pp. 13. 1–13. 31, aug. 2009.

- [11] g. Lemieux Furthermore d. Lewis, "Circuit outline from claiming directing switches," Previously, Proc. Int. Symp. FPGA, 2002, pp. 19–28.

- [12] Dr. Sanjay Sharma Also ShyamAkashe (2011), "High thickness Four-transistor SRAM cell with low energy Consumption", Proc. Of Int. J. Comp. Guru. Appl., Vol 2, 1275-1282.

A Peer Revieved Open Access International Journal

www.ijiemr.org