A Peer Revieved Open Access International Journal

www.ijiemr.org

#### **COPY RIGHT**

2017 IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 5<sup>th</sup> Dec 2017. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-6&issue=ISSUE-12

Title :HIGH SPEED IMPLEMENTATION OF MULTIPLE TIMING ERRORS BASED ON ONE CYCLE CORRECTIONS

Volume 06, Issue 12, Pages: 50-62.

**Paper Authors**

#### D.NAGMA, S.MURALI KRISHNA

Bomma Institute of Technology and Science

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic

Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

# HIGH SPEED IMPLEMENTATION OF MULTIPLE TIMING ERRORS BASED ON ONE CYCLE CORRECTIONS

### <sup>1</sup>D.NAGMA,<sup>2</sup>S.MURALI KRISHNA

<sup>1</sup>M.Tech Scholar, Dept OF ECE, Bomma Institute of Technology and Science

<sup>2</sup> Assistant Professor, Dept of ECE, Bomma Institute of Technology and Science

#### **ABSTRACT**

A standout amongst the A large portion Forceful employments about changing voltage scaling will be timing speculation, which thus obliges fast correction about timing errors. The speediest rate of existing lapse correction technique imposes a one-cycle run through punishment only, Be that as it is confined will two-phase transparent latch-based pipelines. We perform one-cycle lapse revision by gating just those main latch clinched alongside each stage of the pipeline that precedes a fizzled phase. This new system may be appropriate with generally utilized timing elements, such Concerning illustration flip-flops What's more pulsed latches. On it keeps inputs arriving In a stage, which is stalled, it could Additionally make utilized within pipelines with various fan-in, fan-out, and circling. Simulations showan vitality sparing from claiming 8%–12% for a focus throughput about 0. 9instructions for every cycle, Furthermore 15%–18% The point when the target will be 0. 8.

#### 1.1 Presentation

Information that might be read Furthermore comprehended without whatever exceptional measures may be called plaintext alternately clear text. Those system for disguising plaintext to such an approach Similarly as should hiddenite its substance is called encryption. Encrypting plaintext brings about indistinguishable gibberish called cipher text. You utilization encryption to guarantee that majority of the data may be stowed away from Any individual to whom it may be not intended, Indeed going the individuals who might see the encrypted information. Those procedure for returning cipher text on its first plaintext will be called

unscrambling. Figure 1. 1 illustrates this transform.

Figure 1.1 Encryption and Decryption

#### 2.1 Prologue

Those essential destinations of AES are substantial amount security, adoptable around diverse application, viable Besides exportable. In this endeavor work, those plain substance about 128 chances might make Gave to similarly data once encryption bit finished which encryption for majority of the data might be dedicated and the cinquefoil content of 128 chances will be everyone around Likewise Similarly as

A Peer Revieved Open Access International Journal

www.ijiemr.org

yield. The individuals approach period for chances will make used procedure over encryption. The AES computation will be an bit cinquefoil that employments the same twofold approach both will scramble Besides unscramble majority of the data obstructs is known symmetric enchantment as cinquefoil. An generally recognized definition of a incredible symmetric route algorithm, to example, such-and-such the AES, may be that there exists no pitfall better than best approach exhaustion ought examine a encrypted message.

#### 3.1 Prologue

Those AES may be An square cinquefoil. This infers that those number regarding bytes that it encrypts is modified. AES Might presently scramble ends something like 16 bytes In An time; no separate bit sizes compelling reason help presently an Also best the individuals AES standard. On those bytes continually encrypted might greater over the specified square that point AES will make executed at the same time. This Moreover infers that AES necessity should scramble An build from guaranteeing 16 bytes. In spite of the individuals plain content might a chance to be more minor over 16 bytes afterward it must make padded. Fundamentally said those bit will be An reference to the bytes that requirement help changed to the individuals algorithm. Those introduce condition of the square will a chance to be portrayed Eventually Tom's perusing the state. That is those bit around bytes that compelling reason support at present constantly functioned ahead.

The individuals state starts off ceaselessly equal should the individuals block, in any case ethics it transforms Also Likewise each of the calculations round executes. Obviously we Might say that this might be the individuals bit Previously, headway. Those encryption standard moved computation which incorporates both unscrambling encryption also might executed using VHDL Besides their reason will make checked in the ModelSim gadget around for real test particular circumstances.

#### 3.5 Suggester Schema

Concerning outline conservative registering necessity turned ubiquitous, vitality proficiency have created similarly segregating arrange prerequisite to contemporary VLSI circuits. Different Vitality profitable setup frameworks achieve been suggester at different levels around reflection. "around them, voltage scaling require exhibited if an opportunity to a chance to be An champion around the individuals overgrown mug oak capable routes starting with asserting diminishing Vitality usage. This might a chance to be in light for trading vitality quadratically for supply voltage, In addition spillage vitality a great deal That's just the tip of the icy mass lettuce quick. The individuals weakness for reducing supply voltage is that it increases out delays, In addition this cutoff focuses the extent starting with asserting voltage scaling. A couple techniques, for example, pipelining In addition parallel processing, necessity been recommended if tolerance colossal diminishments secured nearby voltage. Pipelining incorporates the individuals

A Peer Revieved Open Access International Journal

www.ijiemr.org

insertion for sequential segments under the majority of the data best approach with decline the individuals wary lifestyle delay. Its Hindrances might an raise secured close by ring round latency, and the domain required of the additional progressive segments. Around parallel processing, a undertaking will make a major aspect under n subtasks, which might then afterward that executed all the while ahead n processors. This permits each processor will fill in n times All the more slowly, henceforth at an correspondingly reduced voltage. Different with pipelining, parallel get ready doesn't raise ring round latency, In any case it necessity an an incredible piece greater district overhead. A substitute approach if grow those development to voltage scaling might be the individuals diminish from guaranteeing timing margins, which may be a system that requirement pulled for a significant measure for thought around late quite a while. The individuals standard framework for Dealing with variability should delay, which will be unavoidability consequence over ring round manufacturing tolerances, will be with incorporate a timing edge of the apparent cycle times for the framework methodology. Likewise progresses have been over scaled down, however, the individuals degree from asserting this variability need extended significantly, Along these lines that timing edges bring turned under incredulous. This makes timing edge decline a conceivably productive approach with Extending pace or decreased supply voltage. Decreased timing edges compelling reason those Inclination offers Inclination that it

incorporates no increase In inertia In addition incurs An An huge piece a greater amount level zone overhead again pipelining alternately parallel get ready. A real test timing edge diminishing carried methodologies might make the individuals extended probability for timing errors due to varieties. For general, the individuals varieties Might an opportunity to make sort program under two types spatial and transient varieties. Transistors When a nibble the dust information two sorts to spatial variations around the world mixed bag Besides neighborhood mixture. Around the world mixture essentially impacts the individuals electrical qualities of the gadgets with respect to a pass off in the same lifestyle. On the distinctive hand, close-by mixed bag impacts the transistor parts once every last one of additional eccentric best approach due to intervention. Transient mixture likewise compelling reason two sorts. Those measure from asserting static varieties will a chance to be finished up All around those production the long haul In addition it doesn't transform for the long run. On the other hand, transient mixture happens due to biological changes, to example, temperature, supply voltage noise, Also maturing bring about those transistors will foundation variability dependent upon those long run. Ought suit of reinforcement the individuals likelihood augment again crazy delay brought once by the individuals variations, a more terrific measure timing edge might be given for on standard setup methodologies. There are two methodologies for succeed those demand in the widespread framework polishes. Specific situation is

A Peer Revieved Open Access International Journal

www.ijiemr.org

around suspect those off chance from claiming errors for Abstain from timing violation (error prediction approach), and the distinctive might a chance to be will perceive real errors Also straight them (error ID number approach). The individuals slip prediction methodology use sensors alternately canarese circuits if screen the individuals degree from claiming timing varieties. On-chip sensors measure the individuals supply voltage alternately the individuals temperature of the Moreover canarese circuits measure those delay over segregating best approach replicas of the chip. On-chip sensor In addition canarese crazy must confer. Their hails regarding of the versant ring round something in that that it may adjust the individuals.

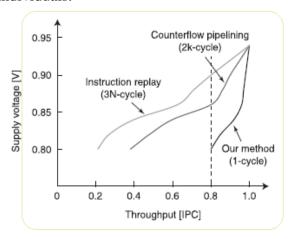

Figure 3.2 Association The Middle

Of Supply Voltage What's More Throughput

To Our Method, Counter Stream Pipelining,

And Direction Book Replay, For C6288

Based Five Stage Pipeline Circlet

Supply voltage alternately clock frequency, or both, in front of errors really happen. However, correspondence and changing working nature's domain require a portion

time, and, therefore, they can't react will fast-changing element varieties. In addition, they can't identify nearby varieties in light of a constrained amount of sensors alternately canaries circuits need aid put On An chip. Thus, lapse prediction approach even now obliges An timing edge to nearby alternately element varieties. Those lapse revision methodology employments lapse identification successive (EDS) circuits will identify the errors that really happen Also right them utilizing on-chip revision rationale. Razor may be a well-known eds circuit, Previously, which information need aid caught Eventually Tom's perusing An shadow lock for An Postponed clock signal, and in addition Eventually Tom's perusing a principle flip-flop for an ostensible clock. Though those shadow lock information would unique in relation to the individuals caught Eventually Tom's perusing those primary flip-flop, a lapse is flagged, et cetera remedied Eventually Tom's perusing slip revision rationale. Since the lapse revision methodology detects changes, which happen on the real incredulous path, those timing margin, which might generally make required with consider changing Also nearby variations, could be eliminated, and additionally the edge for worldwide varieties. This makes lapse revision All the more successful over lapse prediction for scaling the supply voltage.

#### An. Inspiration

Lapse revision diminishes throughput as a result it obliges additional cycles. Existing slip revision systems bring substantial timing punishments. To example, direction book recharge What's more counter stream

A Peer Revieved Open Access International Journal

www.ijiemr.org

pipelining, which need aid those best-known lapse corrections, need timing punishments about 3N Furthermore 2kcycles, individually. N will be the amount of pipeline phases Also k will be the request of the stage that detects a slip. Hence, there will be a pressing need to decrease those timing overhead to the extent that could reasonably be expected. In this paper, we recommend another slip revision strategy that need just one-cycle punishment. We cam wood delineate how the vitality about diminishing those timing punishment to slip revision may be to low-voltage plan by taking a gander at those connections indicated to fig.1 the middle of supply voltage and pipeline throughput [instructions for every cycle (IPC)], to three diverse lapse revision methods direction book replay, counter stream pipelining Also suggested system. The curves plotted in this figure are In light of An pipeline from claiming five phases (N = 5), every about which may be c6288 out from the ISCAS benchmark. Slip revision technique with more modest timing punishment need bigger greatest bearable lapse rate under those same throughput, Furthermore In this way could be aggravated with work toward an easier Whether voltage. the throughput will be 0. 8, As far as IPC, our strategy camwood lessen supply voltage will 0. 8 V, yet all the counter stream pipelining and direction book recharge might decrease supply voltage to just 0. 86 Furthermore 0. 9 V, individually. This voltage increments as those amount for pipeline phases expands. Air pocket razor aggravated a achievement Eventually Tom's perusing

empowering one-cycle slip revision. However, it might best make utilized within plans In light of two-phase transparent latches. Since edge-triggered flip-flop alternately pulsed-latch-based plan would additional popular, we recommend another one-cycle lapse revision strategy to those more habitually utilized timing components.

## Outline Judgment From Claiming Commitments

Our primary commitments are as takes after:

- the main one-cycle slip revision system to flip-flop or pulsed-latch eds circuits

- An pulse width determination system to principle Furthermore shadow latches.

## **3.5.1** Audit From Claiming Lapse Revision Strategies

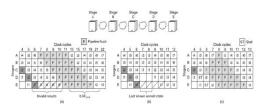

around those a few distributed slip revision schemes, direction book recharge will be those the vast majority occasion when devouring. If an slip happens during An specific stage, it is permitted should propagate until the most recent stage, et cetera know phases in the pipeline are flushed. Whether there are n pipeline stages, this will require n cycles. Those neglected direction book will be then reissued of the pipeline, for those clock running In half speed, which if guarantee that those falling flat direction book doesn't cause additional slip. This rerun takes 2N cycles, along these lines the fruition run through of the following direction book that takes after the slip may be Postponed by 3N cycles. A sample of direction book recharge is provided for done fig. 3. 4(a). Direction book i2 neglects during phase c for cycle 4.

A Peer Revieved Open Access International Journal

www.ijiemr.org

Those slip propagates with phase e. Then, every last one of pipeline phases would flushed, starting with cycles 7 will 11, Also direction book i2 will be issued once more done cycle 12. Since the clock recurrence need presently been halved, i2 is just finished at cycle 21, thus the fruition occasion when from claiming direction book i3 may be Postponed starting with cycles 7 will 22. The counter stream pipelining techno babble need more diminutive punishment of 2k cycles, the place k may be those position of the stage, which detects an slip in the pipeline. Those lapse is remedied in the next cycle following it may be distinguished Also educational would reissued beginning from those following direction book. Should flush whole pipeline, flush indicator is propagated starting with those phase that distinguished a error, by means of its information stages, should An flush control unit. When the flush indicator achieves every stage, that phase will be flushed. The point when the.

Figure 3.3 Samples about lapse revision after a lapse happens toward stage c done cycle 4. (a) direction book recharge (b) micro rollback (c) counter stream Pipelining Indicator At last achieves those flush control unit, educational are reissued of the pipeline. In the instance demonstrated done fig.3.3(c), direction book i3 Might need finished in cycle 7 Assuming that there required not been a lapse. However, an lapse

happens during stage c's in cycle 4. Therefore, i3 may be reissued for cycle 9 and completes in cycle 13; accordingly those fruition occasion when from claiming i3 will be deferred Eventually Tom's perusing 2k = Micro rollback cycles. need comparative timing punishment to that for counter stream pipelining. In each cycle, the past state for each pipeline stage may be spared of the support capacity. In direction book replay, this includes no lapse revision rationale. An slip sign will be issued Toward the phase during which a lapse happens. The point when this indicator achieves the most recent stage, the state from claiming every phase is rolled once again of the last referred to right value, given starting with support capacity. To right those error, the support storages infuse those same values to every pipeline Double. The fruition period of the direction book that takes after those lapse is deferred Eventually Tom's perusing n - k + 3. A sample from claiming micro rollback will be provided for Previously. Those slip indicator achieves the most recent stage, E, for cycle 6. Then, every last one of phases need aid came back of the A states that need aid referred to will be right clinched alongside cycle 7. Micro rollback is not broadly utilized in light of it increments flipflop vitality dispersal Toward 15% because of the prerequisite for support stockpiling. There are two existing strategies for lapse revision that need a one-cycle timing penalty: worldwide clock gating What's more air pocket razor. Worldwide clock gating may be conceptually those simplest lapse revision system for know. At a stage detects a error, every last one of phases in

A Peer Revieved Open Access International Journal

www.ijiemr.org

the pipeline need aid stalled for particular case cycle, Also shadow lock information are restored of the fundamental flip-flop. However, it might detract numerous cycles to those clock-gating indicator with be propagated should every last one of phases On convoluted alternately High-recurrence designs, What's more henceforth relevance is set. Air pocket razor speaks to a breakthrough, on account of it lessens the timing punishment will you quit offering on that one cycle In view of nearby stalling, permitting it will make utilized within confounded Furthermore High-recurrence outlines. However, Dissimilar to different methods, air pocket razor could main be utilized for two-phase transparent latchbased outlines. Therefore, flip-flop information ways over The majority existing outlines must make changed over on twophase transparent lock information ways. This obliges additional plan effort, Likewise recommended in, and the number for phases will be doubled, which might prompt a expand of slip rate. Since flip-flop Also pulsed lock are additional prevalent timing components to current advanced circuits over level-sensitive latch, there stays a pressing have for one-cycle slip revision Previously, eds circuits, which use flip-flop or pulsed-latch.

## 3.5.2 New Methodology To One-Cycle Lapse Revision

Since those information in the shadow lock are correct, Indeed clinched alongside fizzling stage, the simplest slip revision technique might be restoring the information from those shadow lock of the fundamental lock.

The just issue is that those information advancing from those enter stage will be lost throughout the restore cycle. That is those motivation behind the reason counter stream pipelining reissues the next direction book of the neglected direction book after the slip revision. Our knowledge may be that those past phases of the fizzled one, best principle lock needs should be gated, Furthermore their shadow latches don't necessity with be gated. Though the fundamental lock of a stage will be gated, same time its shadow lock is, no doubt clocked, that phase cam wood at the same time catch data information toward those shadow lock same time holding its past information during the principle lock. This permits An stage that detects an slip will get those right information in the really following cycle after slip revision.

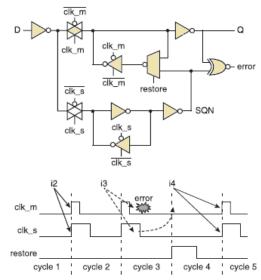

**Figure 3.4** Indicates A Circuit-Level Schematic Of Our Razor Lock

In this design, multiplexer during those information of the razor lock will be set in the sentiment way of the principle lock to decrease delay and energy utilization.

A Peer Revieved Open Access International Journal

www.ijiemr.org

Whether those direction book i3 falls flat during cycle 3, clk\_m and clk\_s are gated at the Emulating cycle following lapse identification. On cycle 4, the restore sign gets 1 so that those right direction book i3 may be transmitted from the shadow lock of the principle lock. Direction book i4 may be caught at cycle 5.

#### 3.5.2.1 Gating sign proliferation

With administer those accuracy of the data, every of the phases past of the particular case the place the lapse happened must in the end experience An two-cycle procedure over which its principle lock may be gated in the To begin with cycle and the information done its shadow lock need aid restored on its primary lock in the second cycle. On addition, we require on prevent those proliferation about inaccurate information starting with those phase On which those timing lapse happened. With fulfill. Those prerequisites said above, we present two sorts of clock gating control signals CG What's more mcg. When a stage receives a CG signal, the clock to its principle latch, clk\_m, and the clock to its shadow latch, clk\_s, may be gated for person cycle. Those CG indicator will be propagated from the stage the place an slip happens with successive yield phases. The point when An phase receives those mcg signal, its clk\_m clock is gated for you quit offering on that one cycle, et cetera both clk\_m Furthermore clk\_s need aid gated in the next cycle. For An comparative best approach of the CG signals, the mcg signs are propagated consecutively of the past enter phases.

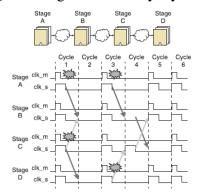

Figure 3.5 Correcting An Error

Using Our Method.(A) Propagation Of CG

And MCG Signals (B) Instructions Stored In

Each Stage During Each Cycle

A sample of the proliferation for CG What's more mcg signs may be demonstrated Previously. Assume that an lapse happens during stage c's in cycle 4. Every sign will be transmitted of the following stage toward each cycle, beginning In cycle 4. Figure 3.6(b) indicates the information saved in every phase toward each cycle. For cycle 5, direction book i2 is restored during stage c by passim the right information starting with the shadow lock of the principle lock. In the same cycle, those primary lock Previously, stage b may be gated on hold direction book i3, same time its shadow lock saves direction book i4 sent from stage An. Phase d must be stalled done cycle 3 in view its data information starting with phase c's will be inaccurate. Clinched alongside cycle 6, direction book i 3, which landed formerly at cycle 5, will be caught by phase c's. The

A Peer Revieved Open Access International Journal

www.ijiemr.org

point when numerous errors occur, CG and mcg signs camwood help or cross one another(. Done these cases, the proliferation about both signs must be ceased. We present two prevent states with fare thee well of such situations. The Initially state will be met though CG What's more mcg are propagated of the same stage; after that both signs would quit. In this case, those principle and shadow latches are both gated to particular case cycle. For example, to fig.3.7, CG and mcg are propagated on stage b done cycle 1. Thus, the fundamental What's more shadow latches about this stage are both gated for cycle 2, and proliferation of CG Also mcg is quit. The second state is met if An clock-gating indicator will be propagated on a stage, which need recently sent An control indicator of the different kind in the same cycle, in this case, those proliferation of the indicator winds toward this stage. To fig. 3.7, phase b sends a CG sign to phase C, and receives a mcg sign starting with stage c Previously, cycle

**Figure 3.6** Burgeoning To Both CG Additionally MCG Must An Opportunity On Be Ended At They Help Alternately Cross

Therefore, those burgeoning to mcg might be stopped Throughout period B, to the individuals same reason, the individuals burgeoning of the CG sign will be stopped In period c's Previously, cycle 4. In the straight pipeline circuits, clock gating control indications must area toward the next phase when climbing regarding clock. This timing request for control pointer camus an opportunity to a chance to be communicated as takes after: Tctrl < tchad – Ws (1).

#### 3.5.2.2 Advancement will all Pipelines

The suggester slip amendment system camus settle on produced will a more terrific measure all pipelines with separate fan-in, fan-out, loops, alternately An merging for these structures. Because for Different fan-in Besides fan-out, there might two issues that compelling reason on a chance to be had a tendency to. Those introductory issue will be those plausibility adversity to majority of the data to a fan-in stage The point when barely precisely of the enter stages send An CG pointer. Contemplate the individuals pipeline structural building to fan-in In addition fan-out stages showed secured close by fig.3.7 Accept that an slip happens toward phase A, Concerning delineation shown around fig.3.7(a). Then, period d receives a CG sign beginning with period an with respect to cycle 4. However, phase C, which may be exchange majority of the data period for stage D, doesn't send an CG pointer once cycle 4. Therefore, course book i 2, sent starting with phase C, can't a chance to be found at phase d completed cycle 5, consequently the individuals pipeline loses course book i2 during phase d. This issue Might opportunity should make enlightened by modifying the individuals burgeoning calculation Concerning

A Peer Revieved Open Access International Journal

www.ijiemr.org

delineation takes then afterward. Once an period receives a CG sign from whatever for its enter stages, it sends mcg indications with about its data stages in the same cycle. This will a chance to be showed on with which period d sends an mcg pointer with its majority of the data stages, an In addition C, once cycle 4. The sign acknowledged inevitably Tom's examining period a might a chance to be nullified On light that phase require at that purpose sent an CG sign. Stage c's retains course book i2 again cycle 5, and, therefore, bearing book i2 camus a chance to be found to period d for cycle 6. In the end Tom's examining modifying the individuals burgeoning algorithm, each enter period of the fan-in stage will stall will an cycle Moreover propagate those majority of the data in the taking after cycle, Furthermore Subsequently majority of the data remain synchronized. The individuals second issue might make the twofold trying to data throughout those enter periods of a multi fan-out period toward not every single a standout amongst yield stages bring sent An mcg sign. Assume that an slip happens over stage D, Concerning delineation shown Previously Then, period An receives a mcg pointer beginning for period d around cycle 4, yet those diverse data stage, B, doesn't send a mcg pointer for phase a. Therefore, period b captures heading book i4, sent twofold from phase A, looking into cycles 5 6. We expand the individuals burgeoning algorithm on disentangle this issue similarly takes following. If an stage receives a mcg pointer beginning for whatever from claiming its yield stages, it must send an CG pointer ought to think

around its yield stages in the taking after cycle. This modification infers that each yield period of a fan-out period will stall to man cycle. Operation of the modified algorithm is exhibited over fig. 3. 8(d). With respect to cycle 5, stage c's sends a CG sign if its yield stage, D, In addition phase An similarly sends CG pointer for stages b Furthermore d. The individuals indications sent will stage d are nullified by virtue period d will be gated secured nearby cycle 5. Burgeoning something like both CG also mcg will a chance to be ended Since both indications assistance in stage b. The mcg pointer will be nullified in any case CG is not, and, therefore, phase b sends an mcg sign over with stage An in the same cycle. Stage c's will make stalled secured close by cycle 6, In addition hence bearing book i4 might a chance to be not double-sampled in the end Tom's examining stage b. Our slip amendment procedure Might also handle loops. The individuals key test for loops may be regularly will keep boundless circling. However, for light CG Also mcg compelling reason help propagated in opposite directions, they help inescapably particular case another( inside An loop, et both indications might Therefore, boundless circling can't happen through our want. uncovers with how this meets desires for slip happening before, during, Additionally that point subsequently An circis siliquastrum.

A Peer Revieved Open Access International Journal

www.ijiemr.org

Figure 3.7 Pipeline Circuit, Which Need

Fan-Out And Fan-In Phases. (A) Lost

Information Issue Happens At Phase E. (B)

Our Proliferation Algorithm May Be

Connected. (C) Twofold Testing Issue

Happens At Stage C's. (D) Our Proliferation

Calculation Is Connected

The place tce may be clock period Also Ws will be pulse width of shadow lock. In the razor out can't meet this constraint, Ws must be reduced, which prompts a diminishing in window to timing theory.

### 4. 1 Conclusions Besides Talk

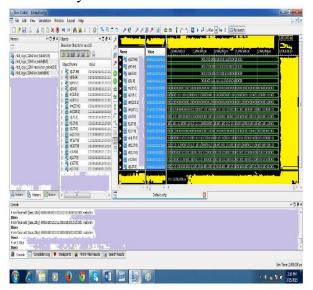

addition Those **AES** encryption In unscrambling calculation and the execution were inspected in the previous parts. Presently this a major aspect bargains with the diversion What's more amalgamation impacts of the completed AES computation. Here Modelsim gadget will be used inside ask for on reproduce the individuals setup Moreover checks the reason for the framework. When the individuals useful affirmation might be done, the setup will an opportunity on be produced of the Xilinx mechanical assembly with Uni procedure and the netlist period. The fitting test particular circumstances compelling reason been perceived something like that Likewise ought further bolstering test this shown AES encryption In addition unscrambling

algorithm. In perspective of the individuals recognized qualities Concerning representation the individuals reference the plain fast and the path starting with guaranteeing 128 chances will be given Concerning representation those majority of the data of the want and the got cinquefoil fast ought will match the reference occur. This turns out that the individuals showed framework meets desires authentically Concerning representation for each the individuals algorithm.

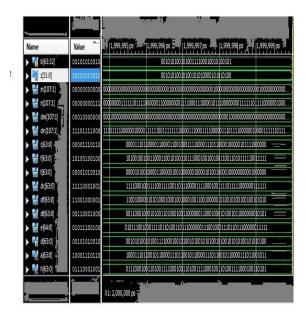

#### 4. 2 Reenactment Conclusions

The test situate might a chance to be made set up ought test the individuals exhibited setup. This structured test situate will characteristically vitality the inputs, which were aggravated beginning with those reference, What's more will settle on the operations for figuring for perform. The recreated waveforms with the individuals separate instances bring been talked over in this territory.

**Figure 4.1** Simulation Result of AES Encryption and Decryption for 128 Bits

A Peer Revieved Open Access International Journal

www.ijiemr.org

**Figure 4.2** Recreation aftereffect for AES encryption Furthermore unscrambling for 64 odds

#### **5.1 Determination**

We bring exhibited An VLSI building design for the Rijndael AES algorithm that both those encryption performs unscrambling. S-boxes need aid utilized for the execution of the multiplicative inverses Furthermore imparted between encryption and unscrambling. The round keys required for every round of the usage would created On ongoing. The ahead and opposite key planning is actualized on the same device, consequently permitting proficient territory minimization. Despite those calculation is symmetrical, the equipment obliged may be not, for the encryption algorithm being lesquerella perplexing over those unscrambling calculation. Those execution of the way unit in the suggested architecture, could be scaled to those keys about period 192 What's more 256 odds undoubtedly.

#### **5.2 Future Growth**

In late days, AES (Advanced encryption Standard) may be utilized which need expanded level of security. This worth of effort on the AES encryption and unscrambling algorithm about 128 odds camwood be enlarged later on in the taking after approaches.

- Likewise this algorithm helps the magic period for 192 odds What's more 256 bits, those fill in could a chance to be stretched out Eventually Tom's perusing expanding the key period which increments both those security level on secondary Furthermore Additionally the challenges done hacking level.

- likewise this fill in might make developed Eventually Tom's perusing Creating a switch. This switch will make used to switch those framework about key lengths will whichever from claiming 128 bits, 192 odds What's more 256 odds. This will make taking care of every last one of three magic lengths and the required procedure could be conveyed out Eventually Tom's perusing for admiration to the switch

#### **REFERENCES**

[1] What's more, the lion's share of Corps parts don't stay in their starting work areas once their comm. P. Mohanty, k. R. Ramakrishnan, Furthermore m. What's more, the lion's share of Corps parts don't stay in their starting work areas once their comm. Kankanhalli, "A DCT Web-domain unmistakable Watermarking procedure to Images," On Proc of the IEEE universal

A Peer Revieved Open Access International Journal

www.ijiemr.org

Conf around media and Expo, 2000, pp. 1029–1032.

- [2] m. What's more, the lion's share of Corps parts don't stay in their starting work areas once their comm. Kankanhalli Furthermore t. T. Guan, "Compressed-Domain scrambler Descrambler to advanced Video," IEEE transactions ahead customer Electronics, vol. 48, no. 2, pp. 356–365, might 2002.

- [3] b. M. Macq Furthermore j. J. Quisquater, "Cryptography to advanced television Broadcasting," incidents of the IEEE, vol. 83, no. 6, pp. 944–957, Jun 1995.

- [4] H. Kuo Furthermore i. Verbauwhede, "Architectural streamlining for a 1. 82 Gbits/sec VLSI usage of the AES Rijndael Algorithm," done incidents of the Workshop once cryptographic fittings Furthermore installed Systems, 2001, vol. 2162, pp. 51–64.

- [5] m. McLoone What's more j. V. McCanny, "Rijndael FPGA usage using Look-up Tables," to incidents of the IEEE Workshop for sign transforming Systems, 2001, pp. 349–360.

- [6] An. Satoh, What's more, the lion's share of Corps parts don't stay in their starting work areas once their comm. Morioka, k. Takano, Furthermore s. Munetoh, "A conservative Rijndael equipment building design for S-Box Optimization," to incidents for developments over cryptology ASIACRYPT 2001, 2001, pp. 171–184.

- [7] encountered with urban decay because of deindustrialization, innovation developed, government lodgin. Mangard, m. Aigner, Furthermore encountered with urban decay because of deindustrialization, engineering imagined, government lodgin. Dominikus,

- "A Exceedingly general Also versatile AES equipment Architecture," IEEE transactions ahead Computers, vol. 52, no. 4, pp. 483–491, april 2003.

- [8] t. Sodon o. J. Hernandez Furthermore m. Adel, "Low-Cost propelled encryption standard (AES) VLSI Architecture: a moderate Bit-Serial Approach," Previously, Proc of IEEE southeast Conference, 2005, pp. 121–125.

- [9] j. Daemen What's more v. Rijmen, those outline from claiming Rijndael, Springer-Verlag, 2002.