A Peer Revieved Open Access International Journal

www.ijiemr.org

### **COPY RIGHT**

2021IJIEMR.Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 5th Oct 2021. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-10&issue=ISSUE-10

DOI: 10.48047/IJIEMR/V10/I10/29

Title DESIGN AND IMPLEMENTATION OF HIGH EFFICIENT PPA BASED HANCARLSON ADDER

Volume 10, Issue 10, Pages: 174-178

**Paper Authors**

**AKULA JAHNAVI, G.POORNA KRISHNA**

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic

Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

# DESIGN AND IMPLEMENTATION OF HIGH EFFICIENT PPA BASED HANCARLSON ADDER

<sup>1</sup>AKULA JAHNAVI, <sup>2</sup>G.POORNA KRISHNA

<sup>1</sup>M.Tech Scholar, Dept of ECE, St. Mary's Womens Engineering College, Budampadu Post, Guntur, Andhra Pradesh 522017

<sup>2</sup>Associate Professor & HOD, Dept of ECE, St. Mary's Womens Engineering College, Budampadu Post, Guntur, Andhra Pradesh 522017

**ABSTRACT:** In this paper design of and implementation of high efficient PPA based hancarlson adder is implemented. Basically, adders plays very important role in DSP and micro processor applications. Input 'a' and input 'b' are assigned in particular order. Next pre-processing stage will be performed. In pre processing stages both propagator and generator signals are generated. Propagator and generator unit generate the signals of propagator and generator. Black cell and grey cells are generated in Carry generation unit. Addition is performed using XOR operation. At last output is saved in post processing stage. From results it can observe the RTL schematic, Technology schematic of proposed system. Hence the binary adder gives effective results.

**KEY WORDS:** Binary adder, Pre Processing Stage, Adder tree, VLSI, Post Processing stage, Black cells and Grey Cells.

#### I. INTRODUCTION

Fastest technologies are developed in present days. In present days, reduction of device size, fast operation and low power consumption are required. The designing of low power VLSI system has more demand in mobile communication. Due to the device designed by designer with high speed, low power consumption and small silicon area, the device is available with low power. ALU (Arithmetic logic unit) and FU (Floating point unit) are the main parts in computations [1]. Logical computations are addition, subtraction, multiplication, division and logical operations are AND, OR, INV and comparison which are processed by Arithmetic logic unit (ALU). Data path has an important role in digital signal processors and microprocessors because of some characteristics such as power consumption, speed of operation and die-area. The above characteristics depend upon the data path efficiency. Data pathcontains complex operations are

subtraction, addition, division and multiplication [2].

The main important factor is data path performance which is affected by efficient hardware units of complex computations. In the data path addition is the important executed operation, addition operation contains binary adder to add given numbers. In complex computations such as decimal operations, multiplication and division, adders has important task [3]. To get data path efficiently, the implementation of binary adder should be efficient.

In central processing unit (CPU) crucial element is ALU (Arithmetic logic unit). An adder has important function in ALU and an adder performs not only addition but also performs multiplication, subtraction and decrement/increment. In ALU and general processors to get better performance, efficient adder is needed. From 1950s, for hardware implementation of VLSI arithmetic circuits, research started on

A Peer Revieved Open Access International Journal

www.ijiemr.org

efficient adder implementation. In control systems and digital signal processing main operation is the addition.

The properties of system or processor like accuracy and speed depends upon the performance of adder. To execute the addition of numbers, adder is used which is a digital circuit. Different processors and computers contains ALU in which adder is used. To reduce different parameters, different designs have been implemented based on parallel and serial structures. Four elementary operations are performed in binary addition.

The adders can be represented in many forms like BCD (binary coded decimal) and excess-3 code; binary numbers are used in adders to perform the operation. Negative numbers are represented by ones complement or two's complement, for this adder is modified as adder-subtractor. More logic is required to represent signed numbers including basic adder [4-5].

execute the addition To operation, computers contain Arithmetic Logic unit (ALU) in which adders are mostly used. Graphics processing unit (GPU) and central processing unit uses the adders to decrease the redundancy for the graphics applications. In the adders first type is half adder it include two inputs and it provides two outputs such as carry and sum. Next one is full adders which include two inputs with carry input and it provides two outputs such as carry and sum. For single bit, both half adder and full adder is utilized. The full adder is coupled in parallel form to perform the multi bit addition operation.

#### II. RELATED WORK

Half adder is used in digital electronics for the purpose of addition of two binary numbers. Full adder is used for the addition of 3-bit input sequence. If input sequence contain more number of bits, half adder and full adder does not satisfy the addition

operation. These drawbacks are overcome by Ripple carry adder. For the addition of Nbit numbers, this type of logic circuit is used in digital operations.

By using multiple full adders, logical circuit can be created for the purpose of addition of N-bit numbers. In each full adder, one of the sources of info is Cin which is taken care of from Cout of past adder. This kind of adderis known as Ripple-Carry Adder. Since each convey bit waves to next full adder. May be half adder is put in the principal full adder since first full adder contains Cin=0.

The Ripple convey adder circuit chart is straightforward, it creates quick plan time. In any case, the activity of wave convey adder is moderate on the grounds that each full adder ought to be hanging tight for convey bit which is originated from past full adder. By utilizing full adder circuit, door postponement can be determined. Three degrees of rationale are required in full adder. N full adders are required in n-bit Ripple convey adder.

BCD (binary coded decimal) adder is a digital circuit in which two BCD numbers are added in parallel and carry out and sum bits are generated. The result of sum will not be in BCD form when addition of two BCD digits is done.

The BCD result is correct in first example and BCD result is not correct in second example. BCD digits are represented from 0 to 9, to represent BCD numbers, four bits are required. But by using four bits, 16 values are represented. In the BCD digits extra six values are ignored because BCD

A Peer Revieved Open Access International Journal

www.ijiemr.org

digits are represented from 0 to 9. After addition, the result will not in BCD form when the result is greater than 9. It contains corrections to be done to obtain correct BCD results.

#### III. PROPOSED SYSTEM

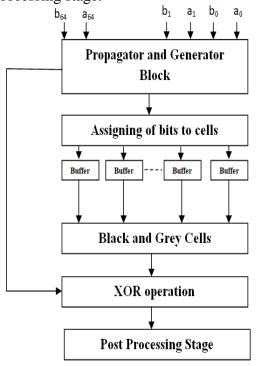

The below figure (1) shows the structure of proposed system. Input 'a' and input 'b' are assigned in particular order. Next preprocessing stage will be performed. In pre processing stages both propagator and generator signals are generated. Propagator and generator unit generate the signals of propagator and generator. Black cell and grey cells are generated in Carry generation unit. Addition is performed using XOR operation. At last output is saved in post processing stage.

Fig. 1: BLOCK DIAGRAM OF PROPOSED SYSTEM

Propagate signals and generate signals are manipulated to pair of each inputs A and B.

In hancarlson adder carry generation stage the calculation is performed based on the bits and carries obtained. The entire operation is performed in the form of parallel. Generate and propagate signals are obtained from the intermediate signals.

#### 1. Pre-Processing Stage:

In this stage, propagate signals and generate signals are manipulated to pair of each inputs A and B. Propagate signal and generate signal are represented as

Pi = Ai XOR Bi Gi = Ai AND Bi

### 2. Carry Generation Network:

In carry generation stage the calculation is performed based on the bits and carries obtained. The entire operation is performed in the form of parallel. Generate and propagate signals are obtained from the intermediate signals. The below equations shows the propagate and generate signals:

$$Pi:j = Pi:k AND Pk-1:j$$

Gi:j = Gi:k OR (Pi:k AND Gk-1:j)

#### 3. Post Processing Stage:

In post processing stage the calculation is performed based on the input bits. From post processing stage sum and carry is generated. The below equations shows the sum and carry equations:

$$Si = Pi XOR Ci-1$$

In applications of high speed circuits, very useful adder is PPA based hancarlson adder.

A Peer Revieved Open Access International Journal

www.ijiemr.org

PPA based hancarlson adder is designed based on the power and area.

Structure delay= log<sub>2</sub> n

Number of computation nodes= [(n)]  $(log_2 n)-n+$

### IV. RESULTS

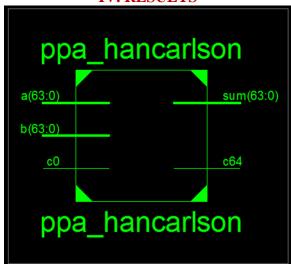

Fig. 2: RTL SCHEMATIC

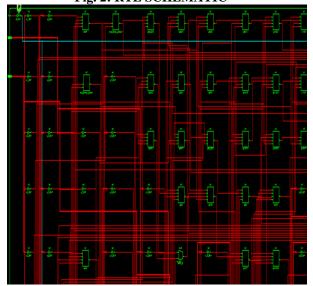

Fig. 3: TECHNOLOGY SCHEMATIC

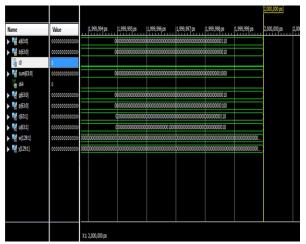

Fig. 4: OUTPUT WAVEFORM

#### V. CONCLUSION

Hence in this paper design of and implementation of high efficient PPA based hancarlson adder was implemented. Propagator and generator unit generate the signals of propagator and generator. From results it can observe the RTL schematic, Technology schematic of configurable parallel adder In future, Arithmetic based sub systems will consists of Shannon based adder cell, high performance low power full adder, high speed counter using GDI technique and Vedic multiplier designs. They can be used in the implementation of finite impulse response filter design for DSP which are advantageous for low power applications. ASIC design for low power digital filter with low latency and power gating can be carried out.

### VI. REFERENCES

- [1] U Penchalaiah, Siva Kumar VG, "Design of High-Speed and Energy-Efficient Parallel Prefix Kogge Stone Adder", 2018 IEEE Conference.

- [2] Aung Myo San , Alexey N. Yakunin , "Reducing the Hardware Complexity of a Parallel Prefix Adder", 978-1-5386-4340-2/18/\$31.00©2018 IEEE.

A Peer Revieved Open Access International Journal

www.ijiemr.org

- [3] Bhavani Koyada,1 N. Meghana,2 Md. Omair Jaleel3 and Praneet Raj Jeripotula4, "A Comparative Study on Adders", 978-1-5090-4442-9/17/\$31.00 c 2017 IEEE.

- [4] S.Daphni, K.S. Vijula Grace, "A REVIEW ANALYSIS OF PARALLEL PREFIX ADDERS FOR BETTER PERFORMNCE IN VLSI APPLICATIONS", 978-1-5090-6480-9/17/\$31.00©2017 IEEE.

- [5] Shaheen Khan , Zainul Abdin Jaffery, "Parallel-prefix modulo adders: A Review", 978-1-5386-4318-1/17/\$31.00 ©2017 IEEE.

- [6] Er. Aradhana Raju, Richi Patnaik, Ritto Kurian Babu, Purabi Mahato , "Parallel Prefix Adders- A Comparative Study For Fastest Response", 2016 IEEE Conference.

- [7] Sudheer Kumar Yezerla, B Rajendra Naik, "Design and Estimation of delay, power and area for Parallel prefix adders", 978-1-4799-2291-8/14/\$31.00 ©2014 IEEE.

- [8] Dayu Wang1, Xiaoping Cui2, Xiaojing Wang, "Optimized design of Parallel Prefix Ling Adder", 978-1-4577-0321-8/11/\$26.00 ©2011 IEEE.

- [9] Tso-Bing Juang, Pramod Kumar Meher, Chung-Chun Kuan, "Area-Efficient Parallel-Prefix Ling Adders", 978-1-4244-7456-1/10/\$26.00 ©2010 IEEE.

- [10] M.Moghaddam, M. B. Ghaznavi-Ghoushchi,"A New Low-Power, Low-area, Parallel Prefix Sklansky Adder with Reduced Inter-Stage Connections Complexity", 2011 IEEE Conference.

- [11] Nagaraja Revanna, Earl E. Swartzlander, Jr., "Memristor Adder Design", 978-1-5386-7392-8/18/\$31.00 ©2003 IEEE.

- [12] Pavan Kumar.M.O.V #1, Kiran.M, "Design Of Optimal Fast Adder", 978-1-5386-7392-8/18/\$31.00 ©2002 IEEE.