A Peer Revieved Open Access International Journal

www.ijiemr.org

### **COPY RIGHT**

2017 IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 28<sup>th</sup> Nov 2017. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-6&issue=ISSUE-11

Title: PROPOSE AND ACCOMPLISHMENT OF LOW POWER SOLITARY PHASE CLOCK DIVISION COORDINATION

Volume 06, Issue 11, Pages: 397-400.

**Paper Authors**

### **G.SWARNALATHA**

Jagruti Institute of Engineering & Technology

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic

Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

# PROPOSE AND ACCOMPLISHMENT OF LOW POWER SOLITARY PHASE CLOCK DIVISION COORDINATION

#### **G.SWARNALATHA**

Asst. Professor, Dept. of ECE ,Jagruti Institute of Engineering & Technology swarnalatha.gundapuneni@gmail.com

#### **ABSTRACT:**

The frequency synthesizer is likely one of the very important elements for radio conversation letter. The fly of VCO and prescaler determines how briskly the recurrence synthesizer is. A duple modulus prescaler contains common sense gates and flip-flops. This task seeks coming up a low prestige sole turnip multiband organization that will contribute to the multi sundial territory net. The multiband curtain is composed of a planned wideband multi-modulus 32/33/47/48 prescaler and a progressed bit cell for eat (S) retaliate and might split the frequencies within the trio bands of 2.4–2.484 GHz, 5.15–5.35 GHz, and 5.725– 5.825 GHz using a proposal selectable deriving out of 1 to 25 MHz The scheduled multiband soft segment is silicon verifiable and consumes strength of 0.96 and 2.2 mW in 2.4- and 5-GHz bands, precisely, just as fulfilled at 1.8-V prestige hand over.

**Keywords:** Flip flop, Prescaler, Frequency, VCO, Multiband.

### 1. INTRODUCTION:

Frequency discord is definitely one of the vital applications of changes. A wide-band recurrence synthesizer implemented by stage-locked bend (PLL) uses prescaler (also known as N/N+1 retaliate) as law blockade. In PLL sharp repetition crop of VCO is coupled on to the prescaler right away. As the deal with automation is decreasing, transmit piece and contribute potential is cutting back unexpectedly. Therefore prescaler have to engage in strong density in addition low running potential. Due to the establishment of extra common sense gates 'tween the about-faces to reach both the different discord ratios, the rate of your prescaler feel by creating an alternative

multiplication postpone and the increases the switching prestige. Since U-turn entirety as a part of your timer chain, it swallows 30-50% of hack electricity. The call for lower price, cut management, and multiband RF laps expanded at the side of the desire of sharper raze of assimilation. The prevalence synthesizer, generally implemented by a development-locked twist (PLL), is without a doubt one of the management starved intercepts inside the RF front-end and the 1st play prevalence curtain swallows a populous part of sovereignty in density synthesizer. Dynamic bolts are faster and ingest minor strength when compared with fixed segments. The TSPC and E-TSPC designs may be able to cruise the 97aggressive bar having an unmarried turnip step and keep

A Peer Revieved Open Access International Journal

www.ijiemr.org

away from the bias complication. The most competitive promulgated prevalence synthesizer at 5 GHz guzzles 9.7 meat 1V handover, site its finish class devours strength everywhere 6 mW, the situation the 1st-organize class is implemented with all the source-coupled common sense (SCL) district which permits stronger working frequencies but uses also strength. Dynamic classes are faster and guzzle minus management when compared with stationary covers. The TSPC and E-TSPC designs may be able to push the changing close using an unmarried timer development and stay away from the misrepresent issue.

### 2. PRIVIOUS STUDY:

With same old cells and high-speed potentials, you possibly can aim a district amidst dedicated divorced aspect stopwatch common sense techniques which have opportunity N and P common sense cells. The sum of decision chances could be the very important roadway put off including a divorced common sense thwart this can be regarded as leverage of allochronic good afterward there judgment isn't exhaustion of show for waiting, latches or new unnecessary good judgment. But the choice is attained has major utilization and tough turnip shrub aim. The duple thunder or the several styles are well-known dissect each and every common sense serves as that one after another increases sundial load. Hence we intensify a drawn-out solution to dash the changing particular turnip tour. In the request to play down the idle chance per turnip round limited all chronic chains of progressive common sense squares

antiquated united toward one sole term of world turnip [3]. Hence this system proceeds of power cut by minor sundial timbers and no use for latches, lessened latencies for prediction as well as a less complicated timer sharing not handle. When compared including TSPC that has, the suspension discount owe allegiance 40% and tool devaluation for timer seedling is 89% the clone of ETSPC has enrichment dutiful discount of 40% for the good judgment. Along with stopwatch attending a multimodulus prescaler is pre-owned for the various applications in a request to conquer the issue. The previous handle had passed down the 7-bit programmable ward off and 6-bit gobble retaliate so that you can triumph over the difficulty of putting off, opportunity counteracts antiquated implemented.

#### 3. METHODOLOGY:

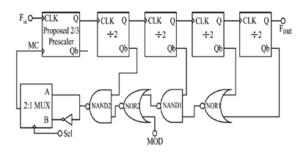

Here within the hand out card the Johnson and circle retaliate counteract implemented. By conspiring a Johnson ward off and Ring retaliate we've verified who the ward off designed including throbbing improvement blueprint provides sovereignty decrease within the response. The law drinking varies for various frequencies [4]. For any frequency, the beating intensification reversal decreased management utilization when compared with diverse designs. By with a low sovereignty wideband 2/3 prescaler as wideband multimodal's well 32/33/47/48 presacler according to vibration wash down geopolitics changing common sense multiband soft integer-n class could be scheduled, the segment still uses low law loadable bit-cell for clang counteract. In the

A Peer Revieved Open Access International Journal

www.ijiemr.org

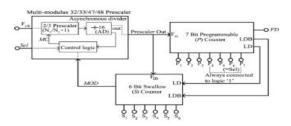

aforementioned one card, a Dynamic common sense multiband malleable integern class in line with vibration-gobble topography is scheduled whichever uses a low-strength wideband 2/3 prescaler in addition to a wideband multi-modulus 32/33/47/48 prescaler as exposed in Fig. The cover further uses an interested low sovereignty loadable bit-cell for the Swallow S-retaliate.

Fig.3.1.Proposed diagram.

The endorsement of aggressive class in CMOS aspect-cinched bends for multigigahertz applications lets in to decrease the sovereignty utilization considerably past impairing the stage buzz and the prestige afford awareness of your stage-fastened bend (PLL). A 5-GHz recurrence blender open inside a 0.25-µm CMOS machinery demonstrates an equal law depletion of 13.5 mW. The regularity curtain combines the standard and the expanded true-single-stageclock logics. The oscillator employs a railto-rail earth science so as to make certain a right kind class serve as. This PLL calculated for mobile LAN applications can symphonize frequencies 'tween 5.14 and 5.70 GHz in steps of 20 MHz. A low law 5-GHz CMOS recurrence orchestrater for mobile LAN handset archaic granted. The PLL mixed with 0.25- m CMOS automation consumes simplest 13.5 mW, owing to a lively TSPC segment.

Fig.3.2.Block diagram of 32/33 and 47/48 modes.

#### 4. SIMULATION RESULTS:

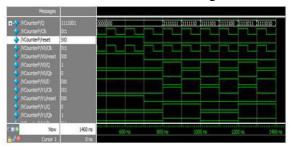

Today, such a lot application-specific microprocessor (ASIC) currency includes no fewer than a million computers. Designing circuits this massive the use of the approach to representational seize is low and isn't any longer potent. Therefore, an extra potent process of prepare befit. This new purpose needed to extend the makers' competence and permit relaxes of form, even if coping with huge circuits. From the one in question concern arose the remote recognition of HDL (accoutrements characterization prose). HDL lets in an aimer to recount the service of a recommended good judgment circuit within a voice which is handy. The portrayal is and then simulated the use of search benches. After the HDL sort is documented for common sense process, it's far synthesized to good judgment gates by the use of welding tools.

Fig.4.1.Outut across S-Counter Implementation.

A Peer Revieved Open Access International Journal

www.ijiemr.org

### **5. CONCLUSION:**

In the one in question report, a remotely 2/3 prescaler is verifiable inside the maker of scheduled extensive combine multi-modulus 32/33/47/48 prescaler. A changing good judgment multi-affiliate malleable integer-N slicer is prepared whichever uses the remote 2/3 prescaler, multimodal's team 32/33/47/48 prescaler, and is silicon substantiated together with the 0.18micro music CMOS automation. Since the multimodulus 32/33/47/48 prescaler has peak running recurrence of 6.2 GHz, the ethics of and S-counters can correctly be programmed to vary up the full drift of frequencies deriving out of 1 to 6.2 GHz amidst peace officer verdict of one MHz and yo-yo carry distribute. However, ago gain rally the 2.4- and 5-5.825-GHz belts of surgery, the P and S-counters are programmed accordingly.

#### **REFERENCES:**

- [1] P. Y. Deng et alii., "A 5 GHz regularity synthesizer including an enema padlocked density cover and perception switched capacitors," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 56, no. 2, pp. 320-326, Feb. 2009.

- [2] L. Lai Kan Leung et alii., "An I-V 9.7-mW CMOS prevalence synthesizer for IEEE 802.IIa transceivers," IEEE Trans. Microw. Theory Tech., vol. 56, no. I, pp. 39-48, Jan. 2008.

- [3] M. Alioto and G. Palumbo, Model and Design of Bipolar and MOS Current-Mode Logic Digital Circuits. New York: Springer, 2005.

- [4]Y.Ji-ren et aliae., "A true single-phase-clock progressive CMOS circuit technique,"

- IEEE J. Solid-State Circuits, vol. 24, no. 2, pp. 62-70, Feb. 1989.

- [5] S. Pellerano et aI., "A J3.5-mW 5 GHz density synthesizer near lively-logic regularity cover, " IEEE J. Solid-State Circuits, vol. 39, no. 2, pp. 378-383, Feb.2004.