A Peer Revieved Open Access International Journal

www.ijiemr.org

### **COPY RIGHT**

2017 IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 19<sup>th</sup> November 2017. Link:

http://www.ijiemr.org/downloads.php?vol=Volume-6&issue=ISSUE-10

**Title**: Multilevel Inverter in Photo Voltaic System With MPPT for Harmonic reduction Withless No of Switches.

Volume 06, Issue 10, Page No: 329 - 334.

### **Paper Authors**

- \* PALLA. NARENDRA, D. SUKLAJA.

- \* Dept of EEE, Annamacharya Institute of Technology and Sciences.

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

## MULTILEVEL INVERTER IN PHOTO VOLTAIC SYSTEM WITH MPPT FOR HARMONICREDUCTION WITHLESS NO OF SWITCHES

\*PALLA. NARENDRA, \*\*D. SUKLAJA

\*PG Scholar, Dept of EEE, Annamacharya Institute of Technology and Sciences.

\*\*Assistant professor, Dept of EEE, Annamacharya Institute of Technology and Sciences.

#### **ABSTRACT:**

This paper presents the modeling and simulation of 13-level cascaded hybrid multilevel inverter (MLI) for with less number of switches. MLI is one of the most efficient power converters which are especially suited for high power applications with reduced harmonics. MLI not only achieves high output power and is also used in renewable energy sources such as photovoltaic, wind and fuel cells. This paper mainly focuses on cascaded MLI with three unequal DC sources called asymmetric cascaded MLI which reduces the number of power switches. The sinusoidal pulse width modulation (SPWM) is improves the output voltage at lower modulation index for obtaining lower Total Harmonic Distortion (THD) level. The gating signal for the 13-level hybrid inverter using SPWM technique is generated. This proposed modulation technique results in reduced percentage of THD, but lower order harmonics are not eliminated. So a new technique called Selective Harmonic Elimination (SHE) is also implemented in order to reduce the lower order harmonics. The performance evaluation of the proposed pulse width modulation (PWM) inverter is verified using 13-level cascaded hybrid MLI with MATLAB / Simulink model.

**Keywords:** Multilevel Inverter (MLI), Sinusoidal Pulse Width Modulation (SPWM), Selective Harmonic Elimination (SHE), Total Harmonic Distortion (THD).

### 1. INTRODUCTION

The inverters are relied upon to give sinusoidal yields yet the viable inverters non-sinusoidal produce vield and subsequently contain harmonics. combine a close sinusoidal component and to lessen the harmonic distortion multilevel inverters have emerged. It is this creating innovation that has affected the battery packs in electric vehicles in light of the likelihood of high power rating without the utilization of transformer. Among the different multilevel structures that were introduced researchers, the cascaded multilevel inverter turns out to be much predominant in harmonic reduction.

Further, the low order harmonic contents which are available can be minimized by exchanging switching strategies. Selective Harmonic Elimination Pulse Width Modulation (SHEPWM) technique was developed for multilevel converters to eliminate lower order harmonics. The

trigonometric terms in the equations create multiple solutions thereby, making it complex to control the switching angle and hence reduce the lower order harmonics. The arithmetic solutions which are the switching angles of inverter suppress the lower order harmonics. Research was carried out to solve these equations by mathematical methods and evolutionary algorithms. Mathematical methods are derivative based and needs initial assumptions. Different topologies like diodeclamped inverter, capacitor-clamped, and cascaded multilevel inverter with separate DC sources were developed [1-5].

An optimal modulation technique [6] to reduce the switching losses was proposed, but this technique had more conduction losses due to high output currents and due to the series connection of several semiconductors. Despite the fact that different novel algorithms for Selective Harmonic Elimination were created [7-8], yet they slacked in the capacity to take out substantial

A Peer Revieved Open Access International Journal

www.ijiemr.org

number of low order harmonics. This lead to the advancements in selective harmonic elimination pulse width modulated technique based on the foraging behavior of a colony of ants [9]. This method has improved calculation, subordinate free operation, and achieves close optimal convergence. A formulation generalized for selective harmonic elimination pulse width modulation control suitable for high voltage, high power Voltage cascaded multilevel Source Converters (VSC) with both equivalent and non square with DC sources utilized as a part

In recent years multilevel inverter plays an important role and attracts more attention in conversion medium of power applications. It is simple in construction, better-quality in performance and produces lesser harmonics. Also it has lower switching high dv/dt rating and reduced switching stresses and harmonics. The three commercial topologies of multilevel voltage source inverters are (i) the Neutral Point Clamped (NPC) or diode clamped multilevel inverter (DCMLI), (ii) flying capacitor and multilevel inverter (FCMLI) cascaded H bridge (CHB) multilevel inverter. Unlike DCMLI and FCMLI the CMLI does not require voltage clamping diodes and voltage balancing capacitors. This paper focuses particularly on cascaded hybrid multilevel inverter [13-16] which requires independent DC sources i.e. for "n" number of DC sources the number of levels obtained will be (2n + 1).

In view of DC source, the CHB multilevel inverter is further divided into two topologies namely symmetric and asymmetric inverters. The values of all the voltage sources are equal in symmetric topology. In symmetric topology if the number of output voltage levels is increased, it results in rapid increase in number of switching devices. So in order to increase the number of output voltage levels with less number of switching devices the different value of DC sources are selected

which is named as asymmetric topology [17-18]. Among these two topologies, asymmetric cascaded MLI is explained in this paper and it requires three unequal DC sources to produce thirteen-level output. This new topology has been proposed to obtain 13-level output with minimum number of switches. In addition to that the THD are reduced and specified harmonics are eliminated using selective harmonic elimination pulse width modulation (SHE PWM) technique.

### MULTILEVEL INVERTER

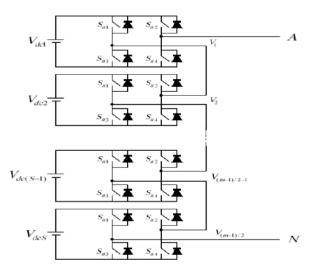

A single-phase structure of an m-level cascaded inverter is illustrated in Figure 5. Each separate dc source (SDCS) is connected to a single-phase full-bridge, or H-bridge, inverter. Each inverter level can generate three different voltage outputs, +Vdc, 0, and -Vdc by connecting the dc source to the ac output by different combinations of the four switches, S1, S2, S3, and S4. To obtain +Vdc, switches S1 and S4 are turned on, whereas -Vdc can be obtained by turning on switches S2 and S3.

By turning on S1 and S2 or S3 and S4, the output voltage is 0. The AC outputs of each different full-bridge inverter levels are connected in series such that the synthesized voltage waveform is the sum of the inverter outputs. The number of output phase voltage levels m in a cascade inverter is defined by m = 2s+1, where s is the number of separate dc sources. An example phase voltage waveform for an 11-level cascaded H-bridge inverter with 5 SDCSs and 5 full bridges is shown in Figure. The phase voltage VAM = VA1+ VA2+ VA3+ VA4+ VA5 For a steppedwaveformsuchasthe onedepictedinFigure withssteps, the Fourier Transform for this wavef ormfollows:

A Peer Revieved Open Access International Journal

www.ijiemr.org

Figure shows Single-phase structure of a m level multilevel cascaded H bridge inverter.

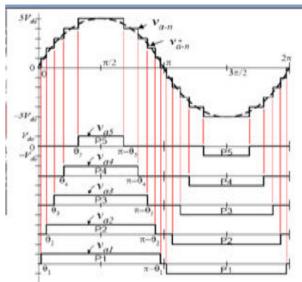

This figure shows the Output phase voltage waveform of an 11-level cascade inverter with 5 separate dc sources.

# PROPOSED SELECTIVE HARMONIC ELIMINATION (SHE) PWM TECHNIQUE

In SPWM it has several carrier signals keeping only one modulating signal. The carrier signals are triangular one and have same frequency and peak to peak amplitude so that the bands they occupy are contiguous i.e. one carrier signal will have a contact with other signal. The modulating signal is pure

sinusoidal and at every instant each carrier signal is compared with modulating signal. In each comparison if the modulating signal is greater than the carrier signal it gives one or otherwise zero. The results are added to give the voltage level, which is required at the output terminal of the inverter. SHE is commonly adopted in medium and high power inverter applications where the switching frequency is low enough to minimize the switching losses. effectiveness of this method is fully depends on switching angles. So, for determining the optimum switching angles several algorithms have been developed. Usually it is done using optimization techniques such as Newton Raphson method.

The digital implementation of SHE equations involves two steps are (i) The switching angles are too calculated through a set of nonlinear and transcendental equations. (ii) The determined switching angles are to be stored in look up table for real time applications. In this paper for finding the values of switching angles the Newton Raphson method has been implemented which has a set of solutions to reduce the lower order harmonics.

The main advantages of this SHE is to obtain lower order harmonics at the output side. If the inverter wants to supply AC power to an AC load with constant frequency a filter is usually installed in its output side. In this method when the lower order harmonics are eliminated the output will have only higher order harmonics and it should be attenuated by the filter. Hence the cut-off frequency will be increased which will results in filter size.

# PROPOSED SINGLE PHASE CASCADED MULTILEVEL INVERTER - ASYMMETRIC TOPOLOGY

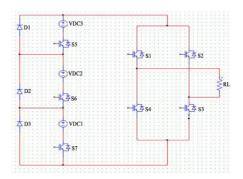

The new design of topology is required to form an asymmetric inverter as shown in Fig 3. The switching states and voltage levels of the proposed inverter are shown in Table 1.

A Peer Revieved Open Access International Journal

www.ijiemr.org

**Fig 3**: Proposed circuit for Cascaded 13-level Inverter-Asymmetric

Fig. Output voltage levels of 13-level inverter

### Switching states and voltage levels of a 13level inverter

| <b>S1</b> | <b>S2</b> | <b>S</b> 3 |   | <b>S4</b> | <b>S5</b> | <b>S6</b> | <b>S</b> 7     |

|-----------|-----------|------------|---|-----------|-----------|-----------|----------------|

| 1         | 0         | 1          | 0 | 0         | 0         | 1         | +Vd            |

| 1         | 0         | 1          | 0 | 0         | 1         | 1         | + <i>Vd</i> /6 |

| 1         | 0         | 1          | 0 | 0         | 1         | 1         | +Vd/3          |

| 1         | 0         | 1          | 0 | 1         | 0         | 0         | +3Vd/6         |

| 1         | 0         | 1          | 0 | 1         | 0         | 1         | +2Vd/3         |

| 1         | 0         | 1          | 0 | 1         | 1         | 1         | +4Vd/5         |

| 0         | 0         | 0          | 0 | 0         | 0         | 0         | 0              |

| 0         | 1         | 0          | 1 | 0         | 0         | 1         | - <u>Vd</u>    |

| 0         | 1         | 0          | 1 | 0         | 1         | 1         | -Vd/6          |

| 0         | 1         | 0          | 1 | 0         | 1         | 1         | -Vd/3          |

| 0         | 1         | 0          | 1 | 1         | 0         | 0         | -3Vd/6         |

| 0         | 1         | 0          | 1 | 1         | 0         | 1         | -2Vd/3         |

| 0         | 1         | 0          | 1 | 1         | 1         | 1         | -4Vd/5         |

## 5.SIMULATION RESULTS AND DISCUSSION

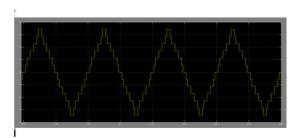

By using MATLAB/Simulink the proposed 13-level inverter is simulated by using Insulated Gate Bipolar Transistor (IGBT) switches. Here only 7 switches are used to produce 13-level output along with 3 feedback diodes. The staircase output voltage

and current waveform of 13-level inverter thus obtained is shown in Fig 5.

**Fig 5**: *Output voltage and current waveform.*

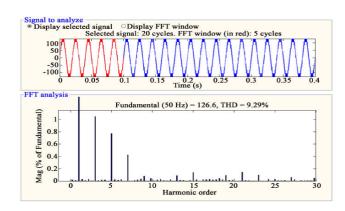

The staircase output and the FFT analysis for THD% is shown in Fig 6.

**Fig 6:** FFT analysis for 13-level inverter with R load.

From the obtained result the THD for R load is 9.29% at 1500 Hz frequency for 126.6 V. The simulation result that the odd harmonics of 3rd, 5th, 7th, and 9th harmonic levels are most dominant. Hence a new method of SHEPWM is suggested for minimizing such kind of odd harmonics.

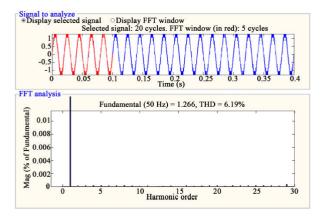

The FFT analysis of 13-level inverter with R load for Mi = 0.97 using SHE technique is shown in Fig 7. By using SHE technique the 3rd, 5th, 7th, and 9th harmonics are minimized by varying the modulation index from 0 to 1.

For the modulation index 0.85, the switching angles are 0.62, 23.10, 44.42, 54.37 and 63.57 the THD is 8.59%. If the modulation index is 0.97 the various switching angles are 4.82, 12.69, 23.32, 24.46, 37.27 and THD is around

A Peer Revieved Open Access International Journal

www.ijiemr.org

6.19% which highly satisfies the IEEE 519-1992 harmonic guidelines. Thus if the modulation index has been increased the % THD would be reduced.

FFT analysis of 13-level inverter with R load for Mi = 0.97 using SHE technique.

#### 6. CONCLUSION

The analysis of the modeling and simulation of 13-level cascaded hybrid multilevel inverter (MLI) for with less number of switches is implemented. The proposed topology of 13-level cascaded hybrid MLI is verified with the satisfied results of MATLAB/Simulink model. This topology is also simulated by using SHEPWM technique for minimizing the most dominant odd harmonics. The ratio (1:2:4) of the DC source voltage and the firing angle computation has performed to obtain a minimum THD value of the load voltage and current. Here the realization of the modulation index is also observed for maintaining the AC output voltage by varying the modulation index between  $0 \le m \le 1$ . From the above analysis by the comparison of output results, it is realized that the proposed model resulted lower THD level which could meet the IEEE 519-1992 standard.

### **REFERENCES**

[1] Rodriguez, J., Lai, J.-S. and Peng, F.Z. (2002) *Multilevel Inverters: A Survey of Topologies, Controls, and Applications*. IEEE

Transactions on Industrial Electronics, 49, 724-738.

- [2] Malinowski, M., Gopakumar, K., Rodriguez, J. and Perez, M.A. (2010) *A Survey on Cascaded Multilevel Inverters*. IEEE Transactions on Industrial Electronics, 57, 2197-2206.

- [3] M.Valan Rajkumar, P.S.Manoharan, Modeling and Simulation of Three-phase DCMLI using SVPWM for Photovoltaic System, Springer Lecture Notes in Electrical Engineering, under the volume titled "Power Electronics & Renewable Energy Systems", Volume 326, Chapter No 5, January 2015, Pages 39-45.

- [4] Fei, W., Du, X. and Wu, B. (2008) *A Generalized Half Wave Symmetry SHE-PWM Formulation for Multilevel Voltage Inverters*. IEEE Transactions on Industrial Electronics, 57, 3030-3038.

- [5] M.Valan Rajkumar, P.S.Manoharan, Harmonic Reduction of Fuzzy PI Controller based Three-Phase Seven-level DCMLI with SVPWM for Grid Connected Photovoltaic System, Journal International Review on Modeling and Simulations, Volume 6, No 3, June 2013, Pages 684-692.

- [6] Sundareswaran, K., Jayant, K. and Shanavas, T.N. (2007) *Inverter Harmonic Elimination through a Colony of Continuously Exploring Ants*. IEEE Transactions on Industrial Electronics, 54, 2558-2565.

- [7] Dahidah, M.S.A. and Agilities, V.G. (2008) Selective Harmonic Elimination PWM Control for Cascaded Multilevel Voltage Source Converters: A Generalized Formula. IEEE Transactions on Power Electronics, 23, 1620-1630.

- [8] M.Valan Rajkumar, P.S.Manoharan, FPGA Based Multilevel Cascaded Inverters with SVPWM Algorithm for Photovoltaic system, Elsevier Journal Solar Energy,

A Peer Revieved Open Access International Journal

www.ijiemr.org

Volume 87, Issue 1, January 2013, Pages 229-245.

- [9] P.Thirumurugan, P.S.Manoharan, M.Valan Rajkumar, *VLSI Based Space Vector Pulse Width Modulation Switching Control* in the proceedings of IEEE International Conference on Advanced Communication Control and Computing Technologies ICACCCT 2012 on August 2012, ISBN No. 978-1-4673-2045-0 (Print) (Page):366-370.

- [10] Fei, W.M., Ruan, X.B. and Wu, B. (2009) A Generalized Formulation of Quarter Wave Symmetry SHEPWM Problems for Multilevel Inverters. IEEE Transactions on Power Electronics, 24, 1758-1766.

- [11] M.Valan Rajkumar, P.S.Manoharan, Space Vector Pulse Width Modulation of Three-Phase DCMLI with Neuro-Fuzzy MPPT for Photovoltaic System, World Journal of Modelling and Simulation, Volume 10, No 3, August 2014, Pages 193-205.

- [12] Sirisukprasert, S., Lai, J.S. and Liu, T.-H. (2002) *Optimum Harmonic Reduction with a Wide Range of Modulation Indexes for Multilevel Converters*. IEEE Transactions on Industrial Electronics, 49, 875-881.

- [13] Rajkumar, M.V., Prakasam, P. and Manoharan, P.S. (2016) *Investigational Validation of PV Based DCDMLI Using Simplified SVM Algorithm Utilizing FPGA Tied with Independent Sources*. Circuits and Systems, 7, 3831-3848. http://dx.doi.org/10.4236/cs.2016.711320