A Peer Revieved Open Access International Journal

www.ijiemr.org

#### **COPY RIGHT**

2017 IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 17<sup>th</sup> Aug 2017. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-6&issue=ISSUE-7

Title: A THREE-PHASE MULTILEVEL INVERTER WITH NOVEL SCHEME OF REDUCED COMPONENTS FOR INDUSTRIAL APPLICATIONS

Volume 06, Issue 07, Pages: 131 - 138.

**Paper Authors**

INDU KUMARI, Mr. JADAPALLI SREEDHAR

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

A Peer Revieved Open Access International Journal

www.ijiemr.org

## A THREE-PHASE MULTILEVEL INVERTER WITH NOVEL SCHEME OF REDUCED COMPONENTS FOR INDUSTRIAL APPLICATIONS

<sup>1</sup>INDU KUMARI, <sup>2</sup>Mr. JADAPALLI SREEDHAR

<sup>1</sup>M-tech Student Scholar, Dept of E.E.E, Annamacharya Institute of Technology & Sciences.

Rangareddy (Dt), Telangana, India.

<sup>2</sup>HOD, Dept of Electrical & E.E.E, Annamacharya Institute of Technology & Sciences.

Rangareddy (Dt), Telangana, India.

Abstract-In this paper Three-Phase Cascaded Multilevel Inverter Based on a New Basic Unit with Reduced Number of Power Switches for grid connected system is proposed. Thus multilevel inverter topologies are becoming more popular. A multilevel inverter topology is discussed. The inverter consists of series connection of a number of basic units. Therefore, multilevel inverters had been introduced and are being developed now. With an increasing number of dc voltage sources in the input side, a sinusoidal like waveform can be generated at the output. As a result, the total harmonic distortion (THD) decreases, and the output waveform quality increases, which are the two main advantages of multilevel inverters. In addition, lower switching losses, lower voltage stress of dv/dt on switches, and better electromagnetic interference are the other most important advantages of multilevel inverters. These features are obtained by the comparison of the conventional cascaded multilevel inverters with the proposed cascaded topology. The ability of the proposed inverter to generate all voltage levels (even and odd) is reconfirmed by using the simulation results of a 15-level inverter and three phase 15-level inverter with grid connected system. The simulation results are presented by using Matlab/Simulink Model.

**Index Terms**—Basic unit, cascaded multilevel inverter, developed cascaded multilevel inverter, H-bridge, grid connected.

#### I. INTRODUCTION

Multilevel inverters have been under research and development for more than three decades have found successful and industrial applications. However, this is still a technology under development, many contributions and new commercial topologies have been reported in the last few years [1-2]. The aim of this dissertation is to group and review recent contributions, in order to establish the current state of the art and trends of the technology provide readers comprehensive and insightful review of where

multilevel converter technology stands and is heading [3]. This chapter first presents a brief overview of well-established multilevel inverters strongly oriented to their current state in industrial applications and then centers the discussion on the new multilevel inverters that have made their way into the industry [4-5]. Multilevel inverters have been attracting increasing interest recently the main reasons are; increased power ratings, improved harmonic performance, and reduced electromagnetic interference (EMI) emission that can be archived with multiple dc levels that are

A Peer Revieved Open Access International Journal

www.ijiemr.org

synthesis of the output voltage waveform. In particular multilevel inverters have abundant demand in applications such as medium voltage industrial drives, electric vehicles, and grid connected photovoltaic systems. The present work provides a solution to design an efficient multilevel topology which is suited for medium and high power applications [6-8].

The cascade inverter has drawn great interest due to the great demand of medium-voltage high-power inverters. The cascade inverter is also used in regenerative-type motor drive applications. Recently, some new topologies of multilevel inverters have emerged. This includes generalized multilevel inverters [9], mixed multilevel inverters, hybrid multilevel inverters [10] and soft-switched multilevel inverters [11]. These multilevel inverters can extend rated inverter voltage and power by increasing the number of voltage levels. They can also increase equivalent switching frequency without the increase of actual switching frequency, thus reducing ripple component of inverter output voltage and electromagnetic interference effects. As the multilevel converter is broadly applied in the industries because the demand to operate switching, power converters in high power application has the growth constantly. The capacity of multilevel converters to operate at high voltages of the AC waveforms has low distortion, high quality and high efficiency [12-13]. However, the multilevel converter topology has improved efficiency by using various controls to attain high efficiency and increase to save energy. In this paper, the topology proposed is three phase fifteen- level cascaded multilevel H bridge inverter for three phase grid connected

system. A fifteen level cascaded multilevel H bridge inverter to reduce the Total Harmonic Distortion (THD)of the inverter output voltages for three-phase grid connected system are presented.

#### II. PROPOSED TOPOLOGY

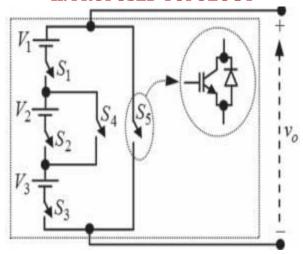

Fig. 1. Proposed basic unit.

TABLE I

Permitted Turn On and Off States for Switches in the Proposed Basic Unit

| atata |       | ν     |       |       |       |                   |

|-------|-------|-------|-------|-------|-------|-------------------|

| state | $S_1$ | $S_2$ | $S_3$ | $S_4$ | $S_5$ | $v_o$             |

| 1     | off   | off   | off   | off   | on    | 0                 |

| 2     | on    | off   | on    | on    | off   | $V_1 + V_3$       |

| 3     | on    | on    | on    | off   | off   | $V_1 + V_2 + V_3$ |

Fig. 1 shows the proposed basic unit. As shown in Fig. 1, the proposed basic unit is comprised of three dc voltage sources and five unidirectional power switches. In the proposed structure, power switches (S2, S4), (S1, S3, S4, S5), and (S1, S2, S3, S5) should not be simultaneously turned on to prevent the short circuit of dc voltage sources. The turn on and

A Peer Revieved Open Access International Journal

www.ijiemr.org

off states of the power switches for the proposed basic unit are shown in Table I, where the proposed basic unit is able to generate three different levels of 0, V1 + V3, and (V1 + V2 + V3) at the output. It is important to note that the basic unit is only able to generate positive levels at the output.

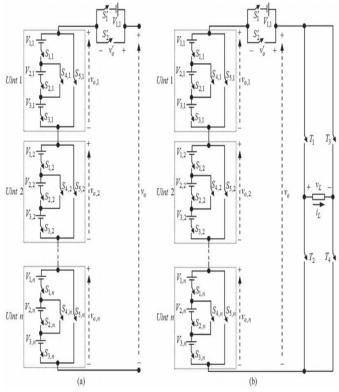

It is possible to connect n number of basic units in series. As this inverter is able to generate all voltage levels except V1, it is necessary to use an additional dc voltage source with the amplitude of V1 and two unidirectional switches that are connected in series with the proposed units. The proposed cascaded inverter that is able to generate all levels is shown in Fig. 2(a). In this inverter, power switches S'1 and S'2 and dc voltage source V1 have been used to produce the lowest output level. The amplitude of this dc voltage source is considered V1 = Vdc (equal to the minimum output level). The output voltage level of each unit is indicated by Vo, 1, Vo, 2, ... ., Vo, n, and V'o. The output voltage level vo of the proposed cascaded multilevel inverter is equal to

$$v_o(t) = v_{o,1}(t) + v_{o,2}(t) + \dots + v_{o,n}(t) + v'_o(t)$$

(1)

The generated output voltage levels of the proposed inverter are shown in Table II. As aforementioned and according to Table II, the proposed inverter that is shown in Fig. 2(a) is only able to generate positive levels at the output.

Fig. 2. Cascaded multilevel inverter. (a) Proposed topology. (b) Developed proposed topology.

## TABLE II Generated Output Voltage Levels Vo Based On the Off And On States of Power Switches

| $v_o$                                                       | Si  | S'2 | $S_{1,1}$ | S 2,1 | $S_{3,1}$ | S <sub>4,1</sub> | S <sub>5,1</sub> | S <sub>1,2</sub> | $S_{2,2}$ | S 3,2 | S 4,2 | $S_{5,2}$ |      | $S_{1,n}$ | $S_{2,n}$ | $S_{3,n}$ | $S_{4,n}$ | S 5,1 |

|-------------------------------------------------------------|-----|-----|-----------|-------|-----------|------------------|------------------|------------------|-----------|-------|-------|-----------|------|-----------|-----------|-----------|-----------|-------|

| 0                                                           | off | on  | off       | off   | off       | off              | on               | off              | off       | off   | off   | on        |      | off       | off       | off       | off       | on    |

| $V_{1}$                                                     | on  | off | off       | off   | off       | off              | on               | off              | off       | off   | off   | on        |      | off       | off       | off       | off       | on    |

| $V_{1,1} + V_{3,1}$                                         | off | on  | on        | off   | on        | on               | off              | off              | off       | off   | off   | on        |      | off       | off       | off       | off       | on    |

| $V_{1,1} + V_{2,1} + V_{3,1}$                               | off | on  | on        | on    | on        | off              | off              | off              | off       | off   | off   | on        |      | off       | off       | off       | off       | on    |

| V <sub>1,2</sub> +V <sub>3,2</sub>                          | off | on  | off       | off   | off       | off              | on               | on               | off       | on    | on    | off       | **** | off       | off       | off       | off       | on    |

| $V_{1,2} + V_{2,2} + V_{3,2}$                               | off | on  | off       | off   | off       | off              | on               | on               | on        | on    | off   | off       |      | off       | off       | off       | off       | on    |

| $V_{1,1} + V_{1,2} + V_{1,3} + V_{2,1} + V_{2,3}$           | off | on  | on        | on    | on        | off              | off              | on               | off       | on    | on    | off       | 5550 | off       | off       | off       | off       | on    |

| $V_{1,1} + V_{1,2} + V_{1,3} + V_{2,1} + V_{2,2} + V_{2,3}$ | off | on  | on        | on    | on        | off              | off              | on               | on        | on    | off   | off       | m    | off       | off       | off       | off       | on    |

| :                                                           | i   | :   | 1         | i     | :         | :                | :                | :                | :         | :     | :     | :         | :    | :         | i         | :         | :         | :     |

| $\sum_{j=1}^{n} (V_{1,j} + V_{2,j} + V_{3,j})$              | off | on  | on        | on    | on        | off              | off              | on               | on        | on    | off   | off       |      | off       | off       | off       | off       | on    |

| $1,1 + \sum_{i=1}^{n} (V_{1,j} + V_{2,j} + V_{3,j})$        | on  | off | on        | on    | on        | off              | off              | on               | on        | on    | off   | off       |      | off       | off       | off       | off       | on    |

A Peer Revieved Open Access International Journal

www.ijiemr.org

TABLE III

Proposed Algorithms and Their Related

Parameters

| Proposed algorithm                | Magnitude of dc voltage sources                                                                                          | N <sub>level</sub>     | $V_{o,\max}$                                | V <sub>block</sub>       |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------|---------------------------------------------|--------------------------|

| First proposed algorithm $(P_1)$  | $V_{1,j} = V_{2,j} = V_{3,j} = V_{dc}$<br>for $j = 1, 2, \dots, n$                                                       | 6n+3                   | $(3n+1)V_{dc}$                              | $(2\ln+6)V_{dc}$         |

| Second proposed algorithm $(P_2)$ | $V_{1,1} = V_{2,1} = V_{3,1} = V_{dc}$<br>$V_{1,j} = V_{2,j} = V_{3,j} = 2V_{dc}$<br>for $j = 2, 3, \dots, n$            | 12n -3                 | 6n – 2                                      | (40n -13)V <sub>dc</sub> |

| Third proposed algorithm $(P_3)$  | $V_{1,1} = V_{2,1} = V_{3,1} = V_{dc}$ $V_{1,j} = \frac{1}{3}V_{2,j} = V_{3,j} = 3^{j-2}V_{dc}$ for $j = 2, 3, \dots, n$ | 5(3 <sup>n-1</sup> )+4 | $\left[\frac{5(3^{n-1})+3}{2}\right]V_{dc}$ | $[82(3^{n-1})-7]V_{dc}$  |

| Fourth proposed algorithm $(P_4)$ | $V_{1,j} = 0.5V_{2,j} = V_{3,j} = 2^{j-1}V_{dc}$<br>for $j = 1, 2, \dots, n$                                             | 2 <sup>n+3</sup> -5    | $(2^{n+2}-3)V_{dc}$                         | $[7(2^{n+2})-22]V_{dc}$  |

Therefore, an H-bridge with four switches T1—T4 is added to the proposed topology. This inverter is called the developed cascaded multilevel inverter and is shown in Fig. 2(b). If switches T1 and T4 are turned on, load voltage vL is equal to vo, and if power switches T2 and T3 are turned on, the load voltage will be —vo. For the proposed inverter, the number of switches Nswitch and the number of dc voltage sources Nsource are given by the following equations, respectively,

$$N_{\text{switch}} = 5n + 6$$

(2)

$$N_{\text{source}} = 3n + 1$$

(3)

Where n is the number of series-connected basic units. As the unidirectional power switches are used in the proposed cascaded multilevel inverter, the number of power switches is equal to the numbers of IGBTs, power diodes, and driver circuits. The other main parameter in calculating the total cost of the inverter is the

maximum amount of blocked voltage by the switches. If the values of the blocked voltage by the switches are reduced, the total cost of the inverter decreases [12]. In addition, this value has the most important effect in selecting the semiconductor devices because this value determines the voltage rating of the required power devices. Therefore, in order to calculate this index, it is necessary to consider the amount of the blocked voltage by each of the switches. According to Fig. 2(b), the values of the blocked voltage by switches are equal to

$$V_{S'1} = V_{S'2} = V_{1,1} \tag{4}$$

$$V_{S1,j} = V_{S3,j} = \frac{V_{1,j} + V_{2,j} + V_{3,j}}{2}$$

(5)

$$V_{S4,j} = V_{S2,j} = V_{2,j}$$

(6)

$$V_{S5,j} = V_{1,j} + V_{2,j} + V_{3,j}$$

(7)

$$V_{T1} = V_{T2} = V_{T3} = V_{T4} = V_{o, \max}$$

(8)

Where Vo, max is the maximum amplitude of the producible output voltage. Therefore, the maximum amount of the blocked voltage in the proposed inverter Vblock is equal to

$$V_{\text{block}} = \sum_{j=1}^{n} V_{\text{block}, j} + V'_{\text{block}} + V_{\text{block}, H}$$

(9)

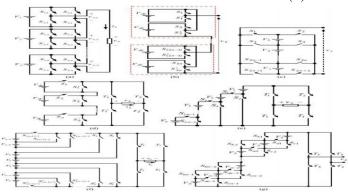

Fig. 3. Cascaded multilevel inverters. (a) Conventional cascaded multilevel inverter R2

A Peer Revieved Open Access International Journal

www.ijiemr.org

for V1 = V2 =  $\cdot \cdot \cdot$  = Vn = Vdc, R3 for V1 = Vdc, V2 =  $\cdot \cdot \cdot$  = Vn = 2Vdc [12], and R4 for V1 = Vdc, V2 =  $\cdot \cdot \cdot$  = Vn = 3Vdc. (b) Presented topology, with R7 for V1 = V2 =  $\cdot \cdot \cdot$  = Vn = Vdc. (c) Presented topology, with R8 for V1 = V2 =  $\cdot \cdot \cdot$  = Vn = Vdc and R9 for V1 = Vdc, V2 =  $\cdot \cdot \cdot$  = Vn = 2Vdc. (d) Presented topology with R10. (e) Presented topology with R6 for V1 = V2 =  $\cdot \cdot \cdot$  = Vn = Vdc. (f) Presented topology with R5 for V1 = V2 =  $\cdot \cdot \cdot$  = Vn = Vdc.(g) Presented topology in [13], with R1 for V1 = V2 =  $\cdot \cdot \cdot \cdot$  = Vn = Vdc.

In (9), Vblock, i, Vblock, and Vblock, H indicate the blocked voltage by the jth basic unit, the additional dc voltage sources, and the used H-bridge, respectively.In the developed inverter, the number and maximum amplitude of the generated output levels are based on the value of the used dc voltage sources. Therefore, different algorithmsare proposed four determine the magnitude of the dc voltage sources. These proposed algorithms and all their parameters are calculated and shown in Table III. According to the fact that the magnitudes of all proposed algorithms except the first algorithm are different, the proposed cascaded multilevel inverter based on these algorithms is considered an asymmetric cascaded multilevel inverter. In addition, based on the equations of the maximum output voltage levels and its maximum amplitude, it is clear that these values in the asymmetric cascaded multilevel inverter are more than those in the symmetric cascaded multilevel inverters with the same number of used dc voltage sources and power switches.

## III. COMPARING THE PROPOSED TOPOLOGY WITH THE CONVENTIONAL TOPOLOGIES

The main aim of introducing the developed cascaded inverter is to increase the number of output voltage levels by using the minimum number of power electronic devices. Therefore, several comparisons are done between the developed proposed the topology and conventional cascaded inverters from the numbers of IGBTs, driver circuits, and dc voltage sources points of view. In addition, the maximum amount of the blocked voltage by the power switches is also compared between the proposed inverter and the other presented topologies. In this comparison, the proposed cascaded inverter that is shown in Fig. 2(b) with its proposed algorithms is represented by P1 to P4, respectively. In [13], a symmetric cascaded multilevel inverter has been presented that is shown by R1 in this comparison. The H-bridge cascaded multilevel inverter has been presented. This inverter is represented by R2. In addition, two other algorithms have been presented for the H-bridge cascaded inverter in [12] and that are represented by R3 and R4, respectively. In, three other symmetric cascaded multilevel inverters have been presented.

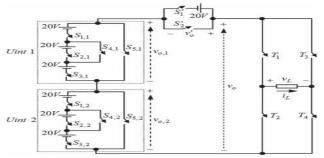

Fig. 4. Cascaded 15-level inverter based on the proposed basic unit.

A Peer Revieved Open Access International Journal

www.ijiemr.org

by These inverters shown R5-R7. are respectively. The other cascaded multilevel inverter with two different algorithms has been presented. This inverter with its algorithms is represented by R8 and R9, respectively. Another symmetric cascaded multilevel inverter that has been presented is represented by R10 in this comparison. Fig. 3 indicates all of the aforementioned cascaded multilevel inverters. In this section, the investigations are done on a cascaded multilevel inverter that is shown in Fig. 4. This inverter consists of two proposed basicunits and one additional series-connected dc voltage source that lead to the use of 7 dc voltage sources and 12 unidirectional power switches. The first proposed algorithm is considered to determine the magnitude of the dc voltage sources with Vdc =20 V. According to (5), this inverter is able to generate 15 levels (seven positive levels, seven negative levels, and one zero level) with the maximum amplitude of 140 V at the output. It is important to note that the load is assumed as a resistiveinductive (R-L) load, with R=70  $\Omega$ , and L=55 mH. It is important to point out that the used control method in this inverter is fundamental control method. The main reason to select this control method is its low switching frequency compared with other control methods that leads to reduction in switching losses

#### IV.MATLAB/SIMULATION RESULTS

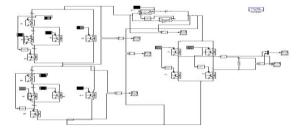

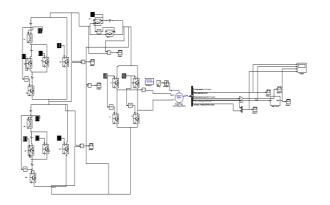

Fig.5.Matlab/Simulation Model Of Cascaded 15-Level Inverter Based On The Proposed Basic Unit

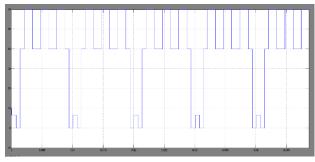

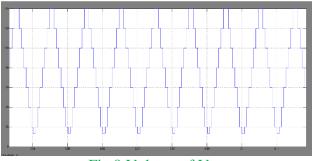

Fig.6.Proposed Basic Unit 1 of Voltage (Vo1).

Fig.7.Proposed Basic Unit 2 of Voltage (Vo2).

Fig.8.Output Voltage of Vo'.

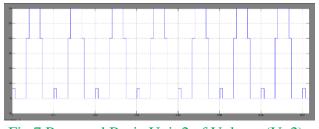

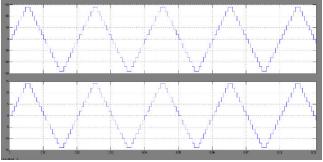

Fig.9. Voltage of Vo.

A Peer Revieved Open Access International Journal

www.ijiemr.org

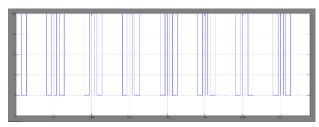

Fig.10.Output Voltage and Current of Fifteen Level Inverter.

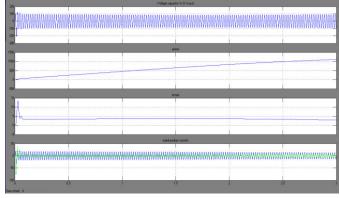

Fig.11.Matlab/Simulation Model of Three Phase Fifteen Level Inverter with induction motor

Fig.12.shows the performance of the motor

#### V. CONCLUSION

In this paper, a cascaded multilevel inverter based on a new basic unit is proposed. The

proposed unit is only able to generate positive levels at the output. Therefore, in order to generate all voltage levels (positive and negative) the H-bridge is added to the proposed topology. The proposed inverter has the advantages of reducing the number of switches and gate drives circuits by 25 % compared with the conventional Multi-level inverter. Therefore, the proposed inverter exhibits the merits of simplified gate drive, low cost compared to the other topologies for the same number of phase levels.A Three-Phase Cascaded voltages Multilevel Inverter Based on a New Basic Unit with Reduced Number of Power Switches for induction motor system.

#### REFERENCES

[1].Ebrahim Babaei, Member, IEEE, Sara Laali, Student Member, IEEE, and Zahra Bayat"A Single-Phase Cascaded Multilevel Inverter Based on a New Basic Unit With Reduced Number of Power Switches"IEEE Transactions On Industrial Electronics, VOL. 62, NO. 2, FEBRUARY 2015.

[2] E. Babaei, S. Alilu, and S. Laali, "A new general topology for cascaded multilevel inverters with reduced number of components based on developed H-bridge," IEEE Trans. Ind. Electron., vol. 61, no. 8, pp. 3932–3939, Aug. 2014.

[3] M. F. Kangarlu and E. Babaei, "A generalized cascaded multilevel inverter using series connection of sub-multilevel inverters," IEEE Trans. Power Electron., vol. 28, no. 2, pp. 625–636, Feb. 2013.

[4] J. H. Kim, S. K. Sul, and P. N. Enjeti, "A carrier-based PWM method with optimum switching sequence for a multilevel four-leg

A Peer Revieved Open Access International Journal

www.ijiemr.org

voltagesource inverter," IEEE Trans. Ind. Appl., vol. 44, no. 4, pp. 1239–1248, Jul./Aug. 2008.

- [5] O. Lopez et al., "Comparison of a FPGA implementation of two multilevel space vector PWM algorithms," IEEE Trans. Ind. Electron., vol. 55, no. 4, pp. 1537–1547, Apr. 2008.

- [6] E. Babaei and S. Sheermohammadzadeh, "Hybrid multilevel inverter using switched-capacitor units," IEEE Trans. Ind. Electron., vol. 61, no. 9, pp. 4614–4621, Sep. 2014.

- [7] A. A. Boora, A. Nami, F. Zare, A. Ghosh, and F. Blaabjerg, "Voltage sharing converter to supply single-phase asymmetric four-level diode clamped inverter with high power factor loads," IEEE Trans. Power Electron., vol. 25, no. 10, pp. 2507–2520, Oct. 2010.

- [8] J. Rodriguez, S. Bernet, P. Steimer, and I. Lizama, "A survey on natural point clamped inverters," IEEE Trans. Ind. Electron., vol. 57, no. 7, pp. 2219–2230, Jul. 2010.

- [9] E. Babaei, M. F. Kangarlu, M. Sabahi, and M. R. Alizadeh Pahlavani, "Cascaded multilevel inverter using sub-multilevel cells," Electr. Power Syst. Res., vol. 96, pp. 101–110, Mar. 2013.

- [10] J. C. Wu, K. D. Wu, H. L. Jou, and S. T. Xiao, "Diode-clamped multilevel power converter with a zero-sequence current loop for three-phase three-wire hybrid power filter," Elect. Power Syst. Res., vol. 81, no. 2, pp. 263–270, Feb. 2011.

- [11] N. Farokhnia, S. H. Fathi, N. Yousefpoor, and M. K. Bakhshizadeh, "Minimizations of total harmonic distortion in a cascaded multilevel inverter by regulating of voltages DC sources," IET Power Electron., vol. 5, no. 1, pp. 106–114, Jan. 2012.

[12] S. Laali, K. Abbaszadeh, and H. Lesani, "Control of asymmetric cascaded multilevel inverters based on charge balance control methods," Int. Rev. Elect. Eng., vol. 6, no. 2, pp. 522–528, Mar./Apr. 2011.

[13] E. Babaei and S. H. Hosseini, "Charge balance control methods for asymmetrical cascade multilevel converters," in Proc. ICEMS, Seoul, Korea, 2007, pp. 74–79.

#### **AUTHORS PROFILE:**

Indu Kumari received B. Tech in Electrical and Electronics Engineering from Annamacharya Inst. of Technology &

Science(JNTUH) in the year 2014 and now pursuing M. Tech in the stream of Power Electronics Engineering at Annamacharya Inst. Of Tech & Sciences, Hyderabad.

Mr. Jadapalli Sreedhar was born at Rajampet near kadpa(dist.), AP., India. He completed his

B. Tech in Electrical and Electronics Engineering, from JNTU in the year 2002. He completed his M. Tech in Power Electronics from JNTU in the year 2006. Currently, he is pursuing PhD from GITAM

University, Hyderabad campus on the topic 'Synchronous Buck Converter Applications'. He is working as Associate Professor in the Department of EEE, Annamacharya Inst. Of Tech.& Sciences, Hyderabad, since 2012. His fields of interest are Power Systems and Power Electronics. So far, he has published 4 papers in International Journals and 1 paper in a National Journal.

A Peer Revieved Open Access International Journal

www.ijiemr.org