A Peer Revieved Open Access International Journal

www.ijiemr.org

#### **COPY RIGHT**

2017 IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 23<sup>rd</sup> July 2017. Link:

http://www.ijiemr.org/downloads.php?vol=Volume-6&issue=ISSUE-5

Title: Eaccs: Structuring An Elastic Ac Conduction System for Renewable Energy.

Volume 06, Issue 05, Page No: 2013 – 2022.

#### **Paper Authors**

- \* BHAWNI VISHWAKARMA, ANKITA KOSHTI, MR. NISHEET SONI.

- \* Dept of power systems, Shri ram Institute of Technology.

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

# EACCS: STRUCTURING AN ELASTIC AC CONDUCTION SYSTEM FOR RENEWABLE ENERGY

#### <sup>1</sup>BHAWNI VISHWAKARMA, <sup>2</sup>ANKITA KOSHTI, <sup>3</sup>MR. NISHEET SONI

PG Scholar, Dept of power systems, Shri ram Institute of Technology, Jabalpur, Madhya Pradesh.

Assistant Professor, Dept of power systems, Shri ram Institute of Technology, Jabalpur, Madhya Pradesh.

HOD, Dept of power systems, Shri ram Institute of Technology, Jabalpur, Madhya Pradesh.

#### **ABSTRACT:**

In this paper, a new single-phase wind energy inverter (WEI) with flexible AC transmission system (FACTS) capability is presented. The proposed inverter is placed between the wind turbine and the grid, same as a regular WEI, and is able to regulate active and reactive power transferred to the grid. This inverter is equipped with distribution static synchronous compensators option in order to control the power factor (PF) of the local feeder lines. Using the proposed inverter for small-to medium-size wind applications will eliminate the use of capacitor banks as well as FACTS devices to control the PF of the distribution lines. The goal of this paper is to introduce new ways to increase the penetration of renewable energy systems into the distribution systems. This will encourage the utilities and customers to act not only as a consumer, but also as a supplier of energy. Moreover, using the new types of converters with FACTS capabilities will significantly reduce the total cost of the renewable energy application. In this paper, modular multilevel converter is used as the desired topology to meet all the requirements of a single-phase system such as compatibility with IEEE standards, total harmonic distortion (THD), efficiency, and total cost of the system. The proposed control strategy regulates the active and reactive power using power angle and modulation index, respectively. The function of the proposed inverter is to transfer active power to the grid as well as keeping the PF of the local power lines constant at a target PF regardless of the incoming active power from the wind turbine. The simulations for an 11-level inverter have been done in MATLAB/Simulink. To validate the simulation results, a scaled prototype model of the proposed inverter has been built and tested.

**Keywords:** EACCS, Modular Multilevel Converter (MMC), Multilevel Inverter (MLI), Wind Energy Inverter (WEI).

ISSN: 2456 - 5083

#### I. INTRODUCTION

The Role of power electronics in distribution systems has greatly increased recently. The power electronic devices are usually used to convert the non conventional forms of energy to the suitable energy for power grids, in terms of voltage and frequency. In permanent magnet (PM) wind applications, a back-to-back converter is normally utilized to connect the

generator to the grid. A rectifier equipped with a maximum power point tracker (MPPT), converts the output power of the wind turbine to a dc power. The dc power is then converted to the desired ac power for power lines using an inverter and a transformer. With recent developments in wind energy, utilizing smarter wind energy inverters (WEIs) has become an important issue. There are a lot of single-phase lines in the United States, which power small

A Peer Revieved Open Access International Journal

www.ijiemr.org

farms or remote houses [1], [2]. Such customers have the potential to produce their required energy using a small-to-medium-size wind turbine. Increasing the number of smallto-medium wind turbines will make several troubles for local utilities such as harmonics or power factor (PF)issues. A high PF is generally desirable in a power system to decrease power losses and improve voltage regulation at the load. It is often desirable to adjust the PF of a system to near1.0. When reactive elements supply or absorb reactive power near the load, the apparent power is reduced. In other words, the current drawn by the load is reduced, which decreases the power losses. Therefore, the voltage regulation is improved if the reactive power compensation is performed near large loads. Traditionally, utilities have to use capacitor banks to compensate the PF issues, which will increase the total cost of the system. The modern ways of controlling the PF of these power lines is to use small distribution static synchronous compensators (D-STATCOMs). The D-STATCOMs are normally placed in parallel with the distributed generation systems as well as the power systems to operate as a source or sink of reactive power to increase the power quality issues of the power lines. Using regular STATCOMs for small-to-medium size single-phase wind applications does not make economic sense and increase the cost of the system significantly. This is where the idea of using smarter WEIs with FACTS capabilities shows itself as a new idea to meet the targets of being cost-effective as well as compatible with IEEE standards. The proposed inverter in this paper is equipped with a D-STATCOM option to regulate the reactive power of the local distribution lines and can be placed between

the wind turbine and the grid, same as a regular WEI without any additional cost. The function of the proposed inverter is not only to convert dc power coming from dc link to a suitable ac power for the main grid, but also to fix the PF of the local grid at a target PF by injecting enough reactive power to the grid. In the proposed control strategy, the concepts of the inverter and the D-STATCO have been combined to make a new inverter, which possesses FACTS capability with no additional cost. The proposed control strategy allows the inverter to act as an inverter with D-STATCOM option when there is enough wind to produce active power, and to act as a D-STATCOM when there is no wind. The active power is controlled by adjusting

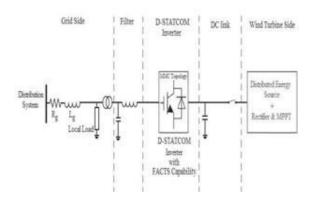

Fig.1. Complete configuration of the proposed inverter with FACTS capability.

The power angle  $\delta$ , which is the angle between the voltages of the inverter and the grid, and reactive power is regulated by the modulation index m. There are a large number of publications on integration of renewable energy systems into power systems. A list of complete publications on FACTS applications for grid integration of wind and solar energy was presented in [3]. In [4], new commercial wind

ISSN: 2456 - 5083

A Peer Revieved Open Access International Journal

www.ijiemr.org

energy converters with FACTS capabilities are introduced without any detailed information regarding the efficiency or the topology used for the converters. In [5], a complete list of the most important multilevel inverters reviewed. Also, different modulation methods such as sinusoidal pulse width modulation(PWM) selective harmonic elimination, optimized harmonic stepped waveform technique, and space vector modulation were discussed and compared. Among all multilevel topologies [6]-[9], the cascaded H-bridge multilevel converter is very well known for STATCOM applications for several reasons [10]-[12]. The main reason is that it is simple to obtain a high number of levels, which can help to connect STATCOM directly to medium voltage grids. The modular multilevel converter(MMC) was introduced in the early 2000s [13], [14]. Reference [15] describes a MMC converter for high voltage DC(HVDC) applications. This paper mostly looks at the main circuit components. Also, it compares two different types of MMC, including H-bridge and full-bridge modules. In [9] and [16], a new single-phase inverter using hybrid clamped topology for renewable energy systems is presented. The proposed inverter is placed between the renewable energy source and the main grid. The main drawback of the proposed inverter is that the output current has significant fluctuations that are not compatible with IEEE standards. The authors believe that the problem is related to the snubber circuit design. Several other applications of custom power electronics in renew able energy systems exist, including [17] an application of a custom power interface where two modes of operation, including an

active power filter and a renewable energy STATCOM. Another application [18] looks at the current source inverter, which controls reactive power and regulates voltage at the point of common coupling (PCC). Varmaet al.[19], [20] propose an application of photovoltaic (PV) solar inverter as STATCOM in order to regulate voltage on three phase power systems, for improving transient stability and power transfer limit in transmission systems. The authors called their proposed system PV-STATCOM. Similar to wind farms (when there is no wind), solar farms are idle during nights. We proposed a control strategy that makes the solar farms to act as STATCOMs during night when they are not able to produce active power. The main purpose of the PV-STATCOM system is to improve the voltage control and the PF correction on three-phase transmission systems. In this paper, the proposed WEI utilizes MMC topology, which has been introduced recently for HVDC applications. Replacing conventional inverters with this inverter will eliminate the need to use a separate capacitor bank or a STATCOM device to fix the PF of the local distribution grids. Obviously, depending on the size of the power system, multiple inverters might be used in order to reach the desired PF. The unique work in this paper is the use of MMC topology for a single phase voltage-source inverter, which meets the IEEE standard519 requirements, and is able to control the PF of the grid regardless of the wind speed Fig. 1 shows the complete grid-connected mode configuration of the proposed inverter. The dc link of the inverter is connected to the wind turbine through a rectifier using MPPT and its output terminal is connected to the utility grid through a series-connected second-order filter and a distribution transformer.

ISSN: 2456 - 5083

A Peer Revieved Open Access International Journal

www.ijiemr.org

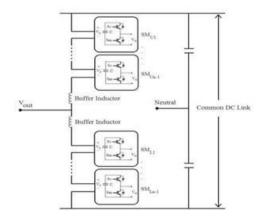

### II. MODULAR MULTILEVEL CONVERTER

MMC has gained increasing attention recently. A number of papers were published on the structure, control, and application of this topology [21], [22], but none has suggested the use of that for inverter + D-STATCOM application. This topology consists of several half-bridge (HB) sub modules (SMs) per each phase, which are connected in series. An nlevel single phase MMC consists of a series connection of 2(n - 1)basic SMs and two buffer inductors. Each SM possesses two semiconductor switches, which operate in complementary mode, and one capacitor. The exclusive structure of MMC becomes it an ideal candidate for medium-to-high-voltage applications such as wind energy applications. Moreover, this topology needs only one dc source, which is a key point for wind applications. MMC requires large capacitors which may increase the cost of the systems; however, this problem is offset by the lack of need for any snubber circuit. The main benefits of the MMC topology are: modular design based on identical converter cells, simple voltage scaling by a series connection of cells, simple realization of redundancy, possibility of a common dc bus. Fig. 2 shows the circuit configuration of a single-phase MMC and the structure of its SMs consisting of two power switches and a floating capacitor. The output voltage of each SM (v<sub>o</sub>) is either equal to its capacitor voltage (v<sub>c</sub>) or zero, depending on the switching states.

Fig.2.Structure of a single-phase MMC inverter structure.

The buffer inductors must provide current control in each phase arm and limit the fault currents. To describe the operation of MMC, each SM can be considered as a two poles witch. If Sui, which is defined as the status of the ith sub module in the upper arm, is equal to unity, then the output of the ith SM is equal to the corresponding capacitor voltage; otherwise it is zero. Likewise, if S<sub>li</sub> which is defined as the status of the ith sub module in the lower arm, is equal to unity, then the output of the ith lower SM is equal to the corresponding capacitor voltage; otherwise it is zero. Generally, when Sui or S<sub>li</sub> is equal to unity, the i<sup>th</sup> upper or lower SM is ON; otherwise it is OFF. Therefore, the upper and lower arm voltages of the MMC are as follows:

$$V_{\text{upper Arm}} = \sum_{i=1}^{n-1} s_{ui} v_{ci} + v_{11}$$

(1)

$$V_{\text{lower Arm}} = \sum_{i=1}^{n-1} s_{ui} v_{ci} + v_{11}$$

(2)

Where  $v_{11}$  and  $v_{12}$  are the voltages of the upper and lower buffer inductors, n is the number of voltage levels, and  $v_{ci}$  is the voltage of the i<sup>th</sup> SMs capacitor in upper arm or lower arm. A single-

A Peer Revieved Open Access International Journal

www.ijiemr.org

phase 11-levelMMC inverter consists of 20 SMs which translates to 40 power switches, 20 capacitors, and2 buffer inductors. The dc and ac voltages of the 11-levelMMC are described by

$$V_{DC}=V_{upper Arm}+V_{lower arm}$$

$$=\sum_{i=1}^{10}(s_{ui}v_{ci})+\sum_{i=1}^{10}(s_{ui}v_{ci})+(V_{11}+V_{12})$$

$$V_{our}-\frac{V_{DC}}{2}-V_{upper arm}-\frac{V_{DC}}{2}-V_{lower arm}$$

(4)

#### III. PROPOSED CONTROL STRATEGY

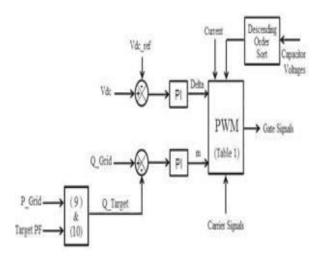

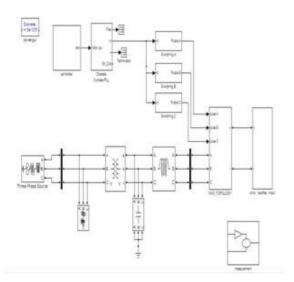

The proposed controller consists of three major functions. The first function is to control the active and reactive power. Transferred to the power lines, the second function is to keep the voltages of the SMs' capacitors balanced, and the third function is to generate desired PWM signals. Fig. 3 shows the complete proposed controller system. The aim of the designed inverter is to transfer active power coming from the wind turbine as well as to provide utilities with distributive control of volt-ampere reactive (VAR) compensation and PF correction of feeder lines.

The application of the proposed inverter requires active and reactive power to be controlled fully independent, so that if wind is blowing, the device should be working as a normal inverter plus being able to fix the PF of the local grid at a target PF (D-STATCOM option), and if there is no wind, the device should be only operating as a D-STATCOM (or capacitor bank) to regulate PF of the local grid. This translates to two modes of operation: 1) when wind is blowing and active power is coming from the wind turbine: the inverter plus D-STATCOM mode. In this mode, the device

is working as a regular inverter to transfer active power from the renewable energy source to the grid as well as working as a normal D-STATCOM to regulate the reactive power of the grid in order to control the PF of the grid and 2) when wind speed is zero or too low to generate active power: the D-STATCOM mode.

Fig. 3.Schematic of the proposed controller system.

In this case, the inverter is acting only as a source of reactive power to control the PF of the grid, as a D-STATCOM. This option eliminates the use of additional capacitor banks or external STATCOMs to regulate the PF of the distribution feeder lines. Obviously, the device is capable of outputting up to its rated maximum real power and/or reactive power, and will always output all real power generated by the wind turbine to the grid. The amount of reactive power, up to the design maximum, is dependent only on what the utility asks the device to produce. Generally, (5) and (6) dictate the power flow between a STATCOM device and power lines

A Peer Revieved Open Access International Journal

www.ijiemr.org

$$P_{S} = \frac{E_{S}E_{L}}{x} sin_{\delta}$$

(5)

$$Q_S = -\frac{E_S E_L \cos_g - E_L^2}{\chi} \tag{6}$$

Where X is the inductance between the STATCOM (here as inverter) and the grid which is normally considered as output filter inductance added to the transmission line inductance. The root mean square (RMS) voltage of the STATCOM (=inverter) is given as Es and is considered to be out of phase by an angle of  $\delta$  to the RMS line voltage E1.In the proposed control strategy, active and reactive power transferred between the inverter and the distribution grid is controlled by selecting both the voltage level of the inverter and the angle  $\delta$ between the voltages of inverter and grid, respectively. The amplitude of the inverter voltage is regulated by changing modulation index m and the angle  $\delta$  by adding a delay to the firing signals which concludes

$$P_{S} = \frac{mE_{S}E_{L}}{X} sin_{\delta}$$

(7)

$$Q_S = -\frac{mE_S E_L \cos_{\delta} - E_L^2}{X}$$

(8)

In this paper, m is the key factor to control the reactive power compensation and its main task is to make the PF of the grid equal to the target PF.  $\delta$  is the control parameter to adjust the active power control between the inverter and the grid. Several assumptions should be considered for the proposed controller which are as: 1) the load on the feeder line should be considered fixed for a small window of time and there is no change in the load during a cycle of the grid frequency;2) the feeder line can be accurately modeled as a constant P,Q load. This means that the power produced by a

wind turbine will displace other power on the feeder line and not add to it; and 3) although making a change in m or  $\delta$  has effect on both (7) and (8), it is assumed that a change in the modulation index will predominantly affect Q, while a change in delta will predominantly affect P. Any effect on Q from a small change in delta is thus ignored. This results in controlling P and Q independently. Equation (9) shows the relation between the target reactive power and the target PF where PG is the amount of active power on the grid, QT is the target amount of reactive power, and PFT is the target PF desired by the utility. So, QT can be calculated as Using the target reactive power for the grid is determined and is compared with the actual value of the reactive power of the grid. Using a PI compensator will determine the desired value for the modulation index.

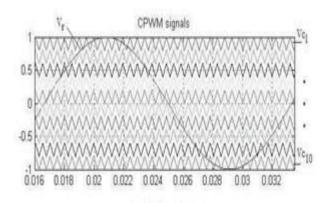

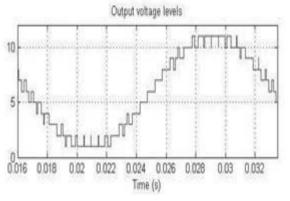

carrier based pulse width modulation (CPWM) method [25], [26] is used. The top graph in Fig. 4 shows the reference signal and the carrier waveforms for an 11-level MMC inverter using CPWM technique. The bottom graph of Fig. 4 shows the output voltage levels generated based on Table I. In an 11-level CPWM technique, ten carrier signals are compared with a reference sinusoidal signal. In Fig 4, based on the phase of the reference signal ( $v_r$ ), there are 11 operating regions where each region defines a voltage level in the output

$$nupperArm + nlower Arm = 10$$

(9)

Where nupperArm and nlower Arm are the numbers of SMs which are ON (Scis ON and Smis OFF in Fig. 1) in the upper armor lower arm, respectively. In an 11-level MMC inverter, there are ten upper and ten lower SMs where each SM has a capacitor. For instance, in voltage level 1 of Table I, all the upper SMs should be

A Peer Revieved Open Access International Journal

www.ijiemr.org

OFF and all the lower SMs should be ON, which translates to the fact that the main switches Sm of all upper SMs and the auxiliary switches (Sc) of all lower SMs have to be ON and all the other switches have to be OFF. In this case, the input dc voltage is applied only to the ten lower capacitors, so that

TABLE I: Operating Regions for An 11 Level MMC Inverter

| Voltage<br>level | Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | N <sub>UpperArm</sub> | D <sub>lowerArm</sub> | V <sub>out</sub>                            |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|---------------------------------------------|

| 1                | $v_r \ge v_{c1}, v_{c2}, v_{c3}, v_{c4}$ $v_{c5}, v_{c6}, v_{c7}, v_{c8}, v_{c6}, v_{c10}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                     | 10                    | 5v <sub>dc</sub> / <sub>10</sub>            |

| 2                | $\begin{aligned} v_r < v_{c1} \\ v_t \ge v_{c2}, v_{c3}, v_{c4}, \\ v_{c5}, v_{c6}, v_{c7}, v_{c6}, v_{c8}, v_{c10} \end{aligned}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                     | 9                     | 4v <sub>dc</sub> / <sub>10</sub>            |

| 3                | $\begin{aligned} v_r < v_{c1}, v_{c2} \\ v_r \ge v_{c3}, v_{c4}, \\ v_{c5}, v_{c6}, v_{c7}, v_{c6}, v_{c6}, v_{c10} \end{aligned}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2                     | 8                     | <sup>3v</sup> <sub>dc</sub> / <sub>10</sub> |

| 4                | $v_{c} < v_{c1}, v_{c2}, v_{c3}$<br>$v_{f} \ge v_{c4}, v_{c5}, v_{c6}, v_{c7}, v_{c8}, v_{c9}, v_{c9}, v_{c10}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3                     | 7                     | 2v <sub>dc/10</sub>                         |

| 5                | $\begin{aligned} v_r < v_{c1}, v_{r2}, v_{c1}, v_{c4} \\ v_r \ge v_{c5}, v_{c6}, v_{r2}, v_{c8}, v_{c6}, v_{c6$ | 4                     | 6                     | v <sub>dc</sub> / <sub>10</sub>             |

| 6                | $\begin{aligned} & v_r < v_{c1}, v_{c2}, v_{c3}, v_{c4}, v_{c5} \\ & v_r \ge v_{c6}, v_{c7}, v_{c6}, v_{c6}, \\ & v_{c10} \end{aligned}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5                     | 5                     | 0                                           |

| 7                | $\begin{aligned} v_r < v_{c3}, v_{c2}, v_{c3}, v_{c4}, v_{c5}, \\ v_{c6} \\ v_r \ge v_{c7}, v_{c8}, v_{c9}, v_{c10} \end{aligned}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6                     | 4                     | -v <sub>dt</sub> / <sub>10</sub>            |

| 8                | $\begin{aligned} v_r < v_{c1}, v_{c2}, v_{c3}, v_{c4}, v_{c5}, \\ v_{c6}, v_{c7} \\ v_r \ge v_{c6}, v_{c6}, v_{c10} \end{aligned}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7                     | 3                     | -2v <sub>dc/10</sub>                        |

| 9                | $\begin{aligned} v_t < v_{c1}, v_{c2}, v_{c3}, v_{c4}, v_{c5}, \\ v_{c6}, v_{c7}, v_{c8} \\ v_t \ge v_{c9}, v_{c10} \end{aligned}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8                     | 2                     | -3v <sub>dc/10</sub>                        |

| 10               | $\begin{aligned} v_{\tau} < v_{c1}, v_{c2}, v_{c6}, v_{c4}, v_{c5}, \\ v_{c6}, v_{c7}, v_{c6}, v_{c9} \\ v_{\tau} \ge v_{c10} \end{aligned}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9                     | 1                     | -4v <sub>dc/10</sub>                        |

| 11               | $\begin{aligned} v_r < v_{c1}, v_{c2}, v_{c3}, v_{c4}, v_{c5}, \\ v_{c6}, v_{c7}, v_{c8}, v_{c6}, v_{c10} \end{aligned}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 10                    | 0                     | -5v <sub>dc/10</sub>                        |

Fig. 4. CPWM waveforms for an 11-level MMC inverter, and the generated output voltage levels.

The power angle is also determined by comparing the actual dc voltage of the inverter with a reference value. A PI compensator determines the desired value for the power angle. The second function of the controller system is to keep the capacitors voltages balanced. In order to this a the output voltage is  $v_{DC}/2$ . Fig. 5 illustrates the selection of capacitors for different voltage levels shown in Table I. The most critical issue to control MMC is to maintain the voltage balance across all the capacitors. Therefore, the SMs' voltages are measured and sorted in descending order during each cycle. If the current flowing through the switches is positive, so that capacitors are being charged, nupper Armand nupperArm and of the SMs in upper arm and lower arm with the lowest voltages are selected,

A Peer Revieved Open Access International Journal

www.ijiemr.org

respectively. As a result, ten capacitors with lowest voltages are chosen to be charged. Likewise, if the current flowing through the switches is negative, so that capacitors are being discharged, nupper Armand nupperArm of the SMs in upper arm and lower arm with highest voltages are selected, respectively. As a result, ten capacitors with highest voltages are chosen to be discharged. Consequently, the voltages of the SMs' capacitors are balanced. Considering Table I and based on the direction of the current flowing through the switches, the proper algorithm will be selected to maintain capacitor balance. The third function of the controller system is the PWM generation block. In this block, based on the desired modulation index, power angle, voltages of the capacitors, direction of the current flowing through the switches and using Table I, the controller generates the PWM signals in order to meet all the system requirements.

## IV. SIMULATION AND PRACTICAL RESULTS

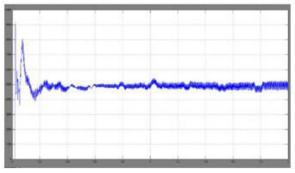

The design of an 11-level MMC inverter was carried out in MATLAB/ Simulink. The simulation is 20 s long and contains severe ramping and de-ramping of the wind turbine. The goal is to assess the behavior of the control system in the worst conditions. Table II shows the values of the parameters used for the simulation. Before t = 6 s, there is no wind to power the wind turbine; therefore, the dc link is open-circuited. At t = 6 s, the input power of the inverter is ramped up to 12 kW in 5 s, and then ramped down to 3.5 kW 4 s later. Fig. 6 shows the output active power from the wind turbine.

Fig. 5.Matlab/simulink model of the proposed method.

#### TABLE II: Parameters Used For the Simulation

| Parameter                     | Value     |  |

|-------------------------------|-----------|--|

| $L_{tine}$                    | 15 mH     |  |

| $R_{tine}$                    | 1 Ohm     |  |

| $L_{Filter}$                  | 5 mH      |  |

| Transformer primary voltage   | 12000 V   |  |

| Fransformer secondary voltage | 600 V     |  |

| Switching frequency           | 2 kHz     |  |

| Load active power             | 50 kW     |  |

| Load reactive power           | 34.8 kVAR |  |

| Target PF                     | 0.90      |  |

| DC link Voltage               | 2000 V    |  |

Fig.6. Simulated output active power from the wind turbine.

A Peer Revieved Open Access International Journal

www.ijiemr.org

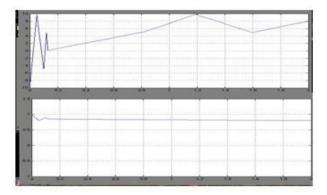

In the simulation, the local load makes the PF 0.82. When the simulation starts, the inverter provides enough compensation to reach the target PF 0.90. Fig. 7 shows the output active and reactive power

Fig.7.Simulated active and reactive power of the inverter (top graph), active and reactive power of the power lines (bottom graph).

Fig. 8.Simulated output voltage of an 11-level inverter.

from the wind turbine and the grid. After t = 6 s, the output power of the wind turbine is increased, and as a result the level of active power provided by the feeder line is decreased by the same amount. The simulated output voltage of the inverter before the filter is shown

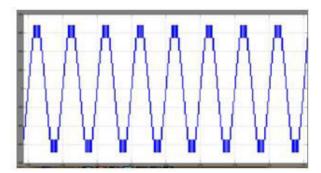

in Fig. 8. Fig. 9 shows the PF of the grid. The PF of the grid is constant at 0.90 regardless of the active power from the wind turbine, showing that the main goal of the inverter is achieved. The setpoint for dc link voltage of the inverter is 2000 V and the RMS value of the output ac voltage is 600 V. The delta and modulation index graphs are shown in Fig. 10. As soon as the active power comes from the wind turbine, the controller system increases the value of the power angle in order to output more active power to the grid. Therefore, the active power provided from the feeder lines to the load is decreased, and as a result the reactive power from the feeder lines is decreased. Consequently, the modulation index is increased by the controller system to inject more reactive power needed by the load.

Fig. 9.Simulated PF of the grid.

Fig. 10. Simulated delta and modulation index of the 11-level inverter. To validate the simulation results, a scaled version of the proposed inverter has been built and tested.

A Peer Revieved Open Access International Journal

www.ijiemr.org

#### V. CONCLUSION

In this paper, the concept of a new multilevel inverter with FACTS capability for small-tomid-size wind installations is presented. The proposed system demonstrates the application of a new inverter with FACTS capability in a single unit by without any additional cost. Replacing the traditional renewable energy inverters with the proposed inverter will eliminate the need of any external STATCOM devices to regulate the PF of the grid. Clearly, depending on the size of the compensation, multiple inverters may be needed to reach the desired PF. This shows a new way in which distributed renewable sources can be used to provide control and support in distribution systems the proposed controller system adjusts the active power by changing the power angle (delta) and the reactive power is controllable by the modulation index m. The simulation results for an 11-level inverter are presented in MATLAB/Simulink. To validate the simulation results, a scaled prototype of the proposed 11level inverter with D-STATCOM capability is built and tested. Practical results show good performance of the proposed control strategy even in severe conditions.

#### VI. REFERENCES

- [1] U.S. Solar Market Insight, 2010 Year End Review Executive Summary, SEIA, Washington, DC, USA, 2011.

- [2] AWEA U.S. Wind Industry Annual Market Report Year Ending 2010, AWEA, Washington, DC, USA, 2011.

- [3] S. A. Rahman, R. K. Varma, and W. H. Litzenberger, "Bibliography of FACTS applications for grid integration of wind and PV solar powersystems: 1995–2010 IEEE

- working group report," in Proc. IEEE PowerEnergy Soc. General Meeting, Jul. 2011, pp. 1–17.

- [4]A. Beekmann, J. Marques, E. Quitmann, and S. Wachtel, "Wind energyconverters with FACTS capabilities for optimized integration of windpower into transmission and distribution systems," in Proc. CIGRE/IEEEPES Joint Symp. Integr. Wide, Scale Renew. Resour. Power Del. Syst.,Jul. 2009, pp. 1–9.

- [5] J. Rodriguez, J. S. Lai, and F. Z. Peng, "Multilevel inverters: Survey oftopologies, controls, and applications," IEEE Trans. Ind. Appl., vol. 49,no. 4, pp. 724–738, Aug. 2002.

- [6] F. Z. Peng, J. S. Lai, J. W. McKeever, and J. VanCoevering, "A multilevelvoltage-source inverter with separate DC sources for static VArgeneration," IEEE Trans. Ind. Appl., vol. 32, no. 5, pp. 1130–1138,Oct. 1996.

- [7]L. M. Tolbert and F. Z. Peng, "Multilevel converters as a utility interfacefor renewable energy systems," in Proc. IEEE Power Eng. Soc. SummerMeeting, vol. 2. Jul. 2000, pp. 1271–1274.

- [8] S. Kouro, M. Malinowski, K. Gopakumar, J. Pou, L. G. Franquelo, B. Wu, et al., "Recent advances and industrial applications of multilevelconverters," IEEE Trans. Ind. Electron., vol. 57, no. 8, pp. 2553–2580, Aug. 2010.

- [9] C. Tareila, P. Sotoodeh, and R. D. Miller, "Design and control of single-phase D-STATCOM inverter for wind application," in Proc.PEMWA, Jul. 2012, pp. 1–5.

- [10] B. Gultekin and M. Ermis, "Cascaded multilevel converter-based transmission STATCOM: System design methodology and development of a12 kV ±12 MVAr power