A Peer Revieved Open Access International Journal

www.ijiemr.org

### **COPY RIGHT**

**2022 IJIEMR**. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 30th Jul 2022. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-11&issue= Spl Issue 06

### DOI: 10.48047/IJIEMR/V11/SPL ISSUE 06/27

Title Implementation of an XOR Based 16-bit Carry Select Adder for Area, Delay and Power Minimization

Volume 11, SPL ISSUE 06, Pages: 148-151

**Paper Authors**

K.Srikanth, M.Vennela, S.Samuel, P.Manoj, Ch.Raju

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic

Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

S.Samuel

UG Student

Dept. of ECE

Science

# **Implementation of an XOR Based 16-bit Carry** Select Adder for Area, Delay and Power **Minimization**

#### K.Srikanth

Assistant Professor Dept. of ECE Balaji Institute of Technology & Science Narsampet, Warangal, India

kallepellisrikant@gmail.com

P.Manoj

UG Student Dept. of ECE Balaji Institute of Technology & Science Narsampet, Warangal, India

#### M.Vennela

UG Student Dept. of ECE Balaji Institute of Technology & Science

**UG** Student Dept. of ECE Balaji Institute of Technology & Science Narsampet, Warangal, India

ISSN 2456 - 5083

Balaji Institute of Technology & Narsampet, Warangal, India Narsampet, Warangal, India

> There are plenty of adder designs available in the literature such as Ripple Carry Adder (RCA), Carry Look Ahead Adder (CLA), Carry Select Adder (CSA), Carry Skip Adder which have their own advantages and disadvantages. CSA is one of the fastest adders because of its less area and power consumption. In CSA there are two multiplexed RCA which act in parallel assuming carry in, Cin = 0 and in other Cin = 1, then final sum is selected through multiplexer. In conventional CSA, XOR, AND and OR gate based full adders are used. These adders consumes more area in the chip due to large number of transistors are used in these gates, the delay is higher and consumes more power [9]. In the present work, XOR based modified full adder have been used as the building blocks of the modified CSA to reduce area, delay and power consumption. The layout of the 16-bit CSA is designed in Micro wind software. The results obtained from the layout data is compared with the conventional CSA [10].

#### Ch.Raju

Abstract— In different types of processors and other digital circuits adders are most widely used. Low power and area efficient high-speed circuits are most substantial area in the research of VLSI design. The carry select adder is one of the fast adders which has less area and reduced power consumption. In this paper, a 16-bit carry select adder has been presented using modified XOR based full adder to reduce circuit complexity, area and delay. The modified full adder design requires only two XOR gates and one multiplexer. The modified 16-bit carry select adder gives better result than conventional carry select adder with respect to area, power consumption and delay.

Keywords— low power, area efficient, XOR based adder, carry select adder

#### I. INTRODUCTION

In digital integrated circuit design, addition is the heart of computer arithmetic. It has special significance in processors and many other digital circuits. In rapidly growing mobile industry faster units, smaller area and less power become major concern [6]. For increasing portability of mobile electronics, area and power are the key factors. They also major concern to increase battery life. In VLSI system, reduction in area and power are the main focus point of research. Faster speed for addition and multiplication is a fundamental requirement of high-performance processors [7]. Arithmetic units are the work horse of a computational circuit and addition is the heart of this. In VLSI sub system the power efficient and high-performance adders are most desired digital circuit. Speed of adder is usually limited for carry propagation bit. The sum of each bit in an adder is generated sequentially after the addition of previous bit and a carry propagated to the next position [8].

Vol 11 Spl Issue 06, Jul 2022

#### II. XOR BASED FULL ADDER

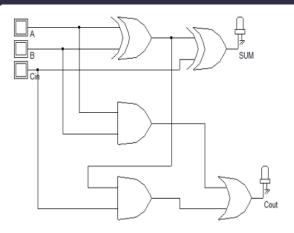

A full adder which is the main building block of n-bit adders gives the result of addition with output carry taking input carry in to consideration [11]. So, actually a one-bit full adder adds three one-bit numbers A, B, and Cin where A and B are the operands, and Cin is a bit carried in from the previous less-significant stage. A conventional full adder implementation based on basic logic gates is shown in Fig. 1.

Page 148

A Peer Revieved Open Access International Journal

www.ijiemr.org

Fig. 1: Conventional 1-bit full adder

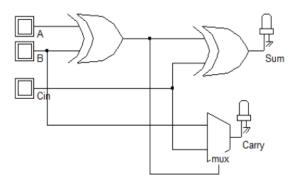

A binary full adder realization employing two XOR gates and one 2:1 MUX is shown in Fig. 2. The layout of conventional and XOR based 1-bit full adder are shown in Fig. 3 and Fig. 4 respectively. The advantage of XOR based adder is that it requires smaller number of transistors [12].

Fig. 2: XOR based 1-bit Full Adder

The main difference between the conventional and XOR based adders is that in XOR based adder other than two XOR gates only one 2:1 MUX is used which needs only 6 MOSFETs where as in conventional type adder other than two XOR gates two AND gates and one OR gate is needed which requires at least 18 number of MOSFETs. So, there is at least 12 numbers of MOSFET savings in XOR based 1-bit adders than conventional which in turn has less area and power consumption at the same time there is also a better delay performance [13].

#### III. CARRY SELECT ADDER

The CSA is constructed from two RCAs and a multiplexer. Addition of two n-bit numbers with CSA is nothing but adding two numbers taking input carry first as zero then using another adder taking input carry as one. After calculation of the two results depending on the correct carryin the correct sum as well as the correct carry-out is selected with the multiplexer connected at last to get the final output.

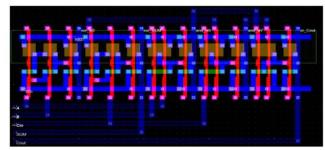

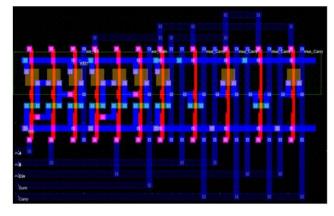

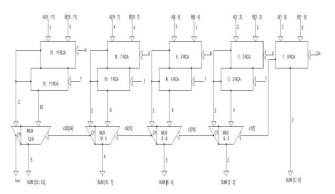

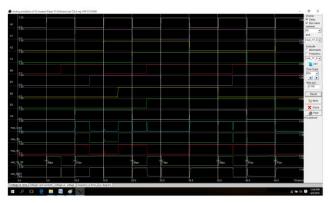

The structure of a 16-bit CSA is shown in Fig. 5. A 16-bit CSA consists of 16-full adders with the carry signal that ripples from one full adder stage to the next, i.e. from LSB to MSB [4]. The layout and input-output wave shapes of a 4-bit CSA are shown in Fig. 6 and Fig. 7 respectively. Due to clarity of the pictures, layout and input output waves of 4-bit CSA are given here in place of 16-bit adder. Results of 16-bit CSA will be given later [14]. Since XOR based 1-bit adders have been used in the 16-bit CSA which are the main building blocks so the number of MOSFETs required is much less than conventional CSA [15].

Fig. 3: Layout of conventional 1-bit full adder

Fig. 4: Layout of XOR based 1-bit full adder

Fig. 5: 16-bit carry select adder

A Peer Revieved Open Access International Journal

www.ijiemr.org

Fig. 6: Layout of 4-bit carry select adder

Fig. 7: Input-output wave shapes of a 4-bit carry select adder

#### IV. RESULTS AND DISCUSSION

The schematic circuit of the CSA has been designed using DSCH 3.1 simulator and synthesized using 90 nm CMOS technology. The layout was constructed from the Verilog file which is generated from the DSCH software. The obtained power, area and delay information of the adder is from Microwind layout simulation [16].

Table I shows the simulation results of both conventional and modified CSA (using XOR based adder) in terms of power, area, delay and power delay product (PDP). Every individual cell in the design adds to the aggregate cell zone and total power is the sum of leakage power, switching power and static power. The XOR-based circuit has the power reduction for 4-bit, 8-bit and 16-bit are 12.5%, 16.67% and 20.04% respectively. Similarly percentage reduction in area are 1.35%, 6.6% and 9.41% respectively. There is also a delay reduction of 0.8%, 1.3%, and 2.01% respectively. In Table II, gate count and Idd values are shown for 4-bit, 8-bit and 16-bit CSA respectively. In Table III, power, delay and area for 8-bit and 16-bit adders are compared with Ref [17].

| TABLE I. COM | MPARISON OF POWER, AREA AND D | ELAY BETWEEN CONVENTIONAL | . CSA AND XOR BASED CSA |

|--------------|-------------------------------|---------------------------|-------------------------|

|--------------|-------------------------------|---------------------------|-------------------------|

| Bit size | Adder                | Power (mW) | Area (µm²) | Delay (ns) | PDP (pWSec) |

|----------|----------------------|------------|------------|------------|-------------|

|          | Conventional CSA     | 0.232      | 287.00     | 2.561      | 0.594       |

| 4-Bit    | XOR based CSA        | 0.203      | 283.12     | 2.538      | 0.515       |

|          | Percentage reduction | 12.5%      | 1.35%      | 0.8%       | 13.29%      |

|          | Conventional CSLA    | 0.300      | 580.855    | 2.520      | 0.756       |

| 8-Bit    | XOR based CSA        | 0.250      | 542.485    | 2.487      | 0.622       |

|          | Percentage reduction | 16.67%     | 6.6%       | 1.3%       | 17.72%      |

|          | Conventional CSLA    | 2.803      | 1170.14    | 5.117      | 14.34       |

| 16-Bit   | XOR based CSA        | 2.241      | 1060.01    | 5.014      | 11.24       |

|          | Percentage reduction | 20.04%     | 9.41%      | 2.01%      | 21.62%      |

TABLE II. COMPARISON OF GATE COUNT, IDD MAX AND IDD AVG BETWEEN CONVENTIONAL CSA AND XOR BASED CSA

| Bit size |                      | Gate count |        |        | I <sub>dd</sub> max | I <sub>dd</sub> avg |

|----------|----------------------|------------|--------|--------|---------------------|---------------------|

|          | Adder                | nMOS       | pMOS   | Total  | (mA)                | (mA)                |

| 4-Bit    | Conventional CSA     | 99         | 99     | 198    | 1.679               | 0.193               |

|          | XOR based CSA        | 63         | 63     | 126    | 1.389               | 0.169               |

|          | Percentage reduction | 36.37%     | 36.37% | 36.37% | 17.28%              | 15.54%              |

| 8-Bit    | Conventional CSA     | 195        | 195    | 390    | 2.231               | 0.550               |

|          | XOR based CSA        | 123        | 123    | 246    | 2.132               | 0.459               |

|          | Percentage reduction | 36.93%     | 36.93% | 36.93% | 4.44%               | 16.55%              |

| 16-Bit   | Conventional CSA     | 386        | 386    | 772    | 6.626               | 2.336               |

|          | XOR based CSA        | 243        | 243    | 486    | 5.023               | 2.316               |

|          | Percentage reduction | 37.04%     | 37.04% | 37.04% | 24.19%              | 0.86%               |

TABLE III. COMPARISON WITH OTHER WORK

| Bit size | Parameters | Ref. [5] | This work |

|----------|------------|----------|-----------|

|          | Power (mW) | 13.598   | 0.250     |

| 8-Bit    | Delay(ns)  | 2.094    | 2.487     |

|          | Area (µm²) | 952.343  | 542.485   |

|          | Power (mW) | 29.311   | 2,241     |

| 16-Bit   | Delay (ns) | 2.450    | 5.014     |

|          | Area (µm²) | 1901.093 | 1060.01   |

#### V. CONCLUSION

A 16-bit CSA is implemented in this paper using XOR based 1-bit full adder as a building block. The schematic has been designed in DSCH software and synthesized using 90 nm CMOS technology. The layout has been created and simulated in Microwind software. From the simulation result 20.40% reduction in power consumption, 9.41% reduction in area and 2.01% reduction in delay has been achieved for an XOR-based 16-bit CSA than conventional CSA. Also 37.04% reduction in gate count and 24.19% current reduction were found.

#### **REFERENCES**

- [1] K. Tejasvi1 and G. S. Kishore, "Low-power and area-efficient N-bit carry select adder," International Advanced Research Journal in Science, Engineering and Technology, Vol. 3, Issue 7, pp. 186-189, July 2016.

- [2] P. Balasubramanian, N. E. Mastorakis, "High speed gate level synchronous full adder designs," WSEAS Transactions on Circuits and Systems, Volume 8, Issue 2, pp. 290-300, February 2009.

- [3] R. Uma, V. Vijayan, M. Mohanapriya and S. Paul, "Area, delay and power comparison of adder topologies," International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.1, pp. 153-168, February 2012.

- [4] G. Kaur, L. Kaur and N. Kaur, "Reduced area carry select adder with low power consumptions," International Journal of Emerging Engineering Research and Technology, Volume 3, Issue 3, pp. 90-95, March 2015

- [5] L. Shanigarapu and B. P. Shrivastava, "Low-Power and High Speed Carry Select Adder," International Journal of Scientific and Research Publications, Volume 3, Issue 8,pp.01-09, August 2013.

A Peer Revieved Open Access International Journal

www.ijiemr.org

- [6] Karthik Kumar Vaigandla, Dr.N.Venu, "Survey on Massive MIMO: Technology, Challenges, Opportunities and Benefits," YMER, VOLUME 20: ISSUE 11 (Nov) - 2021, Page No:271-282.

- [7] Karthik Kumar Vaigandla and Dr.N.Venu, "A Survey on Future Generation Wireless Communications - 5G: Multiple Access Techniques, Physical Layer Security, Beamforming Approach", Journal of Information and Computational Science, Volume 11 Issue 9, 2021, pp.449-474.

- [8] Karthik Kumar Vaigandla and Dr.N.Venu, "BER, SNR and PAPR Analysis of OFDMA and SC-FDMA," GIS SCIENCE JOURNAL, ISSN NO: 1869-9391, VOLUME 8, ISSUE 9, 2021, pp.970-977.

- [9] Dr.Nookala Venu, Dr.A.ArunKumar and Karthik Kumar Vaigandla. Review of Internet of Things (IoT) for Future Generation Wireless Communications. International Journal for Modern Trends in Science and Technology 2022, 8(03), pp. 01-08.

- [10] A. V. L. N. Sujith, R. Swathi, R. Venkatasubramanian, Nookala Venu, S. Hemalatha, Tony George, A. Hemlathadhevi, P. Madhu, Alagar Karthick, M. Muhibbullah, Sameh M. Osman, "Integrating Nanomaterial and High-Performance Fuzzy-Based Machine Learning Approach for Green Energy Conversion" Journal of Nanomaterials, ISSN: 1687-4129, Volume 2022, PP:1-11.

- [11] Nookala Venu, D. Yuvaraj, J. Barnabas Paul Glady, Omkar Pattnaik, Gurpreet Singh, Mahesh Singh, and Amsalu Gosu Adigo, "Execution of Multitarget Node Selection Scheme for Target Position Alteration Monitoring in MANET", Wireless Communications and Mobile Computing, ISSN:1530-8669, Volume 2022, PP: 1-9.

- [12] Nookala Venu, R.Swathi, Sanjaya Kumar Sarangi, V. Subashini, D. Arulkumar, Shimpy Ralhan, Baru Debtera, "Optimization of Hello Message Broadcasting Prediction Model for Stability Analysis", Wireless Communications and Mobile Computing, ISSN:1530-8669, Volume 2022, PP: 1-9.

- [13] Nookala Venu, Karthik Kumar Vaigandla, Dr.A.ArunKumar, "Investigations of Internet of Things (IoT): Technologies, Challenges and Applications in healthcare", International Journal of Research (IJR), ISSN: 2236-6124, Volume XI, Issue II, Feb 2022, PP: 143-153.

- [14] Dr. Nookala Venu, "Analysis of Xtrinsic Sense MEMS Sensors" International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering (IJAREEIE), ISSN:2278-8875 Vol 4, Issue:8, August 2015, PP: 7228-7234.

- [15] Nookala Venu, Asiya Sulthana, "Local Mesh Patterns for Medical Image Segmentation" Asian Pacific Journal of Health Sciences (APJHS), e- ISSN: 2349-0659 p-ISSN: 2350-0964, Vol. 5, Issue 1, March 2018, PP: 123-127.

- [16] Dr Nookala Venu, Mrs Asiya Sulthana "Local Maximum Edge Binary Patterns for Medical Image Segmentation, International Journal of Engineering and Techniques (IJET), ISSN: 2395-1303, Volume 4 Issue 1, Jan-Feb 2018, PP: 504-509.

- [17] Dr.N.Venu, Dr.A.Arun Kumar, "Comparison of Traditional Method with watershed threshold segmentation Technique", International Journal of Analytical and Experimental Analysis (IJAEMA),ISSN: 0886-9367, Volume XIII, Issue 1, January- 2021, PP:181-187.

- [18] Karne, RadhaKrishna, and T. K. Sreeja. "ROUTING PROTOCOLS IN VEHICULAR ADHOC NETWORKS (VANETs)." *International Journal of Early Childhood* 14.03: 2022.

- [19] Karne, RadhaKrishna, et al. "Optimization of WSN using Honey Bee Algorithm."

- [20] RadhaKrishna Karne, Dr TK. "COINV-Chances and Obstacles Interpretation to Carry new approaches in the VANET Communications." *Design Engineering* (2021): 10346-10361.

- [21] Karne, RadhaKrishna, et al. "Simulation of ACO for Shortest Path Finding Using NS2." (2021): 12866-12873.

- [22] RadhaKrishna Karne, Dr TK. "Review On Vanet Architecture And Applications." *Turkish Journal of Computer and Mathematics Education* (*TURCOMAT*) 12.4 (2021): 1745-1749.

- [23] Karne, Radha Krishna, et al. "GENETIC ALGORITHM FOR WIRELESS SENSOR NETWORKS."