PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

## COPY RIGHT

2023 IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 10<sup>th</sup> Apr 2023. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-12&issue=Issue 04

## 10.48047/IJIEMR/V12/ISSUE 04/51

Title NOVEL GENERATION OF TOLERANCE OF FAULT NETWORK IN VOLTAGE SOURCE CONVERTER HVDC (VSC-HVDC) TRANSMISSION SYSTEM

Volume 12, ISSUE 04, Pages: 427-436

**Paper Authors**

Mr.A.Naveen Reddy, Soupati Rehan Prakash, Satharajupalli Satyanadh, Peetha Jahnavi,

Shaik Husna

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic Bar Code

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

### Novel Generation of Tolerance of Fault Network in Voltage Source Converter HVDC (VSC-HVDC) Transmission System

**Mr.A.Naveen Reddy**<sup>1</sup>, Assistant Professor, Department of EEE, Vasireddy Venkatadri Institute of Technology, Nambur, Guntur Dt., Andhra Pradesh.

Soupati Rehan Prakash<sup>2</sup>, Satharajupalli Satyanadh<sup>3</sup>, Peetha Jahnavi<sup>4</sup>, Shaik Husna<sup>5</sup> <sup>2,3,4,5,</sup> UG Students, Department of EEE, Vasireddy Venkatadri Institute of Technology, Nambur, Guntur Dt., Andhra Pradesh. soupatirehanprakash@gmail.com<sup>1</sup>, satyanadhsatya@gmail.com<sup>2</sup>, jahnavipeetha@gmail.com<sup>3</sup>, shaikmahaboobjani888@gmail.com<sup>4</sup>

#### ABSTRACT

The aim of this project is to develop a novel generation of High Voltage DC (HVDC) transmission systems that use hybrid multi-level Voltage Source Converters (VSC) and Half Bridge (HB) cells that are AC cascaded. The operating robustness of VSC systems, Auto-Start capacity, active and reactive power regulation and enhanced ability to ride-through ac fault, and during dc side faults, current limiting capability are only a few of the unique features of the HVDC system. A VSC-HVDC has modular multilevel converters has a broader active and reactive power capability curve than one that uses, which primarily results in improved signal quality and a shorter signal channel length (lower footprint). To ac and dc faults a possibility of this HVDC system is its reaction. Dynamic performance is evaluated in steady-state.

**Keywords:** Source Converter of Voltage Modular Multilevel Converter (MMC), hybrid multilevel converter with AC cascaded Half Bridge (HB) cells, High Voltage DC (VSC-HVDC) transmission system.

#### I. INTRODUCTION

Voltage Source Converter has been around for about ten years, and with the rise in demand for clean, pure energy and power transmission, evolved High Voltage DC (VSC-HVDC) transmission systems have many converters, including clamped neutral point converters, two level converters, and multilevel converters, also known as modular multilevel converters (MMCs). This innovation lowers the overall cost of the converter and reduces its footprint, improving the quality of the AC waveform and reducing or eliminating the need for AC filters. When compared to conventional HVDC systems with thyristor current sources, converter transformers have lower semiconductor losses, which reduce voltage stresses and improve the ability of VSC-HVDC transmission systems to manage power as well as the flexibility and dependability of power system networks. A VSC-HVDC transmission system is suitable for poor AC network connections due to its flexible opera-

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

tion, voltage support for AC networks, and independent operation of AC networks. In situations like offshore wind farms, as well as for active Without dc link voltage, power reversal is possible; as a result, the system is resistant to ac side faults and ideal for multi-terminal HVDC networks.

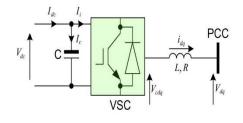

Figure: Representation of VSC station

Unfortunately, it is vulnerable to dc side faults, and the application to point-topoint connections that may operate at high voltage is constrained, which results in the lack of dependable dc circuit breakers. The point of common coupling (PCC) and conversion station control systems' efficient impedance is what enables the existing VSC-HVDC transmission system to ride over dc faults. With this converter advancement, the DC fault current is created by the currents discharged of the DC capacitors and converter's freewheeling diodes. Circuit breakers with high current breaking capacity and brief interruption timings may be needed for the dc fault interruption due to the large let through current that may flow on the dc side during the first few cycles following the fault. The duration and size of the current discharged in first peak are reduced in more recent developments in HVDC converter topologies as the modular multilevel converter (MMC), which do

not utilise common dc link capacitors. The DC fault reverse blocking capacity of the hybrid converter can accomplish the following with coordination between the control functions of HVDC converter station:

- As a result of the VSC-HVDC system's ability to handle DC side faults without the need to open AC side circuit breakers, controlled recovery without interruption is made possible.

- Additionally, the duration and magnitude of dc faults are reduced, simplifying the design of dc circuit breakers, and

- uncontrolled overcurrent during dc faults improves voltage stability in ac networks, lowering the risk of converter failure.

#### **II.PROBLEM IDENTIFICATION**

It can withstand AC defects, Moreover the system is susceptible to DC side failures. To pass through dc faults, this VSC-HVDC transmission system relies on its effective impedance and between the point of common coupling (PCC) and converter station control systems and the converter terminals. The AC networks' contribution to the current converter technology comes from DC side capacitors of the discharge currents and the converter's free-wheeling diodes. Modular multilevel converters (MMC), recent HVDC converter types without common capacitors of DC link, may reduce the discharge current first

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

peak's size and duration. Two techniques are available to help VSC-HVDC transmission systems overcome DC faults. To handle the high DC fault, from the dc side discharge current that may flow, the first method is to utilise a "rapid acting dc circuit breaker" with a sizably high ride through current. This breaker needs to be able to work at high voltages, isolate temporary or permanent dc faults, and break reasonably large currents. Due to the semi-conductors in the main current route, this breaker introduces significant steady state losses. Using "converter stations with dc fault reverse-blocking capability" is the second strategy. Each converter station needs to be able to stop during a dc fault, the flow of current between the ac and dc sides, let the main component of the DC fault current the discharge current from the dc side capacitor decline to zero, and isolation of the fault. A number of converter types are available, such as Half bridge (HB) modular multilevel converter, a hybrid multilevel converter with ac side cascading Hbridge cells and an additional arm modular multilevel converter (MMC). During the dc fault phase, the active power interchange between the AC networks falls to zero, which is a disadvantage. It provides a new HVDC transmission system on a hybrid voltage source multilevel converter with AC cascaded H-bridge cells, similar to the second approach. The converter chosen includes built in DC fault reverse stopping capabilities that can be used to increase VSC resistance HVDC to DC flaws.

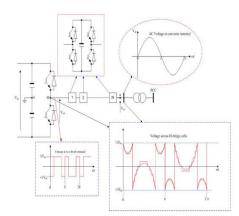

## III. HYBRID MULTILEVEL VSC WITH AC CASCADED H-BRIDGE CELLS

Half bridge cells are used in each phase of a hybrid multilevel VSC. Thus, voltage values converter terminal 'a' in relation to supply midway '0' can be produced. The converter delivers the converter transformer nearly pure sinusoidal voltage. predicted when there are many cells per phase. Selective harmonic reduction with one slot every quarter cycle regulates the fundamental voltage in the two-level converter that limits high voltage. Because of this, the 2 different converter devices operate with flipping losses of 150 Hz. Audible and noise Low switching losses are hence anticipated. By the two-level converter bridge is to reduce the voltage harmonics generated, the Half bridge cells between "M" and "a" are used as a series active power filtering. Level altered signal driven multilayer pulse width modulation (PWM) with a 1-kHz duty cycle is employed to run these Half bridge cells. In order to minimise conversion losses in the H-bridge cells, the cell count might be decreased. This increases the voltage throughout the half-bridge floating capacitors.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

Figure: Hybrid voltage multilevel converter with AC cascaded H-bridge cells.

As a result, converter station is compact since only one-fourth as many H-bridge cells are needed for each converter in the HVDC system than are needed for a system, modular multilevel converter (MMC). An efficient duty cycle per device is possible thanks to the voltage waveform generated between half-bridge cells and the large cell count per phase. Due to the suppression of the control gate signals to the switching state converters, there is no direct link between the AC and DC sides. This allows the HVDC system to block dc fault reverse. As a result, during dc side failures, there is no exchange between active and reactive power in the AC and DC sides since there is no current flow. This linked Half bridge with a dc fault aspect cannot be used. Due to increasing current strains during dc side faults in the switching devices, the ac grid contributes the dc fault current is removed, lowering the chance of converter failure. From the perspective of the grid, The conversion unit link nodes are identified as open - circuit voltage networks for the period of the dc fault by the AC networks and the DC fault counter preventing capability. Yet in order for the hybrid multilevel VSC to function, A voltage order to balance method that ensures the voltages all over the Half Bridge cells are sustained for all operating conditions, with the total dc link voltage in a balanced condition, is required. The effective output method for half-bridge cells cycles the capacitors while taking into account the results of each cell's capacitance and the phase current direction. PI controller keeps the cell capacitors as expected (inner control layer).

#### **IV.METHODOLOGY**

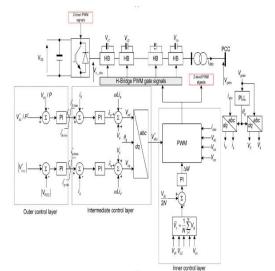

The Three layer control system is necessary for an HVDC transmission system with hybrid multilevel VSC with ac cascaded Half bridge cells. The capacitor voltage balancing mechanism and modulator that produces the converter switches gating signals and preserves Half bridge cell capacitors the voltage balance is represented by the inner layer control system. The intermediate layer regulate supply set points to the current system that regulates voltage (or reactive power) controllers serve as the current controller over the entire working range and limit converter facility current infusion of the active and reactive current components into the ac network during network disruptions like ac and dc side faults, which controllers, make up the outer layer control system. The reader is meant to get a sense. The dc voltage (or active power)

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

and ac e of the intricacy of the HVDC control system from the intermediate and layers. In order to ensure appropriate outer control performance throughout a broad regulating range, includes ac and dc side faults, the simulation final gains employed are the time domain. The test network is used to evaluate the power control and voltage supporting abilities in the steady state changed in. The threephase ac side fault and subjected in the same test network is to a pole to pole dc fault at the locations shown, both for a 140-ms duration, to further demonstrate

Figure: schematic diagram of the control layer of the hybrid multilevel converter

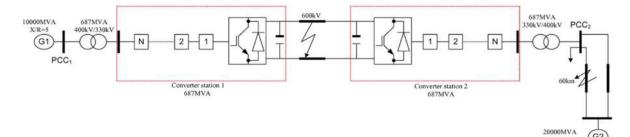

during ac and dc network disturbances the benefits of the hybrid multilevel converter. They represent converter stations 1 and 2. Hybrid VSC versions with the controllers built in and seven cells per phase. When each system component is represented, seven cells are used per arm to achieve appropriate simulation speeds without sacrificing result accuracy. At PCC1 and PCC2, respectively, the converters are set up to control active power changing, and ac voltage magnitudes dc link voltage. The MATLAB Simulink environment is used to simulate the test system.

with AC cascaded Half Bridge cells.

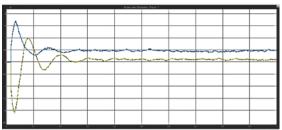

# A. Four-Quadrant Operation and Voltage Support

Converters 1 and 2 exchange active and reactive power, to show that the prepresented VSC-HVDC system can operate in four quadrants and support voltage. It is demonstrated that converter 2 to maintain the voltage magnitude and that converter 2 injects supports its reactive power ex-changes with when the load is at 2s and presents high quality current and voltage waveforms without the use of ac filters. The converters are capable of adjusting and in order to maintain the voltage their reactive power exchange with

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

throughout the entire operating period. And shows that the voltage strains across the converter 1's Half bridge cell capacitors are kept under control and at the correct set point throughout the entire time. This shows the total voltage across converter 2 in DC. VSC-HVDC system can operate in all four quadrants and provide voltage support while still maintaining minimal voltage, current stresses on the converter switches.

#### Current Controller Design:

The differential equations describing the steady-state and ac transient,

$$\frac{di_d}{dt} = -\frac{R}{L}i_d + \frac{1}{L}(V_{cd} - V_d + \omega Li_q)$$

$$\frac{di_q}{dt} = -\frac{R}{L}i_q + \frac{1}{L}(V_{cq} - V_q - \omega Li_d)$$

Assume

$$\begin{split} \lambda_d &= V_{cd} - V_d + \omega L i_q \quad \text{and} \quad \lambda_q = V_{cq} - V_q - \omega L i_d \\ \frac{di_d}{dt} &= -\frac{R}{L} i_d + \frac{1}{L} \lambda_d \\ \frac{di_q}{dt} &= -\frac{R}{L} i_q + \frac{1}{L} \lambda_q. \end{split}$$

The transfer function is derived following State space equations laplace manipulations and is utilised for the present controller design,

$$\frac{i_d(s)}{i_d^*(s)} = \frac{i_q(s)}{i_q^*(s)} = \frac{\frac{K_p}{L}s + \frac{K_i}{L}}{s^2 + \frac{(R+K_p)}{L}s + \frac{K_i}{L}}$$

Expressions for d and q can be used to derive equations that relate the voltages to the modulator and feed forward terms.

$$V_{cd}^* = \lambda_d + V_d - \omega L i_q$$

$$V_{cq}^* = \lambda_q + V_q + \omega L i_d.$$

#### **B. AC Network Faults**

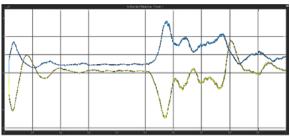

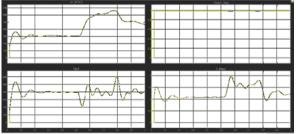

A three-phase fault, pole to ground 140ms is put in to the test network in order to show the provided HVDC system's ability to pass through an ac fault. The power instruction to converter 1 is reduced proportionately to fall in voltage magnitude ac during the fault time. As the voltage at falls power cannot be transferred, this is done to reduce the two-level converter rise in dc link voltage caused by the saved energy in the dc side. Grid undergoes to the three-phase fault and displays the exchanges of converter 1's active and reactive power. To reduce the growth in converter 2's dc link voltage, converter 1 matches its active power export. voltage because it becomes less effective at injecting active power into the grid as the voltage drops. the energies that converter 2 injects, both active and reactive. As soon as the fault is fixed, the system can resume operation, exchange with the grid to support and converter 2 modifies its reactive power voltage. The active and reactive power transients at PCC2 are linked to the response of the ac voltage controller, which controls the ac voltage. As seen, the coordination in the HVDC controllers reduces how much ac-side defects affect on the dc side the transient power flows.

#### AC Voltage Controller:

The AC voltage controller sets the reactive power current component as,

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

$$i_q^* = K_{pv} \left( |V_{ac}^*| - |V_{ac}| \right) + K_{iv} \int \left( |V_{ac}^*| - |V_{ac}| \right) dt$$

| $\frac{P(s)}{V^*} - \frac{i_d(s)}{V^*} - \frac{V^*}{V^*} $                      | $\frac{(K_pK_{pp}+K_iK_{pp}+K_pK_{ip})}{L}s + \frac{K_i}{L}$                                                                                                    |

|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\overline{P^*(s)} = \sqrt[q]{d} \times \overline{P^*(s)} = \sqrt[q]{d} \times$ | $s^{3} + \frac{(R + K_{p} + K_{p}K_{pp}V_{d}^{*})}{L}s^{2} + \frac{(K_{i} + K_{i}K_{pp}V_{d}^{*} + K_{p}K_{ip}V_{d}^{*})}{L}s + \frac{K_{i}K_{ip}V_{d}^{*}}{L}$ |

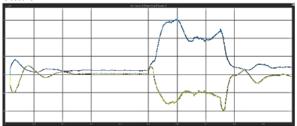

#### **C. DC Network Faults**

Here, it will be shown how the hybrid multilevel VSC with AC cascaded Half bridge cells naturally limits current, allowing the VSC-HVDC system to overcome DC defects. A solid pole to pole dc-side fault lasting 140ms is put-in to test network at the stated location. During the dc fault time the active power replaces in-between the two grids is decreased to zero. Due to channels between the converter's ac and dc the fact that the power sides are blocked (by suppressing all enabling uninterruptable system recovery from it with minimal inrush current converter gate-signals), a grid contributes to the transient dc fault is eliminated. It will be demonstrated how the hybrid multilevel VSC with cascaded Half bridge cells on the ac side naturally controls current, enabling the VSC-HVDC system to get beyond DC side flaws. During the DC fault time, the exchange between active power of the two grids is decreased to zero. Grid contribution to the transient dc fault is eliminated due to the power channels between the converter ac and dc sides being prevented, allowing

uninterruptible system recovery from it with little inrush current. Outcomes when a short time pole to pole fault at the centre of the dc link is applied to the test network. the interchange of reactive and active electricity between converter stations 1 and 2. During the fault time, there is no trading between the converter stations and ac grids active or reactive power, hence there will be no current flowing through the switches of converters 1 and 2. However, in order to restart the system when the gating signals to converters 1 and 2 are restored once the defect is fixed, a significant increase in active and reactive power is seen. During system startup and dc, due to higher use of reactive power, the surge current experienced by both converter stations results in a notable voltage dip at and for fault clearance.

#### DC Voltage Controller:

The converter's dc-side dynamics are

$$C\frac{dv_{\rm dc}}{dt} = I_{\rm dc} - I_i.$$

explained by the differential equation,

where is the voltage of the reference dc link. Thus, the newly introduced control variable for the DC voltage controller should be:

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

$$\begin{bmatrix} \Delta V_{\rm dc}(s) \\ \Delta z_{\rm dc}(s) \end{bmatrix} = \frac{1}{\Gamma} \begin{bmatrix} s & \frac{1}{C} \\ -K_{\rm idc} & s + \left(\frac{K_{\rm pdc}}{C} - \frac{P_{\rm ac}}{CV_{\rm dc}^2}\right) \end{bmatrix} \begin{bmatrix} \frac{K_{\rm pdc}}{C} \\ K_{\rm idc} \end{bmatrix} \Delta V_{\rm dc}^*$$

(23)

where

$$\Gamma = s^{2} + \left(\frac{K_{\rm pdc}}{C} - \frac{P_{\rm ac}}{CV_{\rm dc}^{2}}\right)s + \frac{K_{idc}}{C} \\ \left[\Delta V_{\rm dc}(s)\right] = \begin{bmatrix} \frac{\frac{K_{\rm pdc}}{C}s + \frac{K_{\rm idc}}{C}}{s^{2} + \left(\frac{K_{\rm pdc}}{C} - \frac{P_{\rm ac}}{CV_{\rm dc}^{2}}\right)s + \frac{K_{\rm idc}}{C}} \\ \frac{K_{\rm idc}\left(s - \frac{P_{\rm ac}}{CV_{\rm dc}^{2}}\right)s + \frac{K_{\rm idc}}{C}}{s^{2} + \left(\frac{K_{\rm pdc}}{C} - \frac{P_{\rm ac}}{CV_{\rm dc}^{2}}\right)s + \frac{K_{\rm idc}}{C}} \end{bmatrix} \Delta V_{\rm dc}^{*}.$$

(24)

$$\begin{bmatrix} \frac{di_d}{dt} \\ \frac{dz_d}{dt} \\ \frac{dz_p}{dt} \end{bmatrix} = \begin{bmatrix} -\frac{(R+K_p+K_pK_{pp}V_d^*)}{L} & \frac{1}{L} & \frac{K_p}{L} \\ -(K_i+K_iK_{pp}V_d^*) & 0 & K_i \\ -K_ipV_d^* & 0 & 0 \end{bmatrix} \begin{bmatrix} i_d \\ z_d \\ z_p \end{bmatrix} + \begin{bmatrix} \frac{K_pK_{pp}}{L} \\ K_iK_{pp} \\ K_{ip} \end{bmatrix} P^*$$

Compared to converter 1, which controls active power, converter 2's cell capacitors, which regulate the DC link voltage, undergo a greater voltage dip. Therefore, using a large capacitance minimises the reduction of Half bridge cell capacitor voltages.

#### **V.SIMULATION AND RESULTS**

During Steady State:

Fig(a): Active and Reactive Power at Converter station 1 & 2  $\,$

Fig(b): Voltages at different stages at converter station 1 & 2  $\,$

#### During AC Network Fault:

www.ijiemr.org

Fig(c): Active and Reactive Power at Converter station 1 side

Fig(d): Voltages at different stages at converter station 1

Fig(e): Active and Reactive Power at Converter station 2

Fig(f): Voltages at different stages at converter station 2

Fig(g): Active and Reactive Power at Converter station 1

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

Fig(h): Voltages at different stages at converter station 1

| -d.         | Adda (all failed to sole? 2 |  |  |         |     |      |   |  |

|-------------|-----------------------------|--|--|---------|-----|------|---|--|

|             |                             |  |  |         | L   |      |   |  |

| · · · · · · |                             |  |  |         |     |      |   |  |

|             |                             |  |  |         | 18  |      |   |  |

|             |                             |  |  |         | 10  |      |   |  |

|             |                             |  |  |         | 114 |      |   |  |

|             |                             |  |  |         | 11  |      |   |  |

| I I         |                             |  |  |         | 11  |      |   |  |

|             |                             |  |  |         | 1 k |      |   |  |

|             |                             |  |  |         |     | 200  |   |  |

| -           |                             |  |  |         |     | 0.00 |   |  |

|             |                             |  |  | _       |     |      |   |  |

|             |                             |  |  |         | 111 |      |   |  |

|             |                             |  |  | _       |     |      |   |  |

|             |                             |  |  |         | 117 |      |   |  |

|             |                             |  |  |         | N N |      |   |  |

|             |                             |  |  |         |     |      |   |  |

| I I         |                             |  |  |         | 1   |      |   |  |

| -           | 100                         |  |  | 1941. 0 |     |      | a |  |

$\ensuremath{\text{Fig}(i)}\xspace$  : Active and Reactive Power at Converter station 2

Fig(j): Voltages at different stages at converter station  $2\,$

#### VI.CONCLUSION AND FUTURE SCOPE

This novel generation VSC-HVDC transmission system is built on an ac cascaded multilevel hybrid converter. These are the primary benefits of this HVDC system:

• Perhaps smaller than current HVDC systems in terms of footprint and semi-conductor losses.

• minimal ac side filtering is necessary, and the converter transformer receives high-quality power.

• VSC-HVDC systems benefits, including as its voltage support capabilities, four quadrant operation, and auto-start capability, which is essential for connecting weak AC connections with no generating wind farms.

- Modular designing and handling of converter faults

- able to withstand ac side defects (symmetrical, asymmetrical).

• intrinsic reverse blocking ability of dc fault, which enables converter stations to shut off power to the dc side during faults on the dc side.

More study in the following areas can be done to further this thesis:

The wave effect of traveling can be taken into account when calculating the fault current derivatives of each line in an HVDC system. The protection scheme's effectiveness in HVDC grids with other types of MMCs, such as double clamped MMC (DC-MMC) and cascaded HB-MMC, can be examined, and any necessary adjustments can be made.

#### REFERENCES

[1] G. P. Adam *et al.*, "Network fault tolerant voltage-source-converters for high-voltage applications," in *Proc. 9th IET Int. Conf. AC and DC Power Transmission*, London, U.K., 2010, pp. 1–5.

[2] Y. Zhang *et al.*, "Voltage source converter in high voltage applications: Multilevel versus two-level converters," in *Proc. 9th IET Int. Conf. AC and DC Power Transmission*, London, U.K., 2010, pp. 1–5.

[3] G. P. Adam *et al.*, "Modular multilevel inverter: Pulse width modulation and capacitor balancing technique," *IET Power Electron.*, vol. 3, pp. 702– 715, 2010.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

[4] M. M. C. Merlin *et al.*, "A new hybrid multilevel voltage-source converter with DC fault blocking

capability," in *Proc. 9th IET Int. Conf. AC and DC Power Transmission*, London, U.K., 2010, pp. 1–5.

[5] V. Naumanen *et al.*, "Mitigation of high originated motor overvoltages in multilevel inverter drives," *IET Power Electron.*, vol. 3, pp. 681–689, 2010.

[6] H. Abu-Rub *et al.*, "Medium-voltage multilevel converters: State of the art, challenges, and

requirements in industrial applications," *IEEE Trans. Ind. Electron.*, vol. 57, no. 8, pp. 2581–2596, Aug. 2010.

[7] G. P. Adam *et al.*, "Modular multilevel converter for medium-voltage applications," in *Proc. IEEE Int. Conf. Electr. Mach. Drives Conf.*, 2011, pp. 1013–1018.

[8] G. P. Adam, S. J. Finney, A.M.Massoud, and B.W.Williams, "Capacitor balance issues of the diode-clamped multilevel inverter operated in a quasi-two-state mode," *IEEE Trans. Ind. Electron.*, vol. 55, no. 8, pp. 3088–3099, Aug. 2008.