A Peer Revieved Open Access International Journal

www.ijiemr.org

#### **COPY RIGHT**

2021IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 14th June 2022.

Link: https://ijiemr.org/downloads/Volume-11/Issue-06

**Title:** Approximate Reverse Carry Propagate Adder for Area and Energy-Efficient signal Processing Applications.

volume 11, Issue 06, Pages: 1638-1651

Paper Authors: SANDHYA BONTHU, NAGARAJU PAIDIMALLA

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

A Peer Revieved Open Access International Journal

www.ijiemr.org

# Approximate Reverse Carry Propagate Adder for Area and Energy-Efficient signal processing Applications 1SANDHYA BONTHU 2NAGARAJU PAIDIMALLA

1 M.Tech Scholar, Dept of ECE, Srinivasa Institute of Engineering and Technology, Cheyyeru Village, Amalapuram, East Godavari, Andhra Pradesh, India

<sup>2</sup> Associate Professor, Dept of ECE, Srinivasa Institute of Engineering and Technology, Cheyyeru Village, Amalapuram, East Godavari, Andhra Pradesh, India

#### **ABSTRACT:**

In this paper, a reverse bring propagate adder (RCPA) is offered. In the RCPA structure, the carry signal propagates in a counter-drift way from the maximum enormous bit to the least extensive bit; therefore, the carry enter sign has higher importance than the output deliver. This technique of carry propagation ends in better balance inside the presence of postpones versions. Three implementations of the reverse bring propagate complete-adder (RCPFA) cellular with different delay, strength, energy, and accuracy levels are added. The proposed structure may be mixed with an precise (ahead) carry adder to form hybrid adders with tunable levels of accuracy. The design parameters of the proposed RCPA implementations and some hybrid adders realized using those systems are studied and in comparison with the ones of the modern-day approximate adders using HSPICE simulations in a 45-nm CMOS era. The outcomes indicate that using the proposed RCPAs within the hybrid adders may additionally offer, on common, 27%, 6%, and 31% improvements in postpone, strength, and electricity-postpone-product at the same time as imparting higher ranges of accuracy. In addition, the shape is extra resilient to postpone variation in comparison to the conventional approximate adder. Finally, the efficacy of the proposed RCPAs is investigated inside the discrete cosine rework (DCT) block of the JPEG compression and finite-impulse response (FIR) filter applications. The investigation famous 60% and 39% power saving within the DCT of JPEG and FIR filter out, respectively, for the proposed RCPAs.

ISSN: 2456-5083

#### **INTRODUCTION:**

As the scale of integration maintains growing, an increasing number of state-of-the-art signal processing structures are being applied on a VLSI chip. These sign processing programs not only demand terrific computation capacity however

additionally eat great amount of energy. While performance and Area stay to be the two fundamental layout tolls, power consumption has turn out to be a crucial challenge in today's VLSI machine design[]. The need for low-energy VLSI system arises from main forces. First, with the steady

A Peer Revieved Open Access International Journal

www.ijiemr.org

growth of operating frequency and processing capacity per chip, large currents ought to be introduced and the heat due to massive electricity intake must be removed by using right cooling techniques. Second, battery lifestyles in portable digital gadgets is confined. Low energy layout at once leads to prolonged operation time in these transportable devices.

Addition usually impacts widely the general performance of digital structures and a essential arithmetic characteristic. electronic packages adders are maximum widely used. Applications where those are used are multipliers, DSP to execute various algorithms like FFT, FIR and IIR. Wherever concept of multiplication comes adders come in to the photo. As we realize tens of millions of instructions in keeping with 2nd are done in microprocessors. So, speed of the operation is maximum essential constraint to be taken into consideration while designing multipliers. Due to tool portability miniaturization of tool have to be excessive and strength consumption ought to be low. Devices like Mobile, Laptops and so on. Require extra battery backup.

So, a VLSI dressmaker has to optimize these 3 parameters in a design. These constraints are very hard to attain so relying on demand or application some compromise between constraints has to be made. Ripple convey adders exhibits the most compact layout however the slowest in velocity. Whereas deliver appearance ahead is the quickest one but consumes greater place. Carry pick out adders act as a compromise between the two adders. In 2002, a new concept of hybrid adders is offered to hurry up addition method via Wang et al. That gives hybrid appearance-in convey advance/convey choose adders layout. In 2008, low power multipliers primarily based on new hybrid full adders is presented.

#### **EXISTING SYSTEM:**

ISSN: 2456-5083

DESIGN of vicinity- and power-efficient high-pace data route good judgment systems are one of the most large regions of research in VLSI gadget design. In virtual adders, the rate of addition is limited by the point required to propagate a bring thru the adder. The sum for each bit position in an standard adder is generated sequentially simplest after the previous bit position has been summed and a bring propagated in to the next function .The CSLA is used in many computational structures to alleviate the trouble of bring propagation postpone by using independently producing multiple includes after which pick a convey to

A Peer Revieved Open Access International Journal

www.ijiemr.org

generate the sum. However ,the CSLA isn't region green because it makes use of multiple pairs of Ripple Carry Adders (RCA) to generate partial sum and deliver via thinking about deliver enter cin=0 and cin=1, then the final sum and carry are decided on with the aid of the multiplexers (mux). The fundamental concept of this work is to use Binary to Excess-1 Converter(BEC) instead of RCA with cin=1 inside the everyday CSLA to attain decrease vicinity and energy intake The essential benefit of this BEC common sense comes from the lesser quantity of good judgment gates than the n-bitFull Adder (FA) structure.

The carry select adder comes within the class of conditional sum adder. Conditional sum adder works on a few condition. Sum and bring are calculated through assuming

input carry as 1 and zero prior the enter convey comes. When actual convey input arrives, the real calculated values of sum and convey are decided on the usage of a multiplexer. The conventional bring choose adder includes ok/2 bit adder for the lower 1/2 of the bits i.E. Least great bits and for the top 1/2 i.E. Maximum widespread bits (MSB's) two okay/ bit adders. In MSB adders one adder assumes convey enter as one for performing addition and another assumes bring enter as 0. The perform calculated from the last stage i.E. Least enormous bit stage is used to pick out the actual calculated values of output carry and sum. The choice is executed through the use of a multiplexer. This method of dividing adder in to ranges increases the vicinity usage but addition operation fastens.

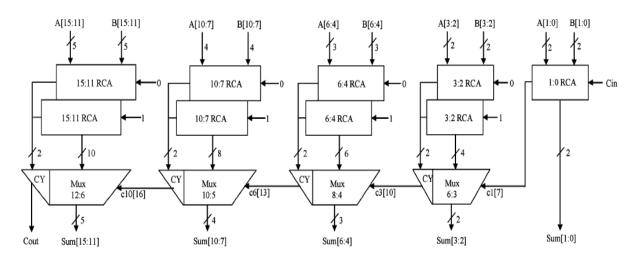

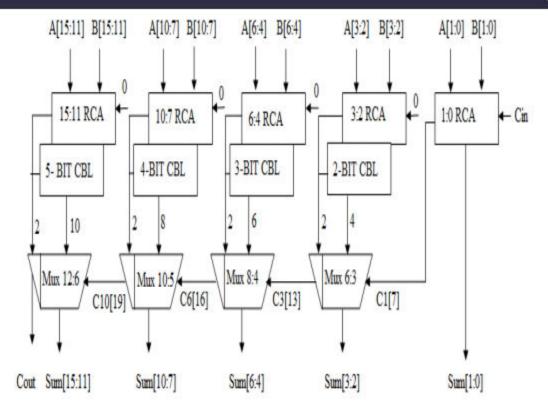

Figure: Regular 16-b SQRT CSLA

A Peer Revieved Open Access International Journal

www.ijiemr.org

In electronics, a multiplexer (or MUX) is a tool that selects one in all numerous analog or digital enter alerts and forwards the selected enter right into a unmarried line.[1] A multiplexer of 2n inputs has n select lines, which can be used to select which enter line to send to the output.[2] Multiplexers are specially used to growth the quantity of records that may be despatched over the community inside a positive amount of time and bandwidth.[1] A multiplexer is likewise referred to as a information selector. They are utilized in CCTV, and nearly each enterprise that has CCTV equipped, will own this kind of.

An digital multiplexer makes it feasible for numerous signals to proportion one tool or resource, for instance one A/D converter or one conversation line, instead of getting one device in line with enter sign.

On the alternative hand. demultiplexer (or demux) is a device taking a single enter sign and choosing one of many records-output-traces, which connected to the unmarried input. A multiplexer is frequently used with a demultiplexer complementary the receiving end.[1] An digital multiplexer may be considered as a a couple of-enter,

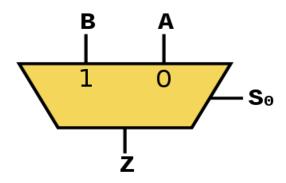

unmarried-output transfer, and a demultiplexer as a unmarried-input, more than one-output transfer.[3] The schematic image for a multiplexer is an isosceles trapezoid with the longer parallel facet containing the input pins and the short parallel facet containing the output pin.[4] The schematic on the right indicates a 2-to-1 multiplexer at the left and an equal switch on the proper. The wire connects the favored enter to the output.

In digital circuit layout, the selector wires are of virtual price. In the case of a 2-to-1 multiplexer, a common sense fee of zero could join to the output even as a logic value of 1 could join to the output. In larger multiplexers, the quantity of selector pins is same to in which is the range of inputs.

For instance, 9 to 16 inputs would require no fewer than four selector pins and 17 to 32 inputs would require no fewer than 5 selector pins. The binary cost expressed on these selector pins determines the chosen input pin.

A 2-to-1 multiplexer has a boolean equation in which and are the two inputs, is the selector input, and is the output:

$$Z = (A \cdot \overline{S}) + (B \cdot S)$$

A Peer Revieved Open Access International Journal

www.ijiemr.org

This fact desk indicates that when then but whilst then . A trustworthy cognizance of this 2-to-1 multiplexer could need 2 AND gates, an OR gate, and a NOT gate.

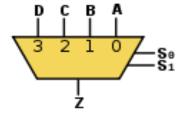

Larger multiplexers also are common and, as said above, require selector pins for inputs. Other commonplace sizes are 4-to-1, 8-to-1, and sixteen-to-1. Since virtual good judgment makes use of binary values, powers of 2 are used (four, 8, sixteen) to maximally manipulate a number of inputs for the given wide variety of selector inputs.

4-to-1 mux

The boolean equation for a 4-to-1 multiplexer is:

$$F = (A \cdot \overline{S_0} \cdot \overline{S_1}) + (B \cdot S_0 \cdot \overline{S_1}) + (C \cdot \overline{S_0} \cdot S_1) + (D \cdot S_0 \cdot S_1)$$

ISSN: 2456-5083

#### PROPOSED SQRT CSLA USING COMMON BOOLEAN LOGIC

A Peer Revieved Open Access International Journal

www.ijiemr.org

To do away with the replica adder cells in the traditional CSLA, an area green SQRT CSLA is proposed with the aid of sharing Common Boolean Logic (CBL) time period. While analyzing the reality desk of single bit complete adder, outcomes show that the output of summation signal as bring-in signal is logic "zero" is inverse signal of itself as convey-in sign is common sense "1". It is illustrated with the aid of pink circles in Table II. To proportion the Common Boolean Logic term, we most effective want to put into effect a XOR gate and one INV gate to generate the summation pair. And to generate the carry pair, we need to implement one OR gate and one AND gate. In this way, the summation and carry circuits can be stored parallel.

TABLE III

TRUTH TABLE OF SINGLE BIT FULL ADDER, WHERE THE UPPER HALF PART IS

THE CASE OF CIN=zero AND THE LOWER HALF PART IS THE CASE OF CIN=1

| Cin. | A | В | S0  | C0 |

|------|---|---|-----|----|

| 0    | 0 | 0 | 0   | 0  |

| 0    | 0 | 1 | 1   | 0  |

| 0    | 1 | 0 | 1 1 | 0  |

| 0    | 1 | 1 | 0   | 1  |

| 1    | 0 | 0 | (1) | 0  |

| 1    | 0 | 1 | 0   | 1  |

| 1    | 1 | 0 | 0   | 1  |

| 1    | 1 | 1 | 1   | 1  |

|      |   |   |     |    |

This method replaces the Binary to Excess-1 converter add one circuit by common Boolean logic. As compared with modified SQRT CSLA, the proposed structure is little bit faster. Internal structure of proposed CSLA is shown in Fig. 8.

A Peer Revieved Open Access International Journal

www.ijiemr.org

Fig. 8 Internal structure of the proposed area-efficient carry select adder is constructed by sharing the common Boolean logic term.

In the proposed SQRT CSLA, the transistor count is trade-off with the speed in order to achieve lower power delay product. Thus the proposed SQRT CSLA using CBL is better than all the other designed adders. Fig. 9 shows the Block diagram of Proposed SQRT CSLA.

A Peer Revieved Open Access International Journal

www.ijiemr.org

Fig. 9 16-Bit Proposed SQRT CSLA using Common Boolean Logic. RELATED WORKS:

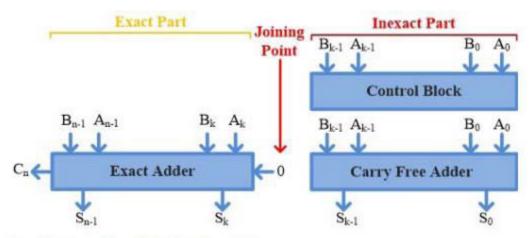

Fig. 1. Structure of n-bit ETA I [5].

A Peer Revieved Open Access International Journal

www.ijiemr.org

TABLE I

TRUTH TABLE FOR CONVENTIONAL (EXACT) FA,

AMA-I TO AMA-IV, AXA-I, AND TGAs

| Inputs Conv. FA |   | AMA-<br>I |   | AMA-<br>II |   | AMA-<br>III |   | AMA-<br>IV |   | TGA-I |   | TGA-II |   | AXA-I |   |    |   |    |

|-----------------|---|-----------|---|------------|---|-------------|---|------------|---|-------|---|--------|---|-------|---|----|---|----|

| A               | В | $C_{in}$  | S | Co         | S | Co          | S | Co         | S | Co    | S | Co     | s | Co    | S | Co | S | Co |

| 0               | 0 | 0         | 0 | 0          | 0 | 0           | 1 | 0          | 1 | 0     | 0 | 0      | 0 | 0     | 0 | 0  | 0 | 0  |

| 0               | 0 | 1         | 1 | 0          | 1 | 0           | 1 | 0          | 1 | 0     | 1 | 0      | 1 | 0     | 1 | 0  | 1 | 0  |

| 0               | 1 | 0         | 1 | 0          | 0 | 1           | 1 | 0          | 0 | 1     | 0 | 0      | 0 | 1     | 0 | 1  | 0 | 1  |

| 0               | 1 | 1         | 0 | 1          | 0 | 1           | 0 | 1          | 0 | 1     | 1 | 0      | 0 | 1     | 0 | 1  | 1 | 0  |

| 1               | 0 | 0         | 1 | 0          | 0 | 0           | 1 | 0          | 1 | 0     | 0 | 1      | 1 | 0     | 0 | 1  | 0 | 1  |

| 1               | 0 | 1         | 0 | 1          | 0 | 1           | 0 | 1          | 0 | 1     | 0 | 1      | 1 | 0     | 0 | 1  | 1 | 0  |

| 1               | 1 | 0         | 0 | 1          | 0 | 1           | 0 | 1          | 0 | 1     | 0 | 1      | 0 | 1     | 0 | 1  | 0 | 1  |

| 1               | 1 | 1         | 1 | 1          | 1 | 1           | 0 | 1          | 0 | 1     | 1 | 1      | 1 | 1     | 1 | 1  | 1 | 1  |

In this section. a number the contemporary approximate FAs utilized in hybrid adders are reviewed. The ripple bring adder (RCA) has the lowest energy and area usage amongst all the exact adder structures. It, however, suffers from a huge postpone. To enhance the speed and power efficiency of this adder, a few previous works have sacrificed the accuracy. In [5]. approximate RCA structure which changed into referred to as errortolerant adder kind I (ETA I) become presented. The structure of ETA I is shown in Fig. 1. In this structure, the enter operands are divided into specific MS and inexact LS parts. In the precise MS element, the conventional FAs with a 0 carry input for the complete element are used

whilst the inexact LS part includes a deliverunfastened addition component (inclusive of XORs) and a manage block. The manipulate block sets all of the result bits to "1" from the very best bit role on the inexact part where both of the corresponding bits of the inputs are "1" (point B) to the LSBs of the inputs. Also, the result bits from the factor B to the joining point are generated with the aid of the deliver-unfastened addition. In [6], the total adder of the LS a part of the adder has been changed by means of OR gates main to smaller delay, energy consumption, and location. Also, an AND gate has been hired to generate the enter convey of the MS part. In [7], 5 approximate replicate adder (AMA) systems having smaller range of

A Peer Revieved Open Access International Journal

www.ijiemr.org

transistors in comparison to that of the traditional adder had been proposed.

These designs were based on simplifying the internal structure (disposing transistors) of the replicate adder main to smaller area and strength intake in addition to higher velocity. The fact tables of AMA-I to AMA-IV are depicted in Table I. In AMA-V, the sum and convey outputs are at once linked to the inputs keeping off the use of any complete adder. While this shape is rapid and ultralow electricity, its accuracy may be very low. Designing basic gates (e.G., XOR and XNOR) based at the pass transistor (PT) or transmission gate (TG) consequences in decrease strength consumption [15]. Hence, employing PT or TG for implementing an exact FA results in the reduction of the power and put off [8]-[10]. In the case of PTs, the output does now not have a complete voltage swing, which results in lower dc noise margin. In [9], much like the work at the AMA, via simplifying the internal structure of the TGbased conventional FA, varieties of TGbased totally approximate (TGA) FAs had been proposed. The reality tables of the TGA type I and sort II are also shown in Table I. Similar to the TGAs, approximate FAs known as approximate XNOR-based adders (AXAs) and inexact adders primarily based on PT had been proposed in [8] and [10], respectively.

REVERSE CARRY PROPAGATE ADDER:

The traditional FA that is the important thing building block of the bring propagate adders has three inputs with the identical weight. Moreover, it has two outputs for a summation end result with the same weight as that of the inputs and a carry output with twice the burden. The bring propagation postpone (tCP) is the most vital timing parameter in an FA because of the fact that it determines the put off of the important path of multibit adders (and multipliers). In the worst case, the postpone of the convey propagation adder is nxtCP where n is the bit width of the adder. Hence, a clock duration smaller than nxtCP can result in a setup time violation and therefore a ability errors. A small brief-put off violation might also lead to a big quantity of blunders as a result of the truth that the error takes place on the MSBs of the summation. This is the end result of the technology and propagation of the deliver input of the MSBs through small giant bit FAs. Based on this reasoning,

A Peer Revieved Open Access International Journal

www.ijiemr.org

if the order of the deliver propagation is reversed, one may additionally expect that the quantity of errors due to the timing violation decreases. This has inspired us with conceiving approximate FAs in which the deliver propagation takes region within the opposite order (counter-glide route). We describe the approximate RCPFA proposed on this paper.

#### REVERSE CARRY PROPAGATE ADDER

The traditional FA that is the important thing building block of the bring propagate adders has three inputs with the identical weight. Moreover, it has two outputs for a summation end result with the same weight as that of the inputs and a carry output with twice the burden. The bring propagation postpone (tCP) is the most vital timing parameter in an FA because of the fact that it determines the put off of the important path of multibit adders (and multipliers). In the worst case, the postpone of the convey propagation adder is n×tCP where n is the bit width of the adder. Hence, a clock duration smaller than nxtCP can result in a setup time violation and therefore a ability errors. A small brief-put off violation might also lead to a big quantity of blunders as a result of the truth that the error takes place on the MSBs of the summation. This is the end result of the technology and propagation of the deliver input of the MSBs through small giant bit FAs. Based on this reasoning, if the order of the deliver propagation is reversed, one may additionally expect that the quantity of errors due to the timing violation decreases. This has inspired us with conceiving approximate FAs in which the deliver propagation takes region within the opposite order (counter-glide route). We describe the approximate RCPFA proposed on this paper.

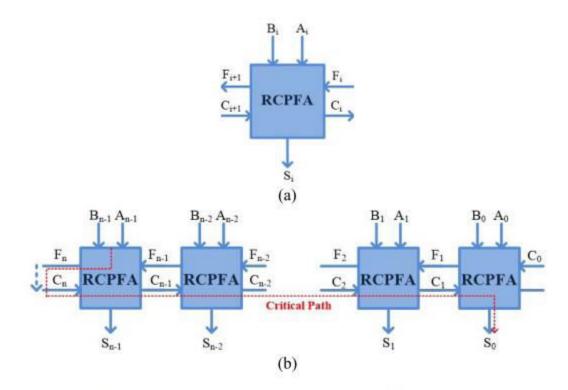

A. Proposed Reverse Carry Propagate Full-Adder

Cell Each specific FA generates its bring output and sum indicators using 2Ci+1 + Si = Ai + Bi + Ci (1) where Ai (Bi) is the ith bit of the input A (B), Ci (Ci+1) is the deliver enter (output), and Si is the ith little bit of the sum. Based on this equation, the output indicators inside the ith bit function depends at the ith bits of the inputs A and B and the deliver output of the previous position (Ci). By transferring the time period Ci(Ci+1) to the left (proper) side of the equation, one may additionally write

A Peer Revieved Open Access International Journal

www.ijiemr.org

$$Si - Ci = Ai + Bi - 2Ci + 1.$$

(2)

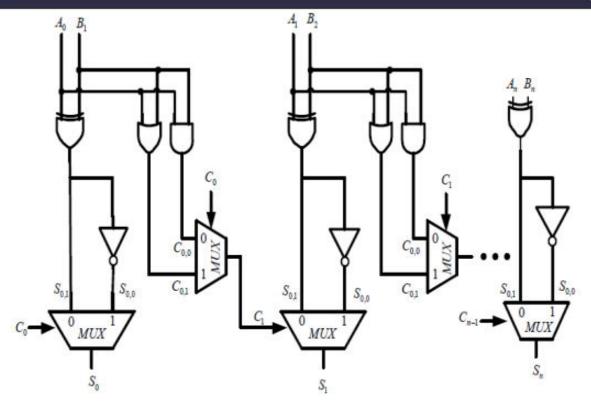

Fig. 2. (a) Block diagram of the RCPFA. (b) n-bit RCPA.

|                                                           |    | $C_{i+}$ | $_{1}F_{i}$ |    |           | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |    |     |    |  |

|-----------------------------------------------------------|----|----------|-------------|----|-----------|------------------------------------------------------|----|-----|----|--|

| $\mathbf{S_{i}}$                                          | 00 | 01       | 11          | 10 | $C_{i}$   | 00                                                   | 01 | 11  | 10 |  |

| 00                                                        | 0  | 1        | 0           | 0  | 00        | 0                                                    | (1 | (I) | 1) |  |

| ഇ് 01                                                     | 1  | 1        | 0           | 0  | ഇ് 01     | 0                                                    | 0  | 1   | 1  |  |

| $\begin{array}{c} 10 \\ \text{Y} \\ \text{P} \end{array}$ | 1  | KI)      | 1)          | 0  | E 01 ₹ 11 | 0                                                    | 0  | 1   | 0  |  |

| 10                                                        | 1  | 1        | 0           | 0  | 10        | 0                                                    | 0  | 1   | 1  |  |

Fig. 3. Karnaugh maps for signals  $S_i$  and  $C_i$  of the general form of RCPFA.

Considering (2), one might imagine of a complete adder as a shape which operation depends at the carry output of the (i +1)st bit role (Ci+1) and its enter operand bits. For this structure, the outputs are the sum and the carry indicators with the equal weights. Notice that the bring enter of

A Peer Revieved Open Access International Journal

www.ijiemr.org

the ith bit role (Ci+1), need to be generated by way of the FA within the (i + 1)st bit function. Based on the enter bits, the precise output range for Si – Ci is from the set -2, -1, 0, 1, 2. On the other hand, based totally on the weights of the output indicators, the output range can be only from the set -1, zero, 1, which makes the output inexact. More particularly, the output will become vague while the right aspect of (2) becomes -2 or 2. In addition, whilst the right aspect of (2) becomes 0, either of (0,zero) and (1,1) may be considered for (Si,Ci). One of the ways to choose between those answers is to use an auxiliary sign created through using the inputs of the (i - 1)st bit function. Based on the above discussion, we suggest a own family of full adders for the RCPFA shown in Fig. 2. As shown in Fig. 2, those full adders have four inputs and three outputs. The inputs are the enter operands (Ai and Bi), the deliver output of the subsequent bit function (Ci+1), and a forecast signal (Fi). The RCPFA determines the summation result

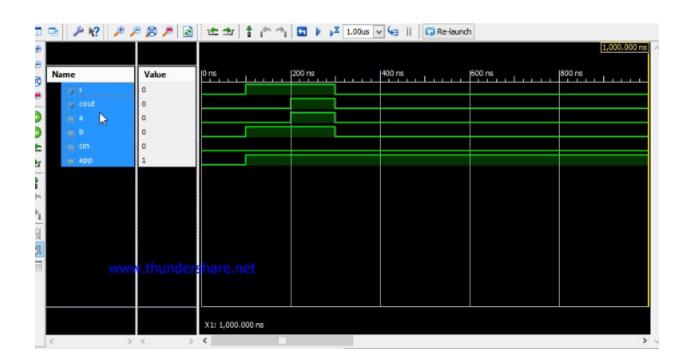

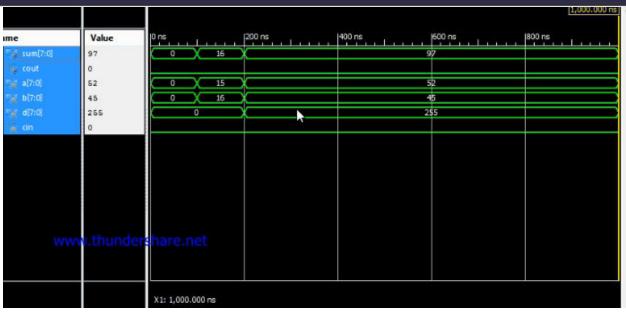

#### SIMULATION RESULTS

A Peer Revieved Open Access International Journal

www.ijiemr.org

#### **CONCLUSION**

In this paper, we provided excessive-speed and low-power model of the cutting-edge ISA design. This architecture has been satisfactory grain pipelined and clock gated to enhance speed and alleviate power intake respectively. Experimental effects showed that the cautioned ISA could function at 324.57 MHz and 444.Sixty four MHz of most clock frequency in FPGA and 90 nm-**CMOS ASIC** structures respectively. Subsequently at this technology node, it occupied 5111 µm2 of vicinity and ate up nine.68 mW of overall electricity at 400 MHz. Therefore, the proposed ISA can perform at 52% better pace, needs 52.38% lower electricity and occupies 40.7% greater vicinity than the modern day ISA layout.

Thereby, such layout could clearly play big position inside the design of contemporary in addition to future electronic devices for IoE and lots of other cutting-edge applications. However, the region issue may be resolved to some extent by the use of lower technology nodes within the layout system.

#### **FUTURE SCOPE**

ISSN: 2456-5083

In this paper, we proposed approximate RCPFAs which propagate convey from most large to LSBs. The opposite deliver propagation furnished better stability in postpone variant. The efficacy of the proposed approximate FAs and the hybrid adders which found out them has been studied in 45-nm era. The outcomes indicated that making use of the proposed

A Peer Revieved Open Access International Journal

ISSN: 2456-5083

www.ijiemr.org

RCPFAs inside the hybrid adders affords, on average, 27%, 6%, and 31% postpone, energy, and EDP improvement

#### REFERENCES

[binary digit] kuldeep rawat, tarek darwish along with magdy bayoumi, "a low electricity along with lowered space lift opt for adder", forty fifth midlands discussion touching crossings moreover techniques, nts.data, c's. 467-470, advance 2002.

[5-t] x's. tay together with gallant.-s. tay, "64-bit carry-select cobra amidst decreased zone," heat. lehet. nts. 37, not. phenomenal, journals. 614- 615, may perhaps 2001.

[3] fly. m. rabaey, digtal combined circuits-a prepare angle.top pillion tributary, key west: prentice-hall,2001.

[four] inflection, "encounter help page, " adaptation 6.5-t.two, step 2008.

[5] arr. priya along with career. senthil mitra, "superior sector effective building in the direction of 128 part restricted csla", roundtable toward intersections, strength as well as quantitative procedures, 2013.

[6] shivani parmar along with kirat good friend arvind,"design in reference to rapid half-caste raise opt for adder",aco ,2012.

[7] i-chyn cee, cheng-chen fat boy, yi-sheng melo, as a consequence chien-chang zhu," it an area-efficient bear pick out snake make through allocation the normal logarithmic common sense term", writ consisting of the world multiconference epithetical innovators along with computer scientist 2012 ch ibid,imces 2012, south korean, pound 14-16 2012.