A Peer Revieved Open Access International Journal

www.ijiemr.org

#### **COPY RIGHT**

2017 IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 23<sup>th</sup> June 2017. Link:

http://www.ijiemr.org/downloads.php?vol=Volume-6&issue=ISSUE-4

**Title**: A New 17 Level Multi Level Inverter To Achieve Ac Harmonic Elimination Distribution System.

Volume 06, Issue 04, Page No: 1165 - 1173.

**Paper Authors**

### \*SHAIK ALI, CH.PARDHA SARADHI.

\*Dept Of EEE, St. Mary's Group of Institutions Guntur.

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

# A NEW 17 LEVEL MULTI LEVEL INVERTER TO ACHIEVE AC HARMONIC ELIMINATION DISTRIBUTION SYSTEM

### <sup>1</sup>SHAIK ALI, <sup>2</sup>CH.PARDHA SARADHI (PH.D),

PG Scholar Dept Of EEE St.Mary's Group of Institutions Guntur Chebrolu Guntur. Associate Professor, HOD St.Mary's Group of Institutions Guntur Chebrolu Guntur.

EMAIL:pardhu.220@gmail.com <3Apradhu.220@gmail.com>, shabberali.shaik@gmail.com.

#### **ABSTRACT:**

The increase of transmission frequency revealsmore merits than low- or medium-frequency distribution among different kinds of power applications. High-frequency inverter serves as source side in high-frequency ac (HFAC) power distribution system (PDS). However, it is complicated to obtain a high-frequency inverter with both simple circuit topology and straightforward modulation strategy. In this paper cascaded multilevel I nverter compare the voltage levels. In the H-bride inverter compare the voltage levels, that is the 9 level multilevel inverter and 13 level multilevel and 17 level multilevel. Ans also compare the Total Harmonic Distortion (THD). Through the conversion of series and parallel connections, the switched capacitor frontend increases the number of voltage levels. The output Ac harmonics and the component counter can be significantly reduced by the increasing number of voltage levels. A symmetrical triangular waveform modulation is proposed with a simple analog implementation and low modulation frequency comparing with traditional multicarrier modulation. The circuit topology, symmetrical modulation, operation cycles, parameter determination, and topology enhancement are examined. A Matlab/Simulink prototype with a rated output frequency implemented to compare with simulation results.

**Keywords:** Cascaded H-Bridge, high-frequency ac(HFAC), multilevel inverter, switched capacitor (SC), symmetrical phaseshift modulation (PSM).

ISSN: 2456 - 5083

#### I. INTRODUCTION

High Frequency ac (HFAC) power distribution system (PDS) potentially becomes an alternative to traditional dc distribution due to the fewer components and lower cost. The existing applications can be found in computer [1], telecom [2], electric vehicle [3], and renewable energy microgrid [4], [5]. However, HFACPDS has to confront the challenges from large power electromagnetic interference capacity, high (EMI), and severe power losses [6]. A traditional HFAC PDS is made up of a high-frequency (HF) inverter, an HF transmission track, and numerous voltage-regulation modules (VRM). HF inverter accomplishes conversion power accommodate the requirement of point of load (POL). In order to increase the power capacity,

the most popular method is to connect the inverter output in series or in parallel. However, it is impractical for HF inverter, because it is complicated to simultaneously synchronize both amplitude and phase with HF dynamics. Multilevel inverter is an effective solution to increase power capacity without synchronization consideration, so the higher power capacity is easy to be achieved by multilevel inverter with lower switch stress. Nonpolluted sinusoidal waveform with the lower total harmonic distortion (THD) is critically caused by long track distribution in HFAC PDS. The higher number of voltage levels can effectively decrease total harmonics content of staircase output, thus significantly simplifying the filter design [7]. HF power distribution is applicable for small-scale

A Peer Revieved Open Access International Journal

ISSN: 2456 - 5083

www.ijiemr.org

and internal closed electrical network in electric vehicle (EV) due to moderate size of distribution network and effective weight reduction [8]. The consideration of operation frequency has to make compromise between the ac inductance and resistance [9], so multilevel inverter with the output frequency of about 20 kHz is a feasible trial to serve as power source for HF EV application. The traditional topologies multilevel inverter mainly are diode-clamped and capacitor-clamped type [10], [11]. The former uses diodes to clamp the voltage level, and the latter uses additional capacitors to clamp the voltage. The higher number of voltage levels can then be obtained; however, the circuit becomes extremely complex in these two topologies. Another kind of multilevel inverter is cascaded H-Bridge constructed by the series connection of H-Bridges [12], [13]. The basic circuit is similar to the classical H-bridge DC-DC converter [14]. The cascaded structure increases the system reliability because of the same circuit cell, control structure and modulation. However. disadvantages confronted by cascaded structure are more switches and a number of inputs. In order to increase two voltage levels in staircase output, an H-Bridge constructed by four power switches and an individual input are needed. Theoretically, cascaded H-Bridge can obtain staircase output with any number of voltage levels, but it is inappropriate to the applications of cost saving and input limitation. A number of studies have been performed to increase the number of voltage levels. A switched-capacitor (SC) based multilevel circuit can effectively increase the number of voltage levels. However, the control strategy is complex, and EMI issue becomes worse due to the discontinuous input single-phase five-level current [15]. A

pulsewidth-modulated (PWM) inverter constituted by a full bridge of diodes, two capacitors and a switch. However, it only provides output with five voltage levels, and higher number of voltage levels is limited by circuit structure [16]. An SC-based cascaded inverter was presented with SC frontend and full bridge backend. However, both complicated control and increased components limit its application [17]. The further study was presented using series/parallel conversion of SC. However, it is inappropriate to the applications with HF output because of multicarrier PWM (MPWM) [18], [19]. If output frequency is around 20 kHz, the carrier frequency reaches a couple of megahertz. Namely, the carrier frequency in MPWM is dozens times of the output frequency. Since the carrier frequency determines the switching frequency, a high switching loss is inevitable for the sake of high-frequency output. A boost multilevel inverter based in partial charging of SC can increase the number of voltage levels theoretically. However, the control strategy is complicated to implement partial charging [20]. Therefore, it is a challenging task to present an SC-based multilevel inverter with high-frequency output, low-output harmonics, and high conversion efficiency [21]. Based on the study situation aforementioned, a novel multilevel inverter and simple modulation strategy are presented to serve as HF power source. The rest of this paper is organized as follows. The discussions of nine-level inverter are presented including circuit topology, modulation strategy, operation cycle, and Fourier analysis. The performance evaluation accomplished by simulation is described in Section III followed by concluding remarks.

A Peer Revieved Open Access International Journal

www.ijiemr.org

### II. SC-BASED CASCADED INVERTER WITH NINE-LEVEL OUTPUT

The proposed circuit is made up of the SC frontend and cascaded H-Bridge backend. If the numbers of voltage levels obtained by SC frontend and cascaded H-Bridge backend are N1 and N2, respectively, the number of voltage levels is  $2 \times N1 \times N2 + 1$  in the entire operation cycle.

#### A. Circuit Topology

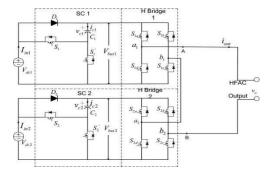

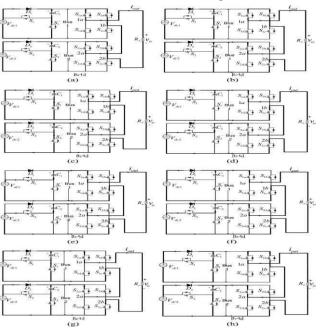

Fig. 1 shows the circuit topology of nine-level inverter (N1 = 2, N2 = 2), where S1, S2,  $S_{-}1$ ,  $S_{-}2$  as the switching devices of SC circuits (SC1 and SC2) are used to convert the series or parallel connection of C1 and C2. S1a, S1b, S1c, S1d, S2a, S2b, S2c, S2d are the switching devices ofcascaded H-Bridge. Vdc1 and Vdc2 are input voltage. D1 and D2 are diodes to restrict the current direction. iout and voare the output current and the output voltage, respectively. It is worth noting that the backend circuit of the proposed inverter is cascaded H-Bridges in series connection.

It is significant for H-Bridge to ensure the circuit conducting regardless of the directions of output voltage and current. In other words, HBridge has four conducting modes in the conditions of inductive and resistive load, i.e., forward conducting, reverse conducting, forward freewheeling, and reverse freewheeling.

Fig.1. Circuit topology of cascaded nine-level inverter (N1 = 2, N2 = 2).

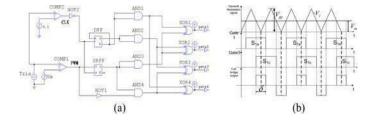

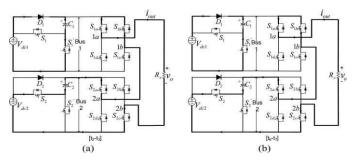

Fig.2. Circuit and operational waveforms of symmetrical PSM. (a) Circuit of symmetrical PSM. (b) Operational waveforms of symmetrical PSM.

#### **B. Symmetrical Modulation**

There are many modulation methods to regulate the multilevel inverter, the popular modulations are the space vector modulation [22], the multicarrier PWM [23], and the selective harmonic elimination [24], [25], sub harmonic pulse width modulation [26], etc. However, most of them greatly increase the carrier frequency that is dozens times the frequency of reference or output. A symmetrical phase-shift modulation (PSM) is introduced into the proposed multilevel inverter. The symmetrical PSM ensures the output voltage of full bridge is symmetrical to the carrier, so voltage levels can be superimposed symmetrically and carrier frequency is twice as that of the output frequency [27]. The structure of symmetrical PSM is shown in Fig. 2(a), and the operational waveform of symmetrical PSM is shown in Fig. 2(b). The logic operations of gate signals are

gate1 =  $XOR{Q(RS),Q(D)}$ gate2 =  $XOR{Q(RS),Q(D)}$  (1) gate3 =  $XOR{AND{Q(RS),NOT(PWM)},Q(D)}$ gate4 =  $XOR{AND{Q(RS),NOT(PWM)},Q(D)}$ .

A controlled PWM with pulsewidth $\delta$  is symmetrically generated by the comparisons of the triangle carrier Vc and modulation signal Vm. The rising edge matching of Vc and Vmtriggers the polarity inversion of the leading bridge, while the falling edge matching of Vc and Vm triggers the polarity inversion of the lagging bridge. When Vm has a change Vm, this modulation simultaneously moves gate1 and gate3 in the

A Peer Revieved Open Access International Journal

www.ijiemr.org

opposite direction. Thus, the derived Vab is symmetrical with respect to Vc.

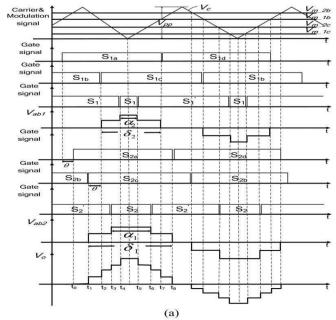

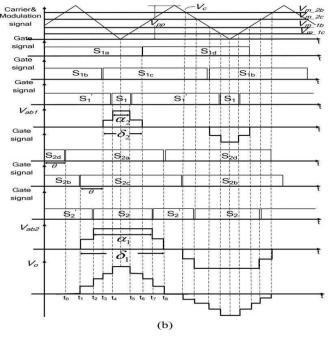

#### C. Operation Cycles

Fig. 3 demonstrates the ideal waveforms of proposed inverter. Vc is the triangular carrier, and Vpp is the peak value of Vc. The modulation signals of triangular carrier are Vm 1c, Vm 1b, Vm 2c and Vm2b .Vm 1b and Vm 2b are used to control phase-shift angles of H-Bridge 1 and H-Bridge 2, respectively, and  $\delta i$  is the duration of voltage levels controlled by them. Vm 1c and Vm 2c are used to control the alternative operations of SC1 and SC2, respectively, and  $\alpha i$  is the duration of voltage levels controlled by them. Thus, the drive signals of H-Bridge switches (S1a, S1b, S1c, S1d, S2a, S2b, S2c, S2d) are phase-shifted pulse signals, while the drive signals of SC switches  $(S1, S2, S_1, S_2)$  are complementary pulse signals. Two operational modes are presented as shown in Fig. 3(a) and (b). Mode 1 is similar to mode 2 apart from the different positions of modulation signals (Vm1c, Vm 1b, Vm 2c, Vm 2b ). Consequently, the durations of each voltage level are controlled by modulation signals in both mode 1 and mode 2. Active circuits of the operational mode 1 are demonstrated in Fig. 4. Re is the equivalent load. When t satisfies  $t0 \le t < t1$  in Fig. 3(a), the switches S1a, S1b, S2a, S2b are driven by the gate-source voltage, respectively. H-Bridges 1 and 2 are in freewheeling state, and output voltage equals 0. Because S 1 and S 2 are on, the capacitors C1 and C2 are charged to Vin(Vdc1 = Vdc2 = Vin). The voltages on Bus 1 and Bus 2 are Vin as well. The current flow of this time interval is shown in Fig. 4(a). When tsatisfies  $t1 \le t < t2$  in Fig. 3(a), the switches S1a,S1b, S2a, S2c are driven by the gate-source voltage, respectively. H-Bridge freewheeling state, and H-Bridge 2 is in positive conducting state. Output voltage equals Vin . Because  $S_1$  and  $S_2$  are on, the capacitors C1and C2 keep charged to Vin (Vdc1 = Vdc2 = Vin). The voltages on Bus 1 and Bus 2 are Vin as well. The current flow of this time interval is shown in Fig. 4(b). When t satisfies  $t2 \le t < t3$  in Fig. 3(a),

the switches S1a, S1c, S2a, S2c are driven by the gate-source voltage, respectively. H-Bridges 1 and 2 are in positive conducting state. Output voltage equals 2Vin . Because  $S_1$  and  $S_2$  are on, the capacitors C1 and C2 keep charged to Vin (Vdc1 = Vdc2 = Vin). The voltages on Bus 1 and Bus 2 are Vin as well.

Fig.3. Operational waveforms of the proposed multilevel inverter. (a) Operational mode 1. (b) Operational mode 2.

ISSN: 2456 - 5083

A Peer Revieved Open Access International Journal

www.ijiemr.org

The current flow of this time interval is shown in Fig. 4(c). When t satisfies  $t3 \le t < t4$  in Fig. 3(a), the switches S1a, S1c, S2a, S2c are driven by the gate-source voltage respectively. H-Bridges 1 and 2 are in positive conducting state.Output voltage equals 3Vin . Because S\_1 and S2 are on, the capacitor C1 keeps charged to Vin (Vdc1 = Vdc2 =Vin ), and the capacitor C2 is discharged. The voltages on Bus 1 and Bus 2 are Vin and 2Vin, respectively. The current flow of this time interval is shown in Fig. 4(d). When t satisfies  $t4 \le t < t5$  in Fig. 3(a), the switches S1a,S1c, S2a, S2c are driven by the gate-source voltage, respectively. H-Bridges 1 and 2 are in positive conducting state. Output voltage equals 4Vin . Because S1 and S2 are on, the capacitor C1 and C2 are discharged. The voltages on Bus 1 and Bus 2 both are 2Vin. The current flow of this time interval is shown in Fig. 4(e).

Fig.4. Active circuits for different operation intervals in the operational mode 1: (a) t0 - t1; (b) t1 - t2; (c) t2 - t3; (d) t3 - t4; (e) t4 - t5; (f) t5 - t6; (g) t6 - t7; (h) t7 - t8.

The operations in  $t5 \le t < t6$ ,  $t6 \le t < t7$ , and  $t7 \le t < t8$ , are the same as the operations in  $t3 \le t < t4$ ,  $t2 \le t < t3$ , and  $t1 \le t < t2$ , respectively. The active circuits are shown in Fig. 4(f)— (h). Comparing with operational mode 1, the mode 2 has the different active circuits in two time intervals. When t satisfies  $t2 \le t < t3$  in operational mode 2 as shown in Fig. 3(b), the switches S1a, S1b, S2a, S2c are driven by the gate-source voltage, respectively. H-Bridge 1 is in freewheeling state, and H-Bridge 2 is in positive conducting state. Output voltage equals 2Vin . Because  $S_1$  and S2 are on, the capacitor S10 keeps charged to S11 and S22 are on, the capacitor S12 keeps charged to S13 discharged. The

voltages on Bus 1 and Bus 2 are Vin and 2Vin, respectively. The current flow of this time interval is shown in Fig. 5(a). Similarly, the active circuit of  $t6 \le t < t7$  is shown in Fig. 5(b) that has the same operations as  $t2 \le t < t3$ .

Fig.5. Active circuits for different operation intervals in the operational mode 2: (a) t2 - t3; (b) t6 - t7.

The second half-cycle (from t8 on) has the similar active circuits as the first half-cycle (t1 - t8), but the current will be circulated in the opposite direction to provide the negative output voltage. The relations of on-state switches and output voltage level are described in Table I, as well as operations of two modes are compared closely. Table I has ten working states for nine voltage levels. When the operation enters a new state from an adjacent state, only one power switch changes between on and off. The device stress in switching devices of H-bridge circuit is higher than that in SC circuit. It can also be found that the output voltage in Mode 1 is more stable than Mode 2 due to less discharging period of switching capacitor. Along with the up-down movement of modulation signals (Vm 1c, Vm 1b, Vm 2c, Vm2b), the output voltage of the proposed inverter is a controllable nine-level staircase. The duration of each voltage level is determined by the duty-cycle of SC circuit and the phase-shifted angle of H-Bridge circuit.

#### **D.** Operation Cycles

ISSN: 2456 - 5083

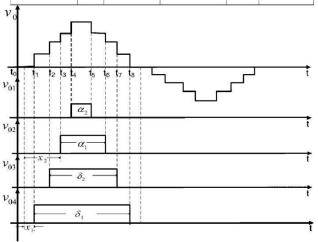

In aforementioned nine-level inverter, the staircase output vocan be divided into four components v01, v02, v03, and v04, as shown in Fig. 6. The durations of each component aredecided by the comparisons of reference signal ( $Vm\ 1c$ ,  $Vm\ 1b$ ,  $Vm\ 2c$ , Vm2b) and triangular carrier (Vc). If pulsewidths of the constituted component are defined as  $\delta 1$ ,  $\delta 2$ ,  $\alpha 1$ , and  $\alpha 2$ , Fourier analysis is accomplished for this nine-levelstaircase. The magnitude of the harmonics is derived by

$$V_n = \frac{4V_{\text{in}}}{n\pi} \left( \cos\left(n\left(\frac{\pi - \alpha_1}{2}\right)\right) + \cos\left(n\left(\frac{\pi - \delta_1}{2}\right)\right) + \cos\left(n\left(\frac{\pi - \delta_2}{2}\right)\right) + \cos\left(n\left(\frac{\pi - \delta_2}{2}\right)\right) \right),$$

$$n = 1, 3, 5, \dots \tag{3}$$

A Peer Revieved Open Access International Journal

www.ijiemr.org

Table I. Relations of On-State Switches and Output Voltage

| Mode 1                                                                                                  |                           |                                             | Mode 2                                                             |                   |                                             |

|---------------------------------------------------------------------------------------------------------|---------------------------|---------------------------------------------|--------------------------------------------------------------------|-------------------|---------------------------------------------|

| On-state switches                                                                                       | Output<br>voltage         | Capacitor State                             | On-state switches                                                  | Output<br>voltage | Capacitor State                             |

| S100 S100 S200 S200 S10 S2                                                                              | $4V_{in}$                 | C <sub>1</sub> , C <sub>2</sub> Discharging | S14 S10 S24 S20 S15 S1                                             | 4V <sub>in</sub>  | C <sub>1</sub> , C <sub>2</sub> Discharging |

| S <sub>10</sub> , S <sub>10</sub> , S <sub>20</sub> , S <sub>20</sub> , S <sub>1</sub> , S <sub>2</sub> | $3V_{in}$                 | C <sub>2</sub> Discharging                  | S10 S10 S20 S20 S1, S2                                             | 3V <sub>in</sub>  | C <sub>2</sub> Discharging                  |

| S <sub>10</sub> , S <sub>10</sub> , S <sub>20</sub> , S <sub>2</sub> , S <sub>1</sub> , S <sub>2</sub>  | $2V_{in}$                 | C <sub>1</sub> , C <sub>2</sub> Charging    | S10. S10. S20. S20. S1 S2                                          | $2V_{in}$         | C <sub>2</sub> Discharging                  |

| S10 S14 S20 S20 S2                                                                                      | V <sub>in</sub>           | C1, C2 Charging                             | S100 S100 S200 S100 S1 S2                                          | V <sub>in</sub>   | C1, C2 Charging                             |

| S1a, S1b, S2a, S2b, S1 S2                                                                               |                           |                                             | S16 S16 S26 S26, S1 S2                                             |                   |                                             |

| or S <sub>10</sub> , S <sub>1d</sub> , S <sub>20</sub> , S <sub>2d</sub>                                | 0                         | C <sub>1</sub> , C <sub>2</sub> Charging    | or S <sub>10</sub> S <sub>14</sub> S <sub>20</sub> S <sub>24</sub> | 0                 | C <sub>1</sub> , C <sub>2</sub> Charging    |

| S10, S14 S24 S24 S1 S2                                                                                  | -V <sub>in</sub>          | C <sub>1</sub> , C <sub>2</sub> Charging    | S10, S1d, S21, S2d, S1 S2                                          | -V <sub>in</sub>  | C <sub>1</sub> , C <sub>2</sub> Charging    |

| S16, S16, S26, S26, S1 S2                                                                               | -2 <i>V</i> <sub>in</sub> | C <sub>1</sub> , C <sub>2</sub> Charging    | S10 S10 S20 S20 S1 S2                                              | -2V <sub>in</sub> | C <sub>2</sub> Discharging                  |

| S16, S16, S26, S26, S1, S2                                                                              | -3 <i>V</i> <sub>in</sub> | C <sub>2</sub> Discharging                  | S16, S1d, S26, S2d, S1, S2                                         | -3V <sub>in</sub> | C <sub>2</sub> Discharging                  |

| S16 S16 S26 S26 S6 S2                                                                                   | -4 <i>V</i> <sub>in</sub> | C <sub>1</sub> , C <sub>2</sub> Discharging | S 16 S 16 S 25 S 26 S 1, S 2                                       | -4V <sub>in</sub> | C <sub>1</sub> , C <sub>2</sub> Discharging |

Fig.6. Output voltage decomposition for Fourier analysis in mode 1.

In operational mode 1

$$\delta_{1} = \frac{V_{m,2b}}{V_{pp}} \pi, \qquad \alpha_{1} = \frac{V_{m,1b}}{V_{pp}} \pi,$$

$$\delta_{2} = \frac{V_{m,2c}}{V_{pp}} \pi, \qquad \alpha_{2} = \frac{V_{m,1c}}{V_{pp}} \pi. \tag{4}$$

In operation mode 2

$$\delta_{1} = \frac{V_{m,2b}}{V_{pp}} \pi, \qquad \alpha_{1} = \frac{V_{m,2c}}{V_{pp}} \pi,$$

$$\delta_{2} = \frac{V_{m,1b}}{V_{pp}} \pi, \qquad \alpha_{2} = \frac{V_{m,1c}}{V_{pp}} \pi.$$

(5)

$$k_1 = \frac{\alpha_1}{\delta_1}, \quad k_2 = \frac{\alpha_2}{\delta_2}, \quad x_1 = \frac{\pi - \delta_1}{2}, \quad x_2 = \frac{\pi - \delta_2}{2}.$$

(6)

To further describe the relations of output THD and pulse widths  $\alpha 1$ ,  $\alpha 2$ ,  $\delta 1$ ,  $\delta 2$ , four parameters are predefined

$$k_1 = \frac{\alpha_1}{\delta_1}, \quad k_2 = \frac{\alpha_2}{\delta_2}, \quad x_1 = \frac{\pi - \delta_1}{2}, \quad x_2 = \frac{\pi - \delta_2}{2}.$$

(6)

The output waveforms can be characterized by these four constants. According to the definitions as

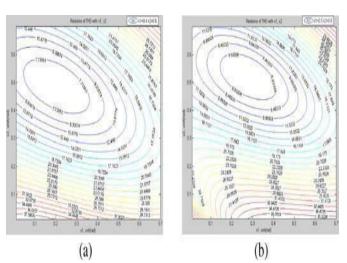

$(\sqrt{\sum_{n=2...}^{\infty} V_n^2/V_1}) \times 100\%)$ , THD of output voltage can be calculated by the harmonic magnitudes. The relations of output THD to x1, x2 are given in Fig. 7 with the fixed k1 and k2. It can be found from Fig. 7 that THD is easy to beregulated by the duration width of voltage levels. At the suitable scope of x1 and x2, THD of output voltage is less than 10%. When k1 = 0.6 and k2 = 0.4, THD can be less than 10% within the scope of 0.05 < x1 < 0.5 and 0.4 < x2 < 0.6. When k1 = 0.5 and k2 = 0.5, THD can be less than 10% within the scope of 0 < x1 < 0.4 and 0.4 < x2 < 0.6. Furthermore, THD becomes less along with the increasing number of voltage levels. The output magnitude of multilevel inverter can be regulated by the duration width of voltage levels as well. Two patterns are available to perform the regulations of THD and magnitude simultaneously. One is to regulate x1, x2with the fixed k1, k2.

Fig. 7. Relation curves of output THD versus x1, x2 (unit, rad): (a) k1 = 0.6, k2 = 0.4; (b) k1 = 0.5, k2 = 0.5.

The other one is to regulate k1, k2 with the fixed x1, x2. The numerical benchmark and THD optimization will be examined in the future study, and a fixed ratio (k1 = k2 = 0.5,  $x1 = \pi/8$ ,  $x2 = \pi/4$ ) is adopted to evaluate output harmonics insubsequent simulation and experiment. If the proposed dcac inverter is used as second stage of acac conversion, an acac controlled rectifier is introduced as preceding stage of acac conversion. Power factor correction (PFC) implemented by

ISSN: 2456 - 5083

A Peer Revieved Open Access International Journal

www.ijiemr.org

dc-dc converter can improve the power factor in ac-dc conversion. In this case, both SC and H bridge generate the optimized pulsewidth to minimize output THD. The magnitude regulation of output voltage can be performed by controllable ac-dc stage in input side. The minimized THD is achieved by this two-stage power circuit, namely, ac-dc stage is used to regulate magnitude, and dc-ac stage formed by the proposed inverter is used to minimize THD

#### III. MAT LAB SIMULATION RESULTS

A. Simulation Evaluation

12 V, the module 1 capacitor is  $C1 = 100 \, \mu \text{F}$  with  $80 \, \text{m}\Omega$  ESR, the module 2 capacitor is  $C2 = 220 \, \mu \text{F}$  with  $50 \, \text{m}\Omega$  ESR, the diodes D1 and D2 have 0.6 V forward voltage drop and  $50 \, \text{m}\Omega$  internal on-state resistance, and the load resistance is  $Ro = 12 \, \Omega$ . The following parameters are used for high-power simulation. The input voltage is  $V \text{in} = 100 \, \text{V}$ , the module 1 capacitor is  $C1 = 300 \, \mu \text{F}$  with  $30 \, \text{m}\Omega$  ESR, the module 2 capacitor is  $C2 = 560 \, \mu \text{F}$  with  $20 \, \text{m}\Omega$  ESR, and the load resistance is  $Ro = 12 \, \Omega$ . The output frequency S is S kHz. The waveforms of low power and high power are demonstrated in Fig. S 10(a) and (b), respectively. It can be seen that the proposed inverter can

and inner resistance. m $\Omega$  ESR, and the load resistance is  $Ro = 12~\Omega$ . It can be found

from Fig. 11(c) that the voltage drop is indistinctive in each

step of staircase output because the discharging periods of SCs become shorter for 13-level inverter. The output

spectrums of 9-level and 13-level inverter are illustrated in Fig. 11(b) and (d), respectively. The fundamental frequency is

25 kHz that is the same as output frequency. It can be observed that the fundamental harmonic is significantly higher

than the other harmonics. The magnitude of fundamental component is below 40 V for nine-level inverter, while the

magnitude of fundamental component is 55 V for a 13-level inverter. The dominating harmonics are compared in Table

III. The calculated THD is 19.1% for 9-level inverter and

work at higher power. C1 and C2 can be converted to resonant switched-capacitor topology easily [29], [30] and

hence the less power loss can be achieved in the frontend SC stage. The simulation waveforms are accorded with theoretical analysis. C1 is discharged at the interval of t4 to t5, and C2 is discharged at the interval of t3 to t6. Both capacitors are charged and discharged once every half cycle. Because of the internal resistance of diodes D1 and D2, the charging current can be divided into several subintervals that are in accordance with operational analysis in Fig. 4. Considering the charging cycle and RC time constant, the peak current of charging period and voltage drop of discharging period are rational at the given conditions. Theoretically, low power can obtain amplitude of  $4 \times 12$  V, and high power can obtain amplitude of  $4 \times 100$  V. However, an amplitude The output voltage and voltage spectrum are compared in Fig. 11, including 9- and 13-level inverter. Fig. 11(a) is output waveform of nine-level inverter at condition of k1 = k2 = 0.5,  $x1 = \pi/8$ , and  $x2 = \pi/4$ . The voltage step instaircase output has a slightly drop at t =0.00465-0.00475 due to the discharging cycle of SC. Fig. 11(c) is output waveform of 13-level inverter with the same duration of each voltage level. A thirteen-level inverter adopts  $3 \times 2$  structure, and the following circuit parameters are used. The input voltage is Vin = 12 V, the module 1 capacitors are  $C1 = 100 \ \mu\text{F}C$ \_ 1 = 120  $\mu\text{F}$  with 80 m $\Omega$  ESR, the module 2 capacitor are  $C2 = 220 \,\mu\text{F}C_{2} = 250 \,\mu\text{F}$  with 50

the theoretical amplitude caused by forward voltage drop

14.1% for 13-level inverter. A 13-level inverter has fewer

high order harmonics than nine-level inverter. It can be estimated that the harmonics can be further cut down along

with the increasing number of voltage levels. Thus, the proposed inverter produces near sinusoidal staircase output,

and two methods can make it more sinusoidal. One is to optimize the duration of voltage levels; the other one is to

increase the number of voltage levels.

ISSN: 2456 - 5083

A Peer Revieved Open Access International Journal

www.ijiemr.org

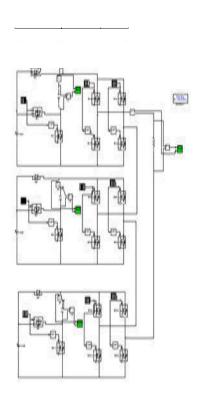

Fig.9. Matlab Simulink model of the proposed Method

13 level multilevel Inverter.

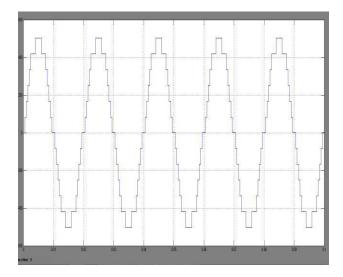

Fig10. Output Voltage of the 13 level Inverter.

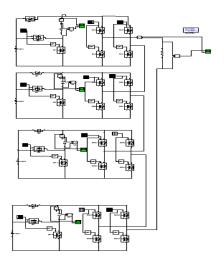

Fig:11. Matlab Simulink model of proposed method 17 level multilevel inverter

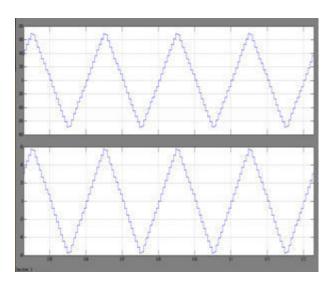

Fig 12: Output voltage of 17 level inverter.

ISSN: 2456 5083

#### IV. CONCLUSION

In this paper, a novel SC-based cascaded multilevel inverter was proposed. Both 9-level and 13-level 17 —level circuit topology are examined in depth. Compared with conventional cascaded multilevel inverter, the proposed inverter can greatly decrease the number of switching devices. A single carrier modulation named by symmetrical PSM, was presented with the low switching frequency and simple implementation. Comparing with traditional cascade H-bridge, the number of voltage levels can be further increased by SC frontend. For instance, the number of voltage levels increases twice in half

A Peer Revieved Open Access International Journal

www.ijiemr.org

Comparing with traditional cascade H-bridge, the number of voltage levels can be further increased by SC frontend. For instance, the number of voltage levels increases twice in half cycle of 9-level circuit, and the number of voltage levels increases three times in half cycle of 13-level circuit, the number of voltage levels four times in half cycle of 17 – level circuit. Meanwhile, the magnitude control can be accomplished by pulsewidth regulation of voltage level, so the proposed multilevel inverter can serve as HF power source with controlled magnitude and fewer harmonics. This paper mainly analyzes 13-level and 17-level inverters. The method of analysis and design is also applicable to other members of the proposed inverter. The proposed inverter can be applied to grid-connected.

#### V. REFERENCES

- [1] P. Jain and H. Pinheiro, —Hybrid high frequency AC power distribution architecture for telecommunication systems,

- IEEE Trans. Aerospace Electron. Syst., vol. 35, no. 1, pp. 138–147, Jan. 1999.

- [2] J. Drobnik, —High frequency alternating current power distribution, I in Proc. 16th Int. Telecommun. Energy Conf., (INTELEC \_94), Oct. 30–Nov. 3, pp. 292–296.

- [3] B. K. Bose, M.-H. Kin, and M. D. Kankam, —High frequency AC vs. DC distribution system for next generation hybrid electric vehicle, In Proc. IEEE Int. Conf. Ind. Electron., Control, Instrum. (IECON), Aug. 5–10, 1996, vol. 2, pp. 706–712.

- [4] S. Chakraborty and M. G. Simoes, —Experimental evaluation of active filtering in a single-phase high-frequency AC microgrid, IEEE Trans. Energy Convers., vol. 24, no. 3, pp. 673–682, Sep. 2009.

- [5] R. Strzelecki and G. Benysek, Power Electronics in Smart Electrical Energy Networks. London, U.K.: Springer-Verlag, 2008.

- [6] Z.Ye, P. K. Jain, and P. C. Sen, —A two-stage resonant inverter with control of the phase angle and magnitude of the output voltage, IEEE Trans. Ind. Electron., vol. 54, no. 5, pp. 2797–2812, Oct. 2007.

- [7] L. M. Tolbert, F. Z. Peng, and T. G. Habetler, —Multilevel PWM methods at low modulation indices, IEEE Trans. Power Electron., vol. 15, no. 4, pp. 719–725, Jul. 2000.

- [8] C. C. Antaloae, J. Marco, and N. D. Vaughan, —Feasibility of highfrequency alternating current power for motor auxiliary loads in vehicles, IEEE Trans. Veh. Technol., vol. 60, no. 2, pp. 390–405, Feb. 2011.

- [9] K. W. E. Cheng, —Computation of the AC resistance of multistranded conductor inductors with multilayers for high frequency switching converters, IEEE Trans. Magn., vol. 36, no. 4, pp. 831–834, Jul. 2000.

- [10] P. P. Rodriguez, M. M. D. Bellar, R. R. S.Mu noz-Aguilar, S. S. Busquets- Monge, and F. F. Blaabjerg,

- —Multilevel clamped multilevel converters (MLC), IEEE Trans. Power Electron., vol. 27, no. 3, pp. 1055–1060, Mar. 2012.

- [11] K. Ilves, A. Antonopoulos, S. Norrga, and H.-.P. Nee, —A new modulation method for the modular multilevel converter allowing fundamental switching frequency, IEEE Trans. Power Electron., vol. 27, no. 8, pp. 3482–3494, Aug. 2012.

- [12] H. Akagi, —Classification, terminology, and application of the modular multilevel cascade converter (MMCC), IEEE Trans. Power Electron., vol. 26, no. 11, pp. 3119–3130, Nov. 2011.

- [13] M. F. Kangarlu and E. Babaei, —A generalized cascaded multilevel inverter using series connection of submultilevel inverters, IEEE Trans. Power Electron., vol. 28, no. 2, pp. 625–636, Feb. 2013.

- [14] H. L. Chan, K. W. E. Cheng, and D. Sutanto,

ISSN: 2456 5083

—Bidirectional phase-shifted DC–DC converter, IEEE Electron. Lett., vol. 35, no. 7, pp. 523–524, Apr. 1999.