A Peer Revieved Open Access International Journal

www.ijiemr.org

### **COPY RIGHT**

2017 IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 20 May 2017. Link:

http://www.ijiemr.org/downloads.php?vol=Volume-6&issue=ISSUE-3

Title: Design of An Efficient Aging-Aware Reliable Multiplier Design With Adaptive Hold Logic.

.

Volume 06, Issue 03, Pages: 229 – 235.

**Paper Authors**

### BETHAPUDI.PUSHPA VENI, D.SRIDHAR (Ph.D).

Sri Sunflower College of Engineering and Technology, Lankapalli, (A.P), INDIA.

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

# Design of An Efficient Aging-Aware Reliable Multiplier Design With Adaptive Hold Logic

### \*BETHAPUDI.PUSHPA VENI, \*\*D.SRIDHAR (Ph.D)

- \*PG Scholar, Dept of ECE (VLSID), Sri Sunflower College of Engineering and Technology, Lankapalli, (A.P),INDIA..

- \*\*Associate Professor, Head of the Department of ECE, Sri Sunflower College of Engineering and Technology, Lankapalli, (A.P.),India.

Email ID: pushpavenib5@gmail.com, sridhar.done@gmail.com

#### **ABSTRACT:**

Digital multipliers are among the most critical arithmetic functional units. The overall performance of these systems depends on the throughput of the multiplier. Meanwhile, the negative bias temperature instability effect occurs when a pMOS transistor is under negative bias (Vgs = -Vdd), increasing the threshold voltage of the pMOS transistor, and reducing multiplier speed. A similar phenomenon, positive bias temperature instability, occurs when an nMOS transistor is under positive bias. Both effects degrade transistor speed, and in the long term, the system may fail due to timing violations. Therefore, it is important to design reliable high-performance multipliers. In this paper, we propose an aging-aware multiplier design with a novel adaptive hold logic (AHL) circuit. The multiplier is able to provide higher throughput through the variable latency and can adjust the AHL circuit to mitigate performance degradation that is due to the aging effect. Moreover, the proposed architecture can be applied to a column- or row-bypassing multiplier. The experimental results show that our proposed architecture with 16 ×16 and 32 ×32 column-bypassing multipliers can attain up to 62.88% and 76.28% performance improvement, respectively, compared with 16×16 and 32×32 fixed-latency columnbypassing multipliers. Furthermore, our proposed architecture with  $16 \times 16$  and  $32 \times 32$  row-bypassing multipliers can achieve up to 80.17% and 69.40% performance improvement as compared with 16×16 and  $32 \times 32$  fixed-latency row-bypassing multipliers.

**Keywords:** Adaptive hold logic (AHL), negative bias temperature instability (NBTI), positive bias temperature instability (PBTI), reliable multiplier, variable latency.

ISSN: 2456 - 5083

A Peer Revieved Open Access International Journal

ISSN: 2456 - 5083

www.ijiemr.org

## **I INTRODUCTION**

DIGITAL multipliers are among the most critical arithmetic functional units in many applications, such as the Fourier transform, discrete cosine transforms, and digital filtering. The throughput of these applications depends on multipliers, and if the multipliers are too slow, the performance of entire circuits will be reduced. Furthermore, negative bias temperature instability (NBTI) occurs when a pMOS transistor is under negative bias (Vgs = -Vdd). In this situation, the interaction between inversion layer holes and hydrogen-passivated Si atoms breaks the Si-H bond generated during the oxidation process, generating H or H2 molecules. When these molecules diffuse away, interface traps are left. The accumulated interface traps between silicon and the gate oxide interface result in increased threshold voltage (Vth), reducing the circuit switching speed. When the biased voltage is removed, the reverse reaction occurs, reducing the NBTI effect. However, the reverse reaction does not eliminate all the interface traps generated during the stress phase, and Vth is increased in the long term. Hence, it is important to design a reliable high-performance multiplier. The corresponding effect on an nMOS transistor is positive bias temperature instability (PBTI), which occurs when an nMOS transistor is under positive bias. Compared with the NBTI effect, the PBTI effect is much smaller on oxide/polygate transistors, and therefore is usually ignored. However, for high-k/metal-gate nMOS transistors

with significant charge trapping, the PBTI effect can no longer be ignored. In fact, it has been shown that the PBTI effect is more significant than the NBTI effect on 32-nm high-k/metal-gate processes. A traditional method to mitigate the aging effect is overdesign, including such things as guard-banding and gate oversizing; however, this approach can be very pessimistic and area and power inefficient. To avoid this problem, many **NBTI-aware** methodologies have been proposed. An NBTI-aware technology mapping technique was proposed in to guarantee the performance of the circuit during its lifetime. In, an NBTI-aware sleep transistor was designed to reduce the aging effects on pMOS sleeptransistors, and the lifetime stability of the powergated circuits under consideration was improved. Wu and Marculescu proposed a joint logic restructuring and pin reordering method, which is based on detecting functional symmetries and transistor stacking effects. They also proposed an NBTI optimization method that considered path sensitization. In dynamic voltage scaling and bodybasing techniques were proposed to reduce power or extend circuit life. These techniques, however, require circuit modification or do not provide optimization of specific circuits. Traditional circuits use critical path delay as the overall circuit clock cycle in order to perform correctly. However, the probability that the critical paths are activated is low. In most cases, the path delay is shorter than the critical path. For these noncritical paths, using the critical path delay as the overall cycle period will

A Peer Revieved Open Access International Journal

www.ijiemr.org

result in significant timing waste. Hence, the variable-latency design was proposed to reduce the timing waste of traditional circuits. The variablelatency design divides the circuit into two parts: 1)Shorter paths 2) Longer paths. Shorter paths can execute correctly in one cycle, whereas longer paths need two cycles to execute. When shorter paths are activated frequently, the average latency of variable-latency designs is better than that of traditional designs. For example, several variablelatency adders were proposed using the speculation technique with error detection and recovery. A short path activation function algorithm was proposed in to improve the accuracy of the hold logic and to optimize the performance of the variable-latency circuit. An instruction scheduling algorithm was proposed in to schedule the operations on non uniform latency functional units and improve the performance of Very Long Instruction Word processors.

### II.LITERATURE SURVEY

Negative Bias Temperature Instability (NBTI) has become one of the major causes for temporal reliability degradation of nano-scale circuits. In this paper, we analyze the temporal delay degradation of logic circuits due to NBTI. We show that knowing the threshold voltage degradation of a single transistor due to NBTI, one can predict the performance degradation of a circuit with a

ISSN: 2456 - 5083

reasonable degree of accuracy. We also propose a sizing algorithm taking NBTI-affected performance degradation into account to ensure the reliability of nano-scale circuits for a given period of time. Experimental results on several benchmark circuits show that with an average of 8.7% increase in area one can ensure reliable performance of circuits for 10 years. Bipul C Paul, Kunhyuk Kang, Haldun Kufluoglu, With the rapid progress semiconductor technology and the shrinking of device geometries, the resulting processors are increasingly becoming prone to effects like aging and soft errors. As a processor ages, its electrical characteristics degrade, i.e., the switching times of its transistors increase. Hence, the processor cannot continue error-free operation at the same clock frequency and/or voltage for which it was originally designed. In order to mitigate such effects, recent research proposes to equip processors with special circuitry that automatically adapts its clock frequency in response to changes in its circuit-level timing properties. From the point of view of tasks running on these processors, such autonomic frequency scaling (AFS) processors become slower as they gradually age. This leads to additional execution delay for tasks, which needs to be analyzed carefully, particularly in the context of hard real time or safety-critical systems. Hence, for real-time systems based on AFS processors, the associated schedulability analysis should be agingaware which a relatively unexplored topic is so far. In this paper we propose a schedulability analysis

A Peer Revieved Open Access International Journal

www.ijiemr.org

framework that accounts such aging-induced degradation and changes in timing properties of the processor, when designing hard real-time systems. In particular, we address the schedulability and task mapping problem by taking a lifetime constraint of the system into account. In other words, the system should be designed to be fully operational (i.e., meet all deadlines) till a given minimum period of time. The proposed framework is based on an aging model of the processor which we discuss in detail. In addition to studying the effects of aging on the schedulability of real-time tasks, we also discuss its impact on task mapping and resource dimensioning. Alejandro Masrur, Philipp Kindt, Martin Becker and Samarjit Chakraborty. Design of portable battery operated multimedia devices requires energy efficient multiplication circuits. This paper presents a novel approach to reduce power consumption of digital multiplier based on dynamic bypassing of partial products. The bypassing incorporated into the multiplier hardware eliminates the redundant signal transitions, which appear within the carry save adders when the partial product is zero.

### III. METHODOLOGY

In this project, we propose an aging-aware reliable multiplier design with novel adaptive hold logic (AHL) circuit. The multiplier is based on the variable-latency technique and can adjust the AHL

ISSN: 2456 - 5083

circuit to achieve reliable operation under the influence of NBTI and PBTI effects. To be specific, the contributions of this paper are summarized as follows: 1) novel variable-latency multiplier architecture with an AHL circuit. The AHL circuit can decide whether the input patterns require one or two cycles and can adjust the judging criteria to ensure that there is minimum performance degradation after considerable aging occurs; 2) comprehensive analysis and comparison of the multiplier's performance under different cycle periods to show the effectiveness of our proposed architecture; 3) an aging-aware reliable multiplier design method that is suitable for large multipliers. We implemented the 4x4 and 8x8 bypassing multipliers.

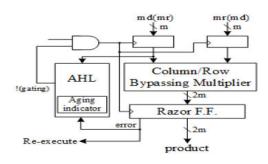

#### • Adaptive hold logic (AHL) circuit

**Fig1: Proposed Architecture**

#### PROPOSED AGING-AWARE MULTIPLIER

The proposed aging-aware reliable multiplier design. It introduces the overall architecture and the functions of each component and also describes how

A Peer Revieved Open Access International Journal

www.ijiemr.org

to design AHL that adjusts the circuit when significant aging occurs.

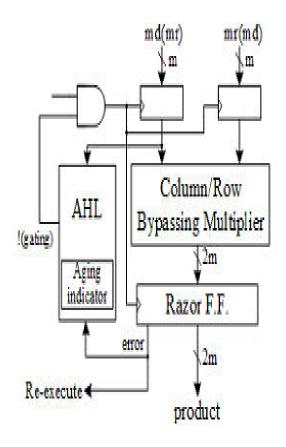

### **Proposed Architecture**

Proposed aging-aware multiplier architecture, which includes two m-bit inputs (m is a positive number), one 2m-bit output, one column- or row-bypassing multiplier, 2m 1-bit Razor flip-flops, and an AHL circuit.

Fig 2: Proposed architecture (md means multiplicand; mr means multiplicator).

### **IV.RESULTS**

#### 64 x 64:

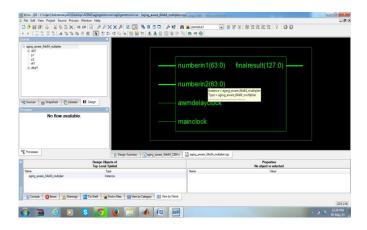

#### **RTL Schematic:**

Fig 3: RTL Schematic

A Peer Revieved Open Access International Journal

www.ijiemr.org

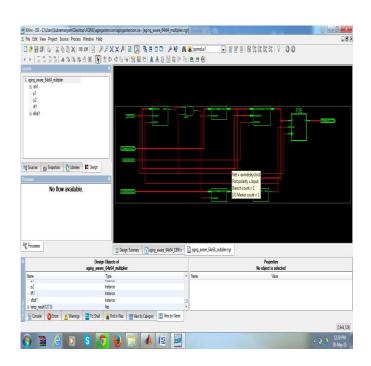

#### **TECHNOLOGY SCHEMATIC:**

Fig 4: Technology Schematic

#### **DESIGN SUMMARY:**

Fig 5: Design Summary

### V.CONCLUSION

In Proposed the multiplier is based on the variablelatency technique. The AHL circuit to achieve reliable operation under the influence of NBTI and PBTI effects. Our proposed architecture with the 8x8 column-bypassing multipliers and rowbypassing multipliers. We are using Razor flip flop to hold the logic. And the output of this is given as an input to the aging indicator.

Note that in addition to the BTI effect that increases transistor delay, interconnect also has its aging issue, which is called electromigration. Electromigration occurs when the current density is high enough to cause the drift of metal ions along the direction of electron flow. The metal atoms will be gradually displaced after a period of time, and the geometry of the wires will change. If a wire becomes narrower, the resistance and delay of the wire will be increased. and in the electromigration may lead to open circuits. This issue is also more serious in advanced process technology because metal wires are narrower, and changes in the wire width will cause larger resistance differences. If the aging effects caused by the BTI effect and electromigration are considered together, the delay and performance degradation will be more significant. Fortunately, our proposed variable latency multipliers can be used under the BTI of both the effect influence and electromigration. In addition, our proposed variable latency multipliers have less performance

A Peer Revieved Open Access International Journal

www.ijiemr.org

degradation because variable latency multipliers have less timing waste, but traditional multipliers need to consider the degradation caused by both the BTI effect and electromigration and use the worst case delay as the cycle period..

### **VI REFERENCES**

- [1] J. Howard, S. Dighe, S. Vangal, G. Ruhl, N. Borkar, S. Jain, V. Erraguntla, M. Konow, M. Riepen, M. Gries, G. Droege, T. Lund-Larsen, S. Steibl, S. Borkar, V. De, and R. Van Der Wijngaart, \A 48-core IA-32 processor in 45 nm CMOS using on-die message-passing and DVFS for performance and power scaling," IEEE Journal of Solid-State Circuits, vol. 46, pp. 173{183, January 2011.

- [2] S. Borkar, T. Karnik, S. Narendra, J. Tschanz, A. Keshavarzi, and V. De, \Parameter variations and impact on circuits and microarchitecture," in Proceedings of the Design Automation Conference, pp. 338{342, 2003.

- [3] P. Hurat, Y.-T. Wang, and N. K. Verghese, \Sub-90 nanometer variability is here to stay," in Proceedings of the EDA Technical Forum, pp. 26{28, 2005.

- [4] A. Devgan, 2003. Tutorial: http://www.research.ibm.com/compsci/project spotlight/ da/devgan-iccad03-tut.pdf.

- [5] S. V. Kumar, \Reliability-aware and variation-aware CAD techniques," 2009. Doctoral dissertation thesis, University of Minnesota, Twin Cities.

### **AUTHORS**

**D. SRIDHAR** Working as Head of the Department of ECE, received the **M.Tech** degree in VLSI System Design from Avanthi Institute of Engineering and Technology,

Narsipatnam, B.Tech degree in Electronics and Communication Engineering at Gudlavalleru Engineering College and also Pursuing his **Ph.D** in Low Power VLSI. He has total Teaching Experience (UG and PG) of 11 years. He has guided and coguided 8 P.G students .His Research areas included VLSI system Design, Digital signal Processing, Embedded Systems.

### **AUTHOR 2**

**BETHAPUDI PUSHPA VENI,** ,PG scholar Dept of ECE (VLSID), Sri Sunflower College of Engineering and Technology, B.Tech degree in Electronics and Communication Engineering at Malineni Lakshmaiah Womens Engineering College, JNTUK, Guntur.