A Peer Revieved Open Access International Journal

www.ijiemr.org

### **COPY RIGHT**

2017 IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 19 May 2017. Link:

http://www.ijiemr.org/downloads.php?vol=Volume-6&issue=ISSUE-3

Title: Area And Power Efficient Lms Adaptive Filter With Low Adaptation Delay.

Volume o6, Issue 03, Pages: 156 - 164.

**Paper Authors**

P. SANTHAN KUMAR, CH.NAVYA DEEPTHI.

Dept of ECE Sri Sunflower College of Engineering and Technology.

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

## AREA AND POWER EFFICIENT LMS ADAPTIVE FILTER WITH LOW ADAPTATION DELAY

P. SANTHAN KUMAR

PG, Dept of ECE (VLSI SD)

Sri Sunflower College of Engineering and

Technology.

Lankapalli (A.P),India.

putaboyinasanthankumar@gmail.com.

CH.NAVYA DEEPTHI

Assistant Professor, Dept of ECE

Sri Sunflower College of Engineering and

Technology.

Lankapalli (A.P),India.

navyabushn@gmail.com.

#### ABSTRACT:

In this paper, we present an efficient architecture for the implementation of a delayed least mean square adaptive filter. For achieving lower adaptation-delay and area-delay-power efficient implementation, we use a novel partial product generator and propose a strategy for optimized balanced pipelining across the time-consuming combinational blocks of the structure. From synthesis results, we find that the proposed design offers nearly 17% less area-delay product (ADP) and nearly 14% less energy-delay product (EDP) than the best of the existing systolic structures, on average, for filter lengths N = 8, 16, and 32. We propose an efficient fixed-point implementation scheme of the proposed architecture, and derive the expression for steady-state error. We show that the steady-state mean squared error obtained from the analytical result matches with the simulation result. Moreover, we have proposed a bit-level pruning of the proposed architecture, which provides nearly 20% saving in ADP and 9% saving in EDP over the proposed structure before pruning without noticeable degradation of steady-state-error performance.

*Keywords:* Adaptive filters, circuit optimization, fixed-point arithmetic, least mean square (LMS) algorithms.

A Peer Revieved Open Access International Journal

www.ijiemr.org

### **I INTRODUCTION**

Versatile computerized channels have been connected to an assortment of vital issues lately. Maybe a standout amongst the most surely understood versatile calculations is the minimum (LMS) calculation, mean squares which overhauls the weights of a transversal channel utilizing an inexact procedure of steepest plummet .Because of its straightforwardness, the LMS calculation has gotten a lot of been effectively consideration. and has connected in various territories including channel leveling, clamor and reverberation dropping and numerous others.

Slightest mean squares (LMS) calculations are a class of versatile channel used to copy a coveted channel by discovering the channel coefficients that identify with delivering the minimum mean squares of the lapse signal (distinction between the fancied sign and the real flag). It is a stochastic slope plunge strategy in which the channel is adjusted in light of the present time blunder. The fundamental thought behind LMS channel is to overhaul the channel weights to merge to the ideal channel weight. The calculation begins by expecting a little weights (zero as a rule), and at every stride, where the angle of the mean square slip, the weights are discovered and overhauled. In the event that the MSE-angle is sure, the mistake increments emphatically, else the same weight is utilized for further cycles, which implies we have to diminish the weights.

If the gradient is negative, weight need to be increased. Hence, basic weight update equation during the nth iteration:

$$w_{n+1} = w_n + \mu \Delta f(\eta) \dots (1)$$

ISSN: 2456 - 5083

Where  $\epsilon$  speaks to the mean-square error, $\mu$  is the stride size, Wn is the weight vector. The negative sign shows that, need to alter the weights in a course inverse to that of the inclination slant The mean-square blunder which is an element of channel weights is a quadratic capacity which says that it has one and only great, which minimizes the mean-square slip, is the ideal weight. The LMS subsequently, approaches towards this ideal weight by rising/plummeting down the mean square-lapse verses channel weight ben.

#### **II.LITERATURE SURVEY**

. The Slightest Mean Square (LMS) versatile channel is the most famous and most broadly utilized versatile channel on account of its straightforwardness as well as in view of its agreeable merging execution. The immediate structure LMS versatile channel includes a long discriminating way because of an internal item calculation to acquire the channel yield. The basic way is obliged to be diminished by pipelined usage when it surpasses the fancied example period. Since the ordinary LMS calculation does not backing pipelined execution in light of its recursive conduct, it is adjusted to a structure called the postponed LMS (DLMS) calculation, which permits pipelined usage of the channel. A ton of work has been done to execute the DLMS calculation in systolic architectures to expand the most extreme usable recurrence, at the same time; they include an adjustment deferral of ~ N cycles for channel length N, which is high for largeorder channels. Since the union execution corrupts significantly for an extensive adjustment delay, Visvanathan et al. have proposed an altered systolic structural planning to decrease the adjustment.

A Peer Revieved Open Access International Journal

www.ijiemr.org

A transpose-structure LMS versatile channel is proposed in where the channel yield at any moment relies on upon the postponed adaptations of weights and the quantity of deferrals in weights differs from 1 to N. Van and Feng have proposed a systolic construction modeling, where they have utilized generally handling components (PEs) accomplishing a lower adjustment delay with the discriminating way of one Macintosh operation. Ting et al. have proposed a fine-grained pipelined outline to confine the basic way to the greatest of one expansion time, which underpins high testing recurrence, yet includes a considerable measure of territory overhead for pipelining and higher force utilization than in, because of its extensive number of pipeline locks. Further exertion has been made by Meher and Maheshwari to decrease the quantity of adjustment postponements. Meher and Park have proposed a 2-bit augmentation cell, and utilized that with an effective snake tree for pipelined internal item reckoning to minimize the discriminating way and silicon range without expanding the quantity of adjustment deferrals. The current deal with the DLMS versatile channel does not talk about the altered point execution issues, e.g., area of radix point, decision of word length, and quantization at different phases of reckoning, despite the fact that they straightforwardly influence the meeting execution, especially because of the recursive conduct of the LMS calculation. Subsequently, altered point usage issues are given sufficient accentuation in this paper. In addition, we show here the streamlining of our already reported configuration, to diminish the quantity of pipeline postpones alongside the territory, inspecting period, and vitality utilization. The proposed configuration is discovered to be more effective as far as the force delay item (PDP)

and vitality delay item (EDP) contrasted with the current structures.

### III. PROBLEM OUTLINE

### **OBJECTIVE**

In commonsense uses of the LMS versatile transversal separating calculation, a postponement in the coefficient is overhauled. This venture talks about the conduct of the deferred LMS calculation. This undertaking present an effective construction modeling for the usage of a deferred minimum mean square versatile channel .with a specific end goal to accomplish lower adjustment postpone, a novel halfway item generator is utilized.

#### **EXISTING SYSTEM:**

The current deal with the DLMS versatile channel does not talk about the altered point usage issues, e.g., area of radix point, decision of word length, and quantization at different phases of calculation, in spite of the fact that they straightforwardly influence the merging execution, especially because of the recursive conduct of the LMS calculation.

### **EXISTING TECHNIQUE:**

• LMS adaptive filter.

#### **DRAWBACKS:**

ISSN: 2456 - 5083

- Fixed-point implementation issues.

- Delay & Area high.

### PROPOSED SYSTEM:

In this proposed we utilized a novel PPG for effective usage of general augmentations and

A Peer Revieved Open Access International Journal

www.ijiemr.org

internal item processing by regular sub expression sharing. We have proposed a proficient expansion plan for inward item processing to diminish the adjustment defer fundamentally so as to accomplish speedier union execution and to decrease the basic way to bolster high info examining rates.

### **PROPOSED TECHNIQUE:**

DLMS adaptive filter.

### IV. METHODOLOGY

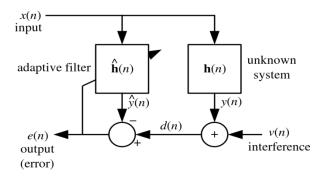

#### LMS ADAPTIVE FILTER:

The LMS Channel actualizes a versatile FIR channel question that profits the separated yield, the lapse vector, and channel weights. The LMS channel utilizes one of five distinct LMS calculations. Slightest mean squares (LMS) calculations are a class of versatile channel used to copy a craved channel by discovering the channel coefficients that identify with delivering the minimum mean squares of the blunder signal (distinction between the sought and the real flag). It is a stochastic angle drop strategy in that the channel is just adjusted in light of the mistake at the present time. It was designed in 1960 by Stanford College teacher Bernard Widrow and his first Ph.D. understudy, Ted Hoff.

ISSN: 2456 - 5083

### Fig 1: LMS adaptive filter

The LMS Channel actualizes a versatile FIR channel question that profits the separated yield, the lapse vector, and channel weights. The LMS channel utilizes one of five distinct LMS calculations.

#### **BLOCK DIAGRAM:**

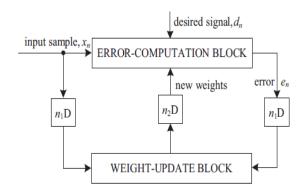

The proposed DLMS adaptive filter structural block diagram is as shown in the figure. dn is the fancied reaction, yn is the channel yield, and en means the mistake figured amid the nth emphasis.µ is the stride size, and N is the quantity of weights utilized as a part of the LMS versatile channel.

Fig 2: The proposed DLMS adaptive filter structural block diagram

In pipelined outlines with m pipeline organizes, the mistake en gets to be accessible after m cycles, where m is known as the "adjustment defer." The DLMS calculation in this manner uses the deferred blunder en-m, i.e., the slip relating to (n - m)th emphasis for upgrading the present weight rather than the later most lapse. The weight-overhaul comparison of DLMS versatile channel is gives ." The DLMS

A Peer Revieved Open Access International Journal

www.ijiemr.org

calculation in this manner uses the deferred blunder en-m.  $w_{n+1} {=}\ w_n + \mu$  .  $e_{n\text{-m}}$  .  $x_{n\text{-m}}$

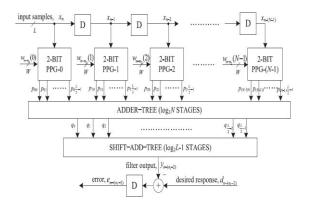

The adjusted DLMS calculation decouples reckonings of the blunder processing piece to minimize the quantity of pipeline stages and adjustment delay. As demonstrated in Figure, there are two fundamental registering squares in the versatile channel building design: 1) the mistake calculation piece, and 2) weight-overhaul piece. The mistake processing square comprises of N number of 2-b fractional item generators (PPG) comparing to N multipliers and a group of L/2 double viper trees, trailed by a solitary shift-add tree.

On the off chance that we present pipeline locks after every expansion, it would oblige L(N-1)/2 + L/2 - 1 hooks in log2  $N+\log 2$  L-1 stages, which would prompt a high adjustment postpone and present a huge overhead of range and force utilization for extensive estimations of the adjustment postponement is deteriorated into n1 and n2.

The lapse reckoning piece creates the postponed mistake by n1 -1 cycles, which is nourished to the weight-upgrade square demonstrated in the beneath Figure in the wake of scaling.

#### **V.RESULTS**

#### LMS ADAPTIVE FILTER:

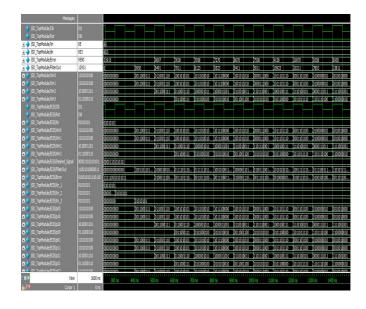

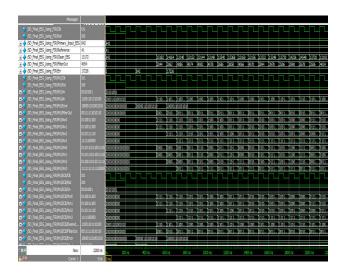

Fig 4: Proposed DLMS adaptive filter design simulation result

Inputs :clock clock,reset 0,xn 85,dn 853

Outputs :error 9550,yn 12931

### **MODIFICATION PART:**

ISSN: 2456 - 5083

### SIMULATION RESULT OF EEG:

A Peer Revieved Open Access International Journal

www.ijiemr.org

Fig 5: Proposed DLMS adaptive filter in EEG application result

Input : clock clock,reset 0,primary input

842,reference 41,fir clean eeg 13172

Outputs :error 4054,yn 17226

#### **SYNTHESIS IMPLEMENTATION:**

Timing Summary:

Speed Grade: -4

Minimum period: 21.280ns (Maximum

Frequency: 46.992MHz)

Minimum input arrival time before clock:

20.190ns

Maximum output required time after clock:

24.507ns

Maximum combinational path delay: 23.417ns

| Device Utilization Summary                     |       |           |             |         |  |  |  |  |

|------------------------------------------------|-------|-----------|-------------|---------|--|--|--|--|

| Logic Utilization                              | Used  | Available | Utilization | Note(s) |  |  |  |  |

| Number of Slice Flip Flops                     | 105   | 7,168     | 1%          |         |  |  |  |  |

| Number of 4 input LUTs                         | 770   | 7,168     | 10%         |         |  |  |  |  |

| Logic Distribution                             |       |           |             |         |  |  |  |  |

| Number of occupied Slices                      | 417   | 3,584     | 11%         |         |  |  |  |  |

| Number of Slices containing only related logic | 417   | 417       | 100%        |         |  |  |  |  |

| Number of Slices containing unrelated logic    | 0     | 417       | 0%          |         |  |  |  |  |

| Total Number of 4 input LUTs                   | 776   | 7,168     | 10%         |         |  |  |  |  |

| Number used as logic                           | 770   |           |             |         |  |  |  |  |

| Number used as a route-thru                    | 6     |           |             |         |  |  |  |  |

| Number of bonded IOBs                          | 53    | 141       | 37%         |         |  |  |  |  |

| IOB Flip Flops                                 | 13    |           |             |         |  |  |  |  |

| Number of GCLKs                                | 1     | 8         | 12%         |         |  |  |  |  |

| Total equivalent gate count for design         | 7,514 |           |             |         |  |  |  |  |

| Additional JTAG gate count for IOBs            | 2,544 |           |             |         |  |  |  |  |

| Performance Summary |                               |              |               |  |  |

|---------------------|-------------------------------|--------------|---------------|--|--|

| Final Timing Score: | 0                             | Pinout Data: | Pinout Report |  |  |

| Routing Results:    | All Signals Completely Routed | Clock Data:  | Clock Report  |  |  |

Fig 6: Device Utilization Summary Of DLMS Adaptive Filter

### MODIFICATION PART DESIGN SUMMARY OF EEG:

**Timing Summary:**

Speed Grade: -4

Minimum period: 23.922ns (Maximum

Frequency: 41.803MHz)

Minimum input arrival time before clock:

21.444ns

Maximum output required time after clock:

27.587ns

ISSN: 2456 - 5083

Maximum combinational path delay: 25.093ns

A Peer Revieved Open Access International Journal

www.ijiemr.org

| LMSWEX Partition Summary                       |       |           |             |        |  |  |  |  |  |

|------------------------------------------------|-------|-----------|-------------|--------|--|--|--|--|--|

| No partition information was found.            |       |           |             |        |  |  |  |  |  |

| Device Utilization Summary                     |       |           |             |        |  |  |  |  |  |

| Logic Utilization                              | Used  | Available | Utilization | Note(s |  |  |  |  |  |

| Number of Slice Flip Flops                     | 102   | 7,168     | 1%          |        |  |  |  |  |  |

| Number of 4 input LUTs                         | 493   | 7,168     | 6%          |        |  |  |  |  |  |

| Logic Distribution                             |       |           |             |        |  |  |  |  |  |

| Number of occupied Slices                      | 275   | 3,584     | 7%          |        |  |  |  |  |  |

| Number of Slices containing only related logic | 275   | 275       | 100%        |        |  |  |  |  |  |

| Number of Slices containing unrelated logic    | 0     | 275       | 0%          |        |  |  |  |  |  |

| Total Number of 4 input LUTs                   | 494   | 7,168     | 6%          |        |  |  |  |  |  |

| Number used as logic                           | 493   |           |             |        |  |  |  |  |  |

| Number used as a route-thru                    | 1     |           |             |        |  |  |  |  |  |

| Number of bonded IOBs                          | 52    | 141       | 36%         |        |  |  |  |  |  |

| IOB Flip Flops                                 | 8     |           |             |        |  |  |  |  |  |

| Number of GCLKs                                | 1     | 8         | 12%         |        |  |  |  |  |  |

| Total equivalent gate count for design         | 5,905 |           |             |        |  |  |  |  |  |

| Additional JTAG gate count for IOBs            | 2,496 |           |             |        |  |  |  |  |  |

**Fig 7: Modification Part Design Summary Of Eeg**

### RTL AND TECHNOLOGY SCHEMATIC:

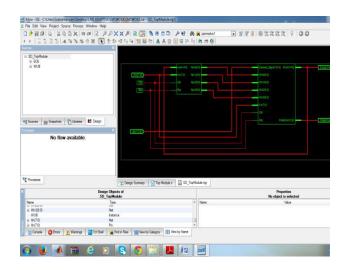

This is the RTL schematic of delayed least mean square. The DLMS having top module the top module consists of err and wub.

ISSN: 2456 - 5083

Fig 8: RTL Schematic Of DLMS Adaptive Filter

### TECHNOLOGY SCHEMATIC OF DLMS ADAPTIVE FILTER:

Fig 9: Schematic Of DLMS Adaptive Filter

The diagram refers to the technology schematic of the delayed least mean square. The diagram is refered as top module, the top module consists of err and wub.

### **MODIFICATION PART:**

A Peer Revieved Open Access International Journal

www.ijiemr.org

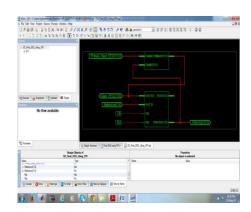

### Fig 10: RTL Schematic Of EEG

This is the RTL schematic of electro electroencephalogram. Hence the eeg having the two blocks. The two block are error compution block and weighted update block.

Fig 11: Technology Schematicof EEG

The diagram refers to the technology schematic of the electroencephalogram. The diagram is refered as top module the top module consists of err and wub.

### **VI.CONCLUSION**

We have proposed an effective expansion plan for internal item processing to diminish the adjustment defer essentially to accomplish quicker union execution and to lessen the discriminating way to bolster high info examining rates. Beside this, we proposed a technique for upgraded adjusted pipelining over the time intensive squares of the structure to decrease the adjustment defer and power utilization, too. The proposed structure included

ISSN: 2456 - 5083

essentially less adjustment postpone and gave huge sparing of ADP and EDP contrasted with the current structures. We proposed a settled point execution of the proposed structural engineering, and determined the expression for unfaltering state blunder and we amplified our work into the use of EEG.

#### VII REFERENCES

- [1]. Pramod Kumar Meher, "Area-Delay-Power Efficient Fixed-Point LMS Adaptive Filter With Low Adaptation Delay", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Vol. 22, No. 2, February 2014.

- [2]. S. Haykin and B. Widrow, *Least-Mean-Square Adaptive Filters*. Hoboken, NJ, USA: Wiley, 2003.

- [3]. M. D. Meyer and D. P. Agrawal, "A modular pipelined implementation of a delayed LMS transversal adaptive filter," in Proc. IEEE Int. Symp. Circuits Syst., May 1990, pp. 1943–1946.

- [4]. G. Long, F. Ling, and J. G. Proakis, "The LMS algorithm with delayed coefficient adaptation," IEEE Trans. Acoust., Speech, Signal Process., vol. 37, no. 9, pp. 1397–1405, Sep. 1989.

- [5]. G. Long, F. Ling, and J. G. Proakis, "Corrections to 'The LMS algorithm with delayed coefficient adaptation'," IEEE Trans. Signal Process., vol. 40, no. 1, pp. 230–232, Jan. 1992.

- [6]. H. Herzberg and R. Haimi-Cohen, "A systolic array realization of an LMS adaptive filter and the effects of delayed adaptation," IEEE Trans. Signal Process., vol. 40, no. 11, pp. 2799–2803, Nov. 1992.

A Peer Revieved Open Access International Journal

www.ijiemr.org

[7]. M. D. Meyer and D. P. Agrawal, "A high sampling rate delayed LMS filter architecture," IEEE Trans. Circuits Syst. II, Analog Digital

Signal Process., vol. 40, no. 11, pp. 727–729, Nov. 1993.

### **AUTHOR 1**

**CH.NAVYA DEEPTHI** Working as assistant professor of ECE, Sri. Sunflower College of Engineering and Technology, Lankapalli. She received the M.Tech degree in Digital electronics and communication Engineering from Dr. Samuel George College of engineering and technology. Markapuram., B.Tech degree in Electronics and Communication Engineering at sindhura college of engineering and technology. Ramagundamand, she has total Teaching Experience (UG and PG) of 6 years.

### **AUTHOR 2**

**P. SANTHAN KUMAR**, ,PG, Dept of ECE (VLSI SD), Sri Sunflower College of Engineering and Technology, B.Tech degree in Electronics and Communication Engineering at Sri Sunflower College of Engineering and Technology, Lankapalli.

ISSN: 2456 - 5083