A Peer Revieved Open Access International Journal

www.ijiemr.org

#### **COPY RIGHT**

2020 IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 20th Jul 2020. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-09&issue=ISSUE-07

Title: AN OPTIMIZED LOWER PART CONSTANT – OR ADDER (OLOCA) FOR ACCURACY IMPROVEMENT AND HARDWARE COST REDUCTION

Volume 09, Issue 07, Pages: 188-196

**Paper Authors**

BHANU PRIYA, K.VENKANNA, M.HARI KRISHNA

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic

Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

# AN OPTIMIZED LOWER PART CONSTANT – OR ADDER (OLOCA) FOR ACCURACY IMPROVEMENT AND HARDWARE COST REDUCTION

<sup>1</sup>BHANU PRIYA, <sup>2</sup>K. VENKANNA, <sup>3</sup>M. HARI KRISHNA

<sup>1</sup>PG SCHOLAR, SREE VAHINI INSTITUTE OF SCIENCE & TECHNOLOGY

<sup>2</sup>Associate. PROFESSOR THE DEPARTMENT OF ECE IN SREE VAHINI INSTITUTE OF SCIENCE & TECHNOLOGY

<sup>3</sup>PROFESSOR & HEAD OF THE DEPARTMENT OF ECE IN SREE VAHINI INSTITUTE OF SCIENCE & TECHNOLOGY

TIRUVURU, KRISHNA DIST, ANDHRA PRADESH, INDIA.

#### **ABSTRACT:**

Misusing the tradeoff among precision and equipment esteem has an incredibly decent ability to upgrade the exhibition of joined frameworks. Utilizing this idea, several surmised adders had been proposed inside the last ten years. Albeit thoughtfully explicit, every first engineering were gotten with an advert hoc and nonsystematic system. Rather, this brief sums up and efficiently enhances a structural layout for estimated adders. Improving Lower part-OR Adder (LOA) efficiently, summing up the LOA structure as an engineering layout and perusing all the attainable decisions to implement that format, an ideal structure for the gave format is gotten that represent considerable authority in infer squared mistake (MSE). The result, known as upgraded lower part consistent OR viper (OLOCA), beats past strategies in expressions of exactness and equipment charge. For instance, an eight-piece estimated viper actualized with our new methodology improves the infer squared bumbles by 58.5%, even as all the while decreasing the expense by 7.2% as for the once referenced quality design. The prevalence of OLOCA over the present inexact adders has been affirmed granting the numerical investigation and correspondingly the utilization of test results.

#### **INTRODUCTION:**

Stochastic figuring has all begun to develop in response to the mulling points of interest of age scaling. As opposed to concealing variants under profoundly estimated safeguard groups, creators have begun to release up customary accuracy requirements and purposefully reveal equipment inconstancy to higher levels of the figuring stack [1]. Rough processing, a promising method to diminish vitality, area, and defer in VLSI format, approximates a machine by utilizing updating its trustworthiness circuit [2]. It abuses the space among the degree of precision required by means of the projects and that provided with the guide of the registering contraption, for arriving at different enhancements.

The specialists in the subject of rough figuring have paid uncommon

A Peer Revieved Open Access International Journal

www.ijiemr.org

enthusiasm to adders, one of the key parts of number juggling circuits. In actuality, a perceptibly enormous wide assortment of surmised adders [3]–[10] had been proposed inside the writing: fragmented adders in which a n-bit viper is isolated into k-bit subadders [3]-[5]; convey select adders wherein two or three submodules are utilized [6], [7]; rough full adders wherein the entire viper is approximated [9], [10]; and theoretical adders which are built upon the explanation that the fundamental way isn't frequently enacted in ordinary adders [11]-[13]. The advanced situation is such, that even a reasonable appraisal of rough adders is a hard endeavor [14], [15]. Albeit the entirety of the structures are adroitly particular, they rate a ordinary capacity: they had been gotten with a specially appointed and nonsystematic technique. A splendid special case is the regular exactness configurable snake (GeAr) that utilizes the possibility of layout [8] yet, isn't prevalent. Among the entirety of the fundamentally combinatorial estimated adders. the abatement component OR snake (LOA) [9] proposes the charming mix-ups instead of equipment expense tradeoff [14], [15]. As might be found in Fig. 1, LOA [9] isolates an n-bit snake into subadders. While the higher enormous subadder incorporates a (nh - 1)- piece careful snake, the diminishing segment subadder is genuinely worked through nl OR doors (bits 0 to nl -1). To produce the convey in sign for the exact snake, an extra AND door is utilized which consolidates the snake contributions of bit work nl, i.E., anl and bnl. The key

position of LOA with preferred acknowledge to various structures equivalent division snake (ESA) [4], blunders open minded viper (ETAII) [5], or then again practically right viper [3] is that the guess is compelled to the least enormous bits, and therefore, the greatness of the mistakes is controlled. The objective of this fast is to upgrade LOA efficiently. To start with, we sum up the LOA structure looking like a compositional layout; at that point, concentrating all the achievable picks to implement that layout, we accomplish a preeminent structure for the provided format gaining practical experience in propose squared bungles (MSE). We name it upgraded LOCA (OLOCA). Since LOA is the prevalent snake a portion of the current inexact adders, our upgraded engineering beats all the predominant inexact adders while pondering the tradeoff between equipment cost and precision. The test evidence articulated in this brief authenticates this fact.

Following the previously mentioned wants, this short is sorted out as follows. Segment II portrays the frameworks of the design format what's more, of OLOCA. A while later, in Section III, we evaluate the advantages of OLOCA the use of trial results; in addition, we approve the scientific equations progressed in Section II. At long last, Section IV finishes up this brief.

#### **RELATED WORD:**

To accomplish deliberately an optimal 1 inexact viper, we improvement in three stages: 1) We portray the mix-up

A Peer Revieved Open Access International Journal

www.ijiemr.org

measurements and equipment cost measuring the great of the design; 2) we sum up the structure of LOA into a more noteworthy conceptual format; and three) we upgrade the layout, in regards to MSE, to deliver OLOCA.

The plan of transportable gadgets requires consideration for stature power admission to ensure unwavering quality and right activity. In any case, the time found the middle value of vitality is oftentimes more significant as it's far directly identified with the battery presence. There are four wellsprings of power scattering in virtual CMOS circuits: exchanging quality, hamper, spillage vitality and static power. The accompanying condition portrays those four parts of solidarity P exchanging is the exchanging power. For a very much planned CMOS circuit, this power issue generally commands, and may represent over ninety% of the full quality. Signifies the progress perspective, which distraction characterized as the basic wide assortment of power expending advances that is made at a hub in a solitary clock period. Versus is the voltage swing, where in most extreme cases it is equivalent to the flexibly voltage, Vdd. CL is the hub capacitance. It very well may be broken into three parts, the entryway capacitance, the dispersion capacitance, and interconnect capacitance. interconnect capacitance is in mainstream a normal for the position and directing. Fck is the recurrence of clock. The exchanging power for static CMOS is determined as follows. During the low to over the top yield progress, the course from Vdd to the yield hub is con-ducting to charge CL. Subsequently, the vitality outfitted by methods for the convey gracefully is

During the low to extreme yield progress, the course from Vdd to the yield hub is con-ducting to expense CL. Thus, the vitality outfitted by methods for the convey supplP short circuit is the short out power. It is a sort of unique vitality and is ordinarily a lot littler than P switching. Isc is alluded to as the immediate course concise circuit present day. It alludes to the directing contemporary from power convey without a moment's delay to ground while each the **NMOS** and **PMOS** transistors are simultaneously exuberant during exchanging. P leakage is the spillage quality. I leakage alludes back to the spillage present day. It is predominantly chosen by utilizing manufacture innovation concerns and begins from assets. The first is the opposite spillage front line of the parasitic channel/sourcesubstrate diodes. This present day is in the request for some femto amperes accordance with diode, which converts into a couple microwatts of power for one million transistors. The second source is the sub edge current of MOSFETs, that is in the request for some nano amperes. For 1,000,000 transistors, the generally speaking sub threshold spillage contemporary results in certain milli watts of intensity.

P static is the static vitality and Istatic is static current. This contemporary emerges from circuits that have a reliable wellspring of contemporary among the force supplies comprising of predisposition

A Peer Revieved Open Access International Journal

www.ijiemr.org

hardware, pseudo-NMOS decision making ability families. For CMOS rationale hover of family members, quality is disseminated best while the circuits move, with out a friction based electricity utilization. Vitality is unprejudiced of the clock recurrence. Decreasing the recurrence will bring down the vitality utilization yet won't change the quality required to play out a given activity, as portrayed by utilizing Eq. (2.Four) and Eq. (2.Five). It is basic to word that the battery ways of life is chosen through utilization, though the vitality dissemination issues are related with the force utilization. There are 4 components that impact the force scattering of CMOS circuits. They are period, circuit format style, structure, and calculation. endeavor of assembly y is

#### RIPPLE CARRY ADDERS:

Concatenating the N full adders forms N bit Ripple carry adder. In this perform of preceding full adder will become the input carry for the following full adder. It calculates sum and bring in line with the subsequent equations. As carry ripples from one complete adder to the other, it traverses longest crucial path and famous worst-case postpone. Si = Ai xor Bi xor Ci Ci+1 = Ai Bi + (Ai + Bi) Ci; where i = 0, 1, ..., n-1RCA is the slowest in all adders (O (n) time) but it's miles very compact in length (O (n) location). If the ripple deliver adder is carried out by concatenating N full adders, the put off of such an adder is 2N gate delays from Cin to Cout. The postpone of adder increases linearly with increase in quantity of bits. Block diagram of RCA is shown in determine 1.

#### CARRY SKIP ADDER

A deliver bypass divides the phrases to be delivered in to corporations of equal length of k-bits. Carry Propagate pi alerts can be used inside a set of bits to accelerate the carry propagation. If all of the pi indicators within the organization are pi=1, carry bypasses the entire group as shown in determine 2.

$$P = pi * pi+1 * pi+2 * ... pi + ok$$

In this manner postpone is decreased in comparison to ripple carry adder. The worst-case deliver propagation delay in a N-bit deliver skip adder with constant block width b, assuming that one degree of ripple has the identical postpone as one pass, can be derived:

$$TCSKA = (b-1)+zero.5+(N/b-2)+(b-1) = 2b + N/b$$

Block width rather influences the latency of adder. Latency is immediately proportional to dam width. More quantity of blocks manner block width is less, therefore more postpone. The idea behind Variable Block Adder (VBA) is to limit the important path postpone in the deliver chain of a bring pass adder, whilst permitting the businesses to take unique sizes. In case of convey pass adder, such condition will bring about more quantity of skips among degrees.

A Peer Revieved Open Access International Journal

www.ijiemr.org

#### **EXPERIMENTAL RESULTS:**

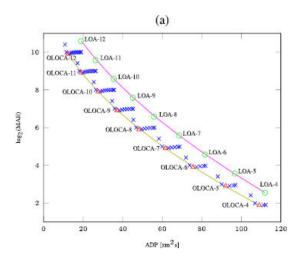

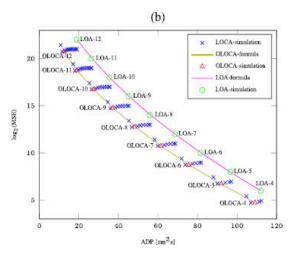

To research the circuit attributes and look at the advertised structures in Section II, we've produced VHDL depiction of the adders. Various designs of these adders are combined in a modern low-power sixty five-8-piece library, for sixteen-and operands. Utilizing returned-commented on reenactments, dynamic quality dispersal of the adders is assessed after blend for the recurrence = 1 GHz. Wave bring adders are utilized as the subadders of all the inexact adders. All the adders have been recreated for 107 consistently dispensed arbitrary enter designs. In this stage, each snake's name is went with by means of one number. For ESA and ETAII, this wide assortment is the size of the equivalent portions. With respect to and OLOCA, the number is the scale of the lessening tremendous subadder; i.E., nl . So as to check the exactness of the equations, just as looking at the snake structures, the blunder versus estimation of the adders for restrictive estimations of nl s are delineated in Fig. Four. MAE and MSE rather than region defer item (ADP) of the 16-piece adders are demonstrated diagrams. LOCA has been reproduced for restrictive scope of constants in each nl case. As can be found in the diagrams, evolving Or then again doors with Cte-1s declines the MAE and MSE values and on the same time the ADP; the design keeps up till the factor where two OR doors keep on being. After that point, the mistake esteems start expanding even as the expense of the snake diminishes. As a final product, the head engineering, considering the mistake value

tradeoff, is gotten holding two OR entryways furthermore, trading Cte-1s for the unwinding of two-to-1 squares. This checks the discourse in Section II that the most appropriate structure has two OR doors. Supplanting all the 2-to-1 squares with Cte-1s prominently blast the mistake esteems. Albeit, changing the entirety of the 2-to-1 squares with Cte-1s impacts in a structure which stays higher that of LOA; it isn't the most astounding design as appeared in Fig. 4. It likewise can be obvious that the OLOCA's and LOA's plan (see Table III) consummately are expecting the direct of the adders for all nl s. Also, for all nl s, OLOCA beats LOA, both from cost and botches perspectives; for the Equivalent estimations of missteps, OLOCA improves the worth practically 25% and for similar estimations of significant worth, the error estimations of OLOCA are nearly half of the LOAs. As an occurrence, a sixteen-piece OLOCA-8 improves the cost through 13.6%, MAE by utilizing 37.4%, and MSE by 58% in appraisal with LOA-eight. So as to assess OLOCA with some other bitwidth, we have considered eight-piece adders also; the results are classified the exactness of the gave recipes rather than the recreation results, notwithstanding the predominance of OLOCA over LOA for all nl s. As an occurrence, OLOCA-four improves MAE by methods for 36.Nine%, MSE through fifty eight.5%, and expense by means of 7.2% in correlation with LOA-4. To show the predominance of OLOCA over all the current estimated adders, with the exception of LOA, we recollect ESA, ETAII, and

A Peer Revieved Open Access International Journal

www.ijiemr.org

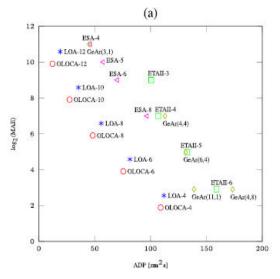

GeAr. Among the present combinational surmised adders, the previously mentioned structures have demonstrated to have the top notch execution [14], [15] after LOA. Various setups of the adders had been

recreated and the impacts are delineated portrays the MAE of the adders instead of ADP. So also, MSE instead of vitality delay item (PDP) of the viper designs is outlined.

Comparison of 16-bit LOA and OLOCA synthesized in a 65-nm technology: simulation and formulas results. (a) MAE versus ADP.(b) MSE versus ADP.

Comparison of 16-bit approximate adders synthesized in a commercial 65-nm technology with various configurations. (a) MAE versus ADP. (b) MSE versus PDP.

A Peer Revieved Open Access International Journal

www.ijiemr.org

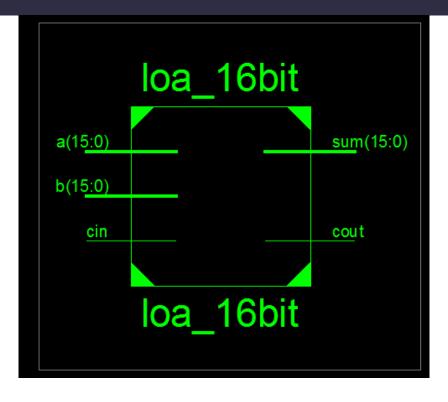

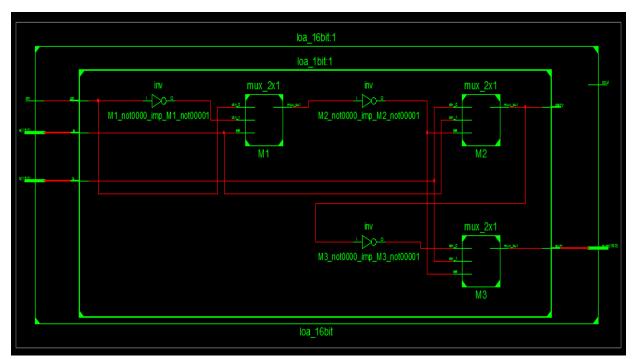

RTL Block Diagram

Internal Block Diagram

A Peer Revieved Open Access International Journal

www.ijiemr.org

|                      |       |      |            |        |        | 1,000.000 ns |

|----------------------|-------|------|------------|--------|--------|--------------|

| Name                 | Value | 0 ns | <br>200 ns | 400 ns | 600 ns | 800 ns       |

| ▶ <b>ा</b> sum[15:0] | 3334  | 21   |            | 3334   |        |              |

| ▶ 🐻 a[15:0]          | 1111  | 10   |            | 1111   |        |              |

| ▶ 🚮 b[15:0]          | 2222  | 10   |            | 2222   |        |              |

| √ cin                | 1     |      |            |        |        |              |

|                      |       |      |            |        |        |              |

Simulation Results

In spite of the fact that ESA is equipment effective, it's miles the least precise viper structure. For instance, for the about equivalent estimation of ADP, OLOCA-eight improves the blunder cost by utilizing ninety seven% in Assessment with ESA-four. OLOCA-eight improves slip-ups, ADP, and PDP through fifty three%, 54.Nine%, and forty two.6% as contrasted and ETAII-4, separately. The overhauls for the MSE are significantly bigger.

#### **CONCLUSION:**

In this short, a biggest rough viper, through summing up an structural layout for surmised adders, has been proposed. The proposed viper OLOCA shows broad advancement in each errors and equipment cost measurements conversely with the once in the past articulated top notch designs. The prevalence of OLOCA over the current rough adders has been built up offering the scientific assessment and likewise the utilization of trial results. As a case, a 16-piece estimated snake did with the OLOCA approach improves MSE by methods for fifty eight% simultaneously as diminishing the ADP by means of thirteen.8% at the

equivalent time, in evaluation with an estimated viper applied with the LOA technique.

#### **REFERENCES:**

- [1] J. Sartori and R. Kumar, "Stochastic figuring," Found. Patterns Electron. Structure Autom., vol. 5, no. 3, pp. 153–210, Mar. 2011.

- [2] S. Mittal, "A review of methods for estimated processing," ACM Comput. Surv., vol. 48, no. 4, pp. 62-1–62-33, Mar. 2016.

- [3] A. B. Kahng and S. Kang, "Precision configurable viper for estimated number-crunching plans," in Proc. 49th Annu. Structure Autom. Conf. (DAC), Jun. 2012, pp. 820–825.

- [4] D. Mohapatra, V. K. Chippa, A. Raghunathan, and K. Roy, "Plan of voltage-adaptable meta-capacities for rough figuring," in Proc. Plan, Autom. Test Eur., Mar. 2011, pp. 1–6.

- [5] N. Zhu, W. L. Goh, and K. S. Yeo, "An improved low-power fast viper for mistake open minded application," in Proc. twelfth

A Peer Revieved Open Access International Journal

www.ijiemr.org

Int. Symp. Integr. Circuits, Dec. 2009, pp. 69–72.

[6] K. Du, P. Varman, and K. Mohanram, "Elite dependable variable inactivity convey select expansion," in Proc. Structure, Autom., Test Eur. Conf. Show. (DATE), Mar. 2012, pp. 1257–1262.

[7] I. C. Lin, Y. M. Yang, and C. C. Lin, "Superior low-power convey theoretical expansion with variable dormancy," IEEE Trans. Large Scale Integr. (VLSI) Syst., vol. 23, no. 9, pp. 1591–1603, Sep. 2015.

[8] M. Shafique, W. Ahmad, R. Hafiz, and J. Henkel, "A low inactivity nonexclusive precision configurable snake," in Proc. 52nd ACM/EDAC/IEEE Design Autom. Conf. (DAC), Jun. 2015, pp. 1–6.

[9] H. R. Mahdiani, A. Ahmadi, S. M. Fakhraie, and C. Lucas, "Bio-motivated uncertain computational squares for proficient VLSI execution of delicate registering applications," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 57, no. 4, pp. 850–862, Apr. 2010.

[10] V. Gupta, D. Mohapatra, A. Raghunathan, and K. Roy, "Low-power advanced signal handling utilizing surmised adders," IEEE Trans. Comput.- Helped Design Integr. Circuits Syst., vol. 32, no. 1, pp. 124–137, Jan. 2013.

[11] A. K. Verma, P. Lively, and P. Ienne, "Variable inertness theoretical expansion: another worldview for number juggling circuit plan," in Proc. Conf. Structure,

Autom. Test Eur. (DATE), Mar. 2008, pp. 1250–1255.

[12] S.- L. Lu, "Accelerating preparing with estimation circuits," Computer, vol. 37, no. 3, pp. 67–73, Mar. 2004.

#### **Student Details:**

BHANU PRIYA ,M.Tech SreeVahini Institute of Science & Technology.

#### **Guide Details:**

K Venkanna Associate.Professor the Department of ECE, in SreeVahini Institute of Science & Technology.

M.HariKrishna, Professor & Head of the Department of ECE, in SreeVahini Institute of Science & Technology.

A Peer Revieved Open Access International Journal

www.ijiemr.org