A Peer Revieved Open Access International Journal

www.ijiemr.org

### **COPY RIGHT**

2019IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 16<sup>th</sup> Nov 2019. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-08&issue=ISSUE-11

Title IMPLEMENTATION OF (ROBA) ROUNDING BASED APPROXIMATION

MULTIPLIER ARCHITECTURE FOR IMAGE SHARPENING AND SMOOTHING

Volume 08, Issue 11, Pages: 56-64.

**Paper Authors**

#### T. SUNEETHA, SK. HUSSIN

VAHINI INSTITUTE OF SCIENCE &TECHNOLOGY TIRUVURU, KRISHNA DIST, ANDHRA PRADESH, INDIA.

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic

Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

# IMPLEMENTATION OF (ROBA) ROUNDING BASED APPROXIMATION MULTIPLIER ARCHITECTURE FOR IMAGE SHARPENING AND SMOOTHING

<sup>1</sup>T. SUNEETHA, <sup>2</sup>SK. HUSSIN

<sup>1</sup>PG SCHOLAR, VAHINI INSTITUTE OF SCIENCE & TECHNOLOGY <sup>2</sup>PROFESSOR DEPARTMENT OF ECE IN VAHINI INSTITUTE OF SCIENCE &TECHNOLOGY TIRUVURU, KRISHNA DIST, ANDHRA PRADESH, INDIA.

#### **ABSTRACT:**

In this paper, we propose an inexact multiplier that is rapid yet vitality proficient. The methodology I s to adjust the operands to the closest type of two. Along these lines the computational escalated some portion of the duplication is excluded improving pace and vitality utilization at the cost of a little blunder. The proposed methodology is material to both marked and unsigned increases. We propose three equipment usage of the estimated multiplier that incorporates one for the unsigned and two for the marked tasks. The productivity of the proposed multiplier is assessed by looking at its exhibition with those of some surmised and precise multipliers utilizing diverse plan parameters. Furthermore, the viability of the proposed inexact multiplier is contemplated in two picture handling applications, i.e., picture honing and smoothing.

#### **INTRODUCTION:**

ENERGY minimization is one of the principle structure necessities in practically any electronic frameworks, particularly the convenient ones, for example, PDAs, tablets, and unique devices [1]. It is profoundly wanted to accomplish this minimization with insignificant execution (speed) punishment [1]. Advanced signal preparing (DSP) squares are key parts of these convenient gadgets for acknowledging different sight and sound applications. The computational center of these squares is the number juggling rationale unit where duplications have the best offer among all number-crunching activities performed in these DSP frameworks [2]. In this manner, improving the speed and power/vitality

effectiveness qualities of multipliers assumes a key job in improving the productivity of processors. A considerable lot of the DSP centers actualize picture and video handling calculations where last yields are either pictures or recordings arranged for human utilizations. This reality empowers us to use approximations for improving the speed/vitality effectiveness. This starts from the restricted perceptual capacities of human creatures in watching a picture or a video. Notwithstanding the picture and video preparing applications, there are different zones where the precision of the number juggling activities isn't basic to usefulness of the framework (see [3], [4]). Being capable to utilize the surmised

A Peer Revieved Open Access International Journal

www.ijiemr.org

processing gives the originator the capacity of making tradeoffs between the precision and the speed just as power/vitality utilization [2], [5]. Applying the estimation to the math units can be performed at various structure reflection levels including circuit, rationale, and design levels, just as calculation what's more, programming layers [2]. The estimate might be performed utilizing various systems, for example, permitting some planning infringement (e.g., voltage overscaling or overclocking) and work guess techniques (e.g., altering the Boolean capacity of a circuit) or a mix of them [4], [5]. In the class of capacity estimate strategies, various approximating math building squares, for example, adders and multipliers, at various plan levels have been proposed (see [6]-[8]). In this paper, we center around proposing a rapid lowpower/ vitality yet surmised multiplier fitting for blunder strong DSP applications. The proposed estimated multiplier, which is likewise territory effective, is developed by changing the regular duplication approach at the calculation level accepting adjusted input esteems. We call this adjusting based estimated (RoBA) multiplier. The proposed duplication approach is relevant to both marked and unsigned increases for which three enhanced structures are exhibited. The efficiencies of these structures are evaluated by looking at the deferrals, power and vitality utilizations, vitality defer items (EDPs), and regions with those of some estimated and precise (accurate) multipliers. The commitments of this paper can be condensed as pursues:

- 1) exhibiting another plan for RoBA augmentation by changing the regular augmentation approach;

- 2) portraying three equipment structures of the proposed rough duplication conspire for sign and unsigned activities.

#### PRIOR WORKS

In this area, a portion of the past works in the test of inexact multipliers are in no time inspected. In [3], an approx-imate multiplier and a rough viper primarily dependent on a tech-nique named broken-cluster multiplier (BAM) had been proposed. By utilizing two the two BAM estimation two technique two of [3] to the regular changed Booth multiplier, inexact an marked Booth multiplier was once presented in [5]. The multiplier inexact provided quality utilization financial investment funds shape 28% to 58.6% and area mark downs from 19.7% to 41.8% for exceptional expression lengths conversely with a typical Booth multiplier. Kulkarni et al. [6] suggested a rough multiplier con-sisting two of two an assortment of 2 erroneous setting up hinders that spared the power through 31.8%-45.4% over a right multiplier. A surmised marked 32-piece multiplier for theory purposes in pipelined processors used to be when planned in [7]. It was once 20% quicker than full-snake based tree multiplier simultaneously as having a probability of mistake of round 14%. In [8], a mistake tolerant multiplier, which registered the estimated stop final product by method for separating the duplication into one right and one surmised part, used to be presented, in which the correctnesses for unique piece widths have been accounted for. On account of a 12-piece multiplier, a vitality sparing of

A Peer Revieved Open Access International Journal

www.ijiemr.org

extra than half was once detailed. In [9], two inexact 4:2 blowers for utilizing in a regular Dadda multiplier were structured and investigated.

The utilization of estimated multipliers in photograph preparing applications, which prompts deal rates in quality utilization, postponement, transistor depend interestingly with these of a specific multiplier configuration, has been talked about in the writing. In [10], a precision configurable multiplier shape (ACMA) used to be prompted for mistake strong frameworks. To improve its throughput, the ACMA utilized a methodology alluded to as convey in expectation that worked put together absolutely completely with respect to a precomputation rationale. When in qualification with the genuine one, the proposed surmised increase brought about almost half markdown dormancy through bringing down quintessential way. Likewise, Bhardwaj et al. [11] an inexact Wallace tree multiplier (AWTM). Once more, it summoned the convey in expectation to diminish the basic way. In this work, AWTM used to be utilized in a constant benchmark picture utility appearing about 40% and 30% imprint downs in the power and zone, separately, with no photograph wonderful misfortune interestingly with the instance of the utilization of a correct Wallace tree multiplier (WTM) structure.

In [12], rough unsigned augmentation and division dependent on an estimated logarithm of the operands two have two been proposed. In the proposed duplication, the summation of the rough logarithms decides the final product of the

activity. Henceforth, the increase is streamlined to some move and include activities. In [13], a strategy for developing the precision of the increase approach of [12] used to be once proposed. It was once put together absolutely with respect to the disintegration of the enter operands. This procedure radically quickened the regular mistake at the expense of expanding the equipment of the rough multiplier by means of capability of around multiple times.

In [16], a powerful stage system (DSM) is displayed, which plays out the augmentation activity on a m-bit stage starting from the primary one piece of the enter operands. A dynamic differ impartial multiplier (DRUM) multiplier, which chooses a m-bit segment starting from the fundamental one piece of the information operands and units the least enormous piece of the truncated qualities to one, has been proposed in [17]. In this the truncated qualities structure, quickened and moved to left to produce the end yield. In [18], a surmised 4 WTM has been recommended that utilizes an incorrect 4:2 counter. Likewise, a mistake adjustment unit for remedying the yields has been recommended. To two accumulate bigger multipliers, this four 4 off base Wallace multiplier can be utilized in an exhibit structure. The majority of the previously proposed rough multipliers are put together absolutely totally with respect to each upgrading the shape or multifaceted nature markdown of an exact precise multiplier. In this paper, identified with [12], we advocate playing out the inexact duplication through disentangling the activity. The differentiation between our work and [12] is that, despite the fact that the thoughts in

A Peer Revieved Open Access International Journal

www.ijiemr.org

every work are almost comparative for unsigned numbers, the mean mistake of our proposed system is littler. What's more, we advocate some estimation methods when the increase is performed for marked numbers.

## PROPOSED APPROXIMATE MULTIPLIER

A. Multiplication Algorithm of RoBA Multiplier

The primary thought behind the proposed surmised multiplier is to utilize the simplicity of activity when the numbers are two to the power n (2n). To expound on the activity of the surmised multiplier, first, let us indicate the adjusted quantities of the contribution of An and B by  $A_{\rm r}$  and  $B_{\rm r}$ , individually. The increase of A by B might be revised as

$$A \times B = (A_r - A) \times (B_r - B) + A_r \times B + B_r$$

$$\times A - A_r \times B_r.$$

The key perception is that the increases of Ar Br, Ar B, and Br A might be executed just by the move oper-ation. The equipment execution of ( Ar A) notwithstanding, is fairly unpredictable. The heaviness of this term in the conclusive outcome, which relies upon contrasts of the precise numbers from their adjusted ones, is regularly little. Thus, we propose to discard this part from (1), improving the increase activity. Subsequently, to play out the duplication procedure, the accompanying articulation is utilized:

$$A \times B \sim = A_r \times B + B_r \times A - A_r \times B_r$$

.

Accordingly, one can play out duplication activity utilizing three move and two expansion/subtraction tasks. In this methodology, the closest qualities for An and B as 2n ought to be resolved. At the point when the estimation of An (or B) is equivalent to the 3 2 p-2 (where p is a subjective positive whole number bigger than one), it has two closest qualities as 2n with equivalent supreme contrasts that are 2 p and 2 p-1. While the two qualities lead to a similar impact on the exactness of the proposed multiplier, choosing the bigger one (with the exception of the instance of p 2) prompts a littler equipment execution for deciding the closest adjusted worth, and thus, it is considered in this paper. It begins from the way that the numbers as 3 2 p-2 are considered as couldn't care less in both gathering together and down rearranging the procedure, and littler rationale articulations might be accomplished in the event that they are utilized in the gathering together.

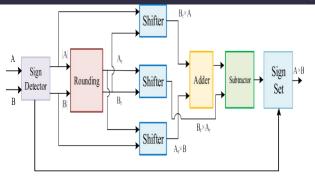

## **B.Hardware Implementation of RoBA Multiplier:**

In view of (2), we give the square graph to the equipment execution of the proposed multiplier in Fig. 1 where the information sources are spoken to in two's supplement position. In the first place, the indications of the sources of info are resolved, and for each

A Peer Revieved Open Access International Journal

www.ijiemr.org

negative worth, the outright worth is produced. Next, the adjusting square extricates the closest incentive for every supreme incentive as 2n. It ought to be noticed that the bit width of the yield of this square is n (the most noteworthy piece of the supreme estimation of a n-bit number in the two's supplement group is zero). To discover the closest estimation of information A, we utilize the accompanying In the proposed condition, Ar [i] is one of every two cases. In the main case, A[i] is every last one the bits on its left side are zero while A[i 1] is zero. In the subsequent case, when A[i] and all its left-side bits are zero, A[i 1] and A[i 2] are both one. Having decided the adjusting esteems, utilizing three barrel shifter hinders, the items Ar Br, Ar B, and Br An are determined. Consequently, the measure of moving is resolved dependent on logAr 1 (or logBr 1) on account of An (or B) operand. Here, the info bit width of the shifter squares is n, while their yields are 2n. A solitary 2n-bit Kogge-Stone snake is utilized to ascertain the summation of Ar B and Br A. The yield of this viper and the aftereffect of Ar Br are the contributions of the subtractor hinder whose yield is the total estimation of the yield of the proposed multiplier. Since Ar and Br are as 2n, the contributions of the subtractor may take one of the three info designs appeared in Table I. The relating yield designs are likewise appeared The types of the information sources and yield roused us to consider a straightforward circuit dependent on the accompanying articulation: On account of the AS-RoBA multiplier, the blunder incorporates an extra term because of the surmised nullification (inexact refutation).

Consequently, in the most pessimistic scenario (where the two data sources are negative), one may get the greatest mistake from sponding circuit for executing this articulation is littler and quicker than the ordinary subtraction circuit. At long last, if the indication of the last duplication result ought to blunder

$(A,B) = (A^{T}r - A^{T})(B^{T}r - B^{T})$  Stomach muscle

Stomach muscle be negative, the yield of the subtractor will be discredited in the sign set square. To discredit esteems, which have the two's comple-ment portrayal, the comparing circuit dependent on X-1 ought to be utilized. To build the speed of nullification activity, one may avoid the incrementation procedure in the invalidating stage by tolerating its related mistake. As will be seen later, the significance of the mistake diminishes as the information widths increments. In this paper, if the invalidation is performed precisely (approxi-mately), the usage is called marked RoBA (S-RoBA) multiplier [approximate S-RoBA (AS-RoBA) multiplier]. For the situation where the sources of info are constantly positive, to expand the speed and lessen the power utilization, the sign detec-tor and sign set squares are discarded from the engineering, furnishing us with the design called unsigned RoBA (U-RoBA) multiplier. For this situation, the yield width of the adjusting square is n 1 where this bit is resolved dependent on A<sub>r</sub> n A n 1 A n 2. This is on the grounds

A Peer Revieved Open Access International Journal

www.ijiemr.org

#### RESULTS AND DISCUSSION

### **A.Hardware Implementation**

To assess the adequacy of the proposed multiplier, the three RoBA multiplier executions were contrasted and some rough and definite multipliers. Baugh Wooley dependent on Wallace tree design (as a careful marked) and Wallace (as a definite unsigned) multipliers were chosen as the accurate multipliers. Additionally, on account of inexact multipliers, DSM8 [16], DRUM6 [17], and HAAM [18] were picked. Since [12] has not given any equipment execution,

we avoided it from this piece of the examination. The multipliers were executed Verilog utilizing equipment portrayal language and afterward orchestrated utilizing Synopsys plan compiler with the choice of combining with the base postpone objective under a 45-nm innovation [14]. Next, the postlayout plan parameters of the considered multipliers were extricated by misusing Cadence framework on-chip The experience. removed structure parameters of these multipliers accounted for in Table VI. It ought to be referenced that in this paper, the inventory voltage was 1.1 V (in light of the NanGate innovation while 45-nm [14]),recurrence was chosen utilizing the revealed postponement for every multiplier (see Table VI).

The outcomes uncover that the base postponement, vitality, and EDP have a place with the U-RoBA while DSM8 has the best power utilization and DRUM8 has the base region and PDA. The deferral, vitality, and EDP of the U-RoBA are about 22% (15%), 5% (13%), and 26% (25%) lower

DSM8 (DRUM6). than those of Interestingly, the power (territory and PDA) of DSM8 (DRUM6) is (are) about 18% (57% and 51%) lower. Additionally, the nullification activity prompts bigger structure parameters for S-RoBA and AS-RoBA contrasted and those of U-RoBA, DSM8, and DRUM6. Additionally, HAAM has the most noticeably awful plan parameters because of its cluster structure.

The outcomes additionally show that the definite multipliers have extensively bigger structure parameters contrasted and those of the proposed U-RoBA and AS-RoBA. On account of the S-RoBA multiplier, the postponement is, all things considered, 3.4% bigger than that of the Baugh Wooley multiplier because of the utilization of the definite invalidation activity. With the exception of the postponement parameter, other plan parameters of the S-RoBA multiplier are superior to those of the Bough Wooley multiplier. Then again, the power, zone, vitality, EDP, and PDA of the S-RoBA multiplier, are about 47%, 32%, 45%, 43%, and 63%, individually, lower than those of the Bough Wooley multiplier. At long last, Table VII shows the breakdown of the power, postponement, and region of various units of both the AS-RoBA and S-RoBA multipliers. As the outcomes uncover, the shifter unit has the most elevated postponement, power, and territory among the units of the multipliers.

#### **B.Image Processing Applications**

To assess the plausibility of the proposed multiplier in genuine applications, we thought about the exhibitions of the RoBA multiplier architectures in two image processing applications of smoothing and

A Peer Revieved Open Access International Journal

www.ijiemr.org

sharpening with those of the corresponding exact ones. For sharpening, two different methods were invoked. In the first one, each pixel of the sharp image was extracted from where the X(i, j) [Y (i, j)] indicates the pixel of the i th row and j th column of input (output) image and  $Mask_{sharpening,1}$  is an  $n \times n$  coefficient sharpening matrix given by

In the second method, each output pixel is determined from On account of MaskSharpening,1, every one the estimations of the network are certain, and subsequently, all the three RoBA multiplier archi-tectures lead to similar outcomes, while on account of the Masksharpening,2, both Sa-RoBA and AS-RoBA multipliers might be used prompting distinctive picture characteristics.

Initially, for instance, consider the honing

depicted above for the first picture of Vd-Orig appeared in Fig. 3. The honed pictures for the second approach when the careful multiplier, S-RoBA multiplier, and ASmul-tiplier utilized RoBA were are additionally given in Fig. 3(b)– (d). As the pinnacle signal-to-clamor proportion (PSNR) and mean auxiliary likeness record metric (MSSIM [20]) of the honed pic-tures for the two honing lattices for seven pictures in Table VIII. It ought to be noticed that the detailed PSNRs are resolved dependent on looking at the honed picture acquired utilizing the accurate multipliers to the honed picture got utilizing the considered rough multiplier structures. Additionally, the MSSIM esteems more like one show higher characteristics for the rough yield picture.

As the outcomes appear, on account of the positive numbers, the normal of PSNR (MSSIM) of the proposed multiplier is in

excess of 43 dB (0.99). In spite of the fact that, on account of negative num-bers, the nature of the pictures is lower, the PSNRs (MSSIM) in every one of the cases are in excess of 20 dB (0.91), which is worthy in numerous applications [15]. In every one of the benchmarks, the DSM8 gives the most noteworthy yield quality giving a similar exhibition as that of the careful duplication that has the PSNR estimations of . The Mitchell multiplier underpins just the unsigned activity, and thus, its outcomes have been accounted for just for the first honing calculation. The outcomes uncover the most reduced quality for this multiplier. Likewise, our proposed surmised multiplier yields higher (lower) yield PSNR values contrasted and those of the DRUM6 on account of the principal (second) honing calculation.

For the second utilization of the smoothing, we have used the accompanying condition to decide the smoothed yield picture Here, again X(i, j) [Y(i, j)] is the pixel of the i th row and j th column of input (output) Mask<sub>Smoothing</sub> is an  $n \times n$ coefficient smoothing matrix given by Since each coefficient is sure, all the three RoBA multiplier models lead to a similar yield picture quality. Table IX shows the PSNR and MSSIM of the smoothing procedure utilizing the considered surmised multiplier structures for the seven pictures contrasted and the instance of utilizing the careful multiplier. As the outcomes uncover, all the PSNRs (MSSIMs) are higher than 40 (0.99) showing little blunders for the proposed multiplier. The yield nature of the RoBA in all the benchmark pictures is superior to those of the DRUM6 and

A Peer Revieved Open Access International Journal

www.ijiemr.org

multipliers. Be that as it may, like the honing application, the DSM8 multiplier gives the most noteworthy yield quality.

### **CONCLUSION**

In this paper, we proposed a fast yet vitality proficient inexact multiplier called RoBA multiplier. The proposed multiplier, which had high precision, depended on adjusting of the contributions to the type of 2n. Thusly, the computational serious piece of the augmentation was excluded improving pace and vitality utilization at the cost of a little blunder. The proposed methodology was material to both marked and unsigned duplications. Three equipment executions of the rough multiplier including one for the unsigned and two for the marked activities were talked about. The efficiencies of the proposed multipliers were assessed by contrasting them and those of some precise and rough multipliers utilizing diverse plan parameters. The outcomes uncovered that, in generally (all) cases, the RoBA multiplier designs out-played out the relating surmised (careful) multipliers. Additionally, adequacy of the proposed estimated increase approach was considered in two picture preparing uses of honing and smoothing. The examination uncovered similar picture characteristics as those of accurate increase calculations.

#### REFERENCES

- [1] M. Alioto, "Ultra-low power VLSI circuit configuration demystified and clarified: An instructional exercise," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 59, no. 1, pp. 3–29, Jan. 2012.

- [2] V. Gupta, D. Mohapatra, A. Raghunathan, and K. Roy, "Low-control advanced sign handling utilizing inexact

- adders," IEEE Trans. Comput.- Aided Design Integr. Circuits Syst., vol. 32, no. 1, pp. 124–137, Jan. 2013.

- [3] H. R. Mahdiani, A. Ahmadi, S. M. Fakhraie, and C. Lucas, "Bio-propelled loose computational squares for proficient VLSI usage of delicate processing applications," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 57, no. 4, pp. 850–862, Apr. 2010.

- [4] R. Venkatesan, A. Agarwal, K. Roy, and A. Raghunathan, "MACACO: Modeling and examination of circuits for inexact registering," in Proc. Int. Conf. Comput.-Aided Design, Nov. 2011, pp. 667–673.

- [5] F. Farshchi, M. S. Abrishami, and S. M. Fakhraie, "New inexact multiplier for low power advanced sign handling," in Proc. seventeenth Int. Symp. Comput. Archit. Digit. Syst. (Creeps), Oct. 2013, pp. 25–30.

- [6] P. Kulkarni, P. Gupta, and M. Ercegovac, "Exchanging exactness for control with an underdesigned multiplier design," in Proc. 24th Int. Conf. VLSI Design, Jan. 2011, pp. 346–351.

- [7] D. R. Kelly, B. J. Phillips, and S. Al-Sarawi, "Estimated marked paired whole number multipliers for math information esteem hypothesis," in Proc. Conf. Plan Archit. Signal Image Process., 2009, pp. 97–104.

- [8] K. Y. Kyaw, W. L. Goh, and K. S. Yeo, "Low-control fast mul-tiplier for mistake tolerant application," in Proc. IEEE Int. Conf. Electron Devices Solid-State Circuits (EDSSC), Dec. 2010, pp. 1–4.

- [9] A. Momeni, J. Han, P. Montuschi, and F. Lombardi, "Plan and examination of inexact blowers for augmentation," IEEE

A Peer Revieved Open Access International Journal

www.ijiemr.org

Trans. Comput., vol. 64, no. 4, pp. 984–994, Apr. 2015.

[10] K. Bhardwaj and P. S. Mane, "ACMA: Accuracy-configurable multi-plier design for mistake flexible framework on-chip," in Proc. eighth Int. Workshop Reconfigurable Commun.- Centric Syst.-Chip, 2013, pp. 1–6.

[11] K. Bhardwaj, P. S. Mane, and J. Henkel, "Power-and region proficient rough wallace tree multiplier for mistake flexible frameworks," in Proc. fifteenth Int. Symp. Quality Electron. Structure (ISQED), 2014, pp. 263–269.

[12] J. N. Mitchell, "PC increase and division utilizing paired log-arithms," IRE Trans. Electron. Comput., vol. EC-11, no. 4, pp. 512–517, Aug. 1962.

[13] V. Mahalingam and N. Ranganathan, "Improving precision in Mitchell's logarithmic duplication utilizing operand disintegration," IEEE Trans. Comput., vol. 55, no. 12, pp. 1523–1535, Dec. 2006.

[14] Nangate 45nm Open Cell Library, got to on 2010. [Online]. Benefit capable: http://www.nangate.com/

[15] H. R. Myler and A. R. Weeks, The Pocket Handbook of Image Process-ing Algorithms in C. Englewood Cliffs, NJ, USA: Prentice-Hall, 2009.

[16] S. Narayanamoorthy, H. A. Moghaddam, Z. Liu, T. Park, and N. S. Kim, "Vitality productive surmised duplication for advanced sign procedure ing and order applications," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 23, no. 6, pp. 1180–1184, Jun. 2015.

[17] S. Hashemi, R. I. Bahar, and S. Reda, "DRUM: A unique range fair multiplier for inexact applications," in Proc. IEEE/ACM Int. Conf. Comput.- Aided Design (ICCAD), Austin, TX, USA, 2015, pp. 418–425.

[18] C.- H. Lin and I.- C. Lin, "High exactness estimated multiplier with blunder amendment," in Proc. 31st Int. Conf. Comput. Structure (ICCD), 2013, pp. 33–38. [19] A. B. Kahng and S. Kang, "Exactness configurable snake for approximate number juggling plans," in Proc. 49th Design Autom. Conf. (DAC), Jun. 2012, pp. 820–825.

[20] Z. Wang, A. C. Bovik, H. R. Sheik, and E. P. Simoncelli, "Picture quality evaluation: From mistake perceivability to auxiliary likeness," IEEE Trans. Picture Process., vol. 13, no. 4, pp. 600–612, Apr. 2004.

[21] J. Liang, J. Han, and F. Lombardi, "New measurements for the unwavering quality of surmised and probabilistic adders," IEEE Trans. Comput., vol. 62, no. 9, pp. 1760–1771, Sep. 2013.

#### Guide Details:

SK. Husseni, Assis. Professor the Department of ECE, in Sree Vahini Institute of Science & Technology.

#### **Student Details:**

T. SUNEETHA, M.Tech in Sree Vahini Institute of Science & Technology.