A Peer Revieved Open Access International Journal

www.ijiemr.org

### **COPY RIGHT**

2019IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 23<sup>rd</sup> Nov 2019. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-08&issue=ISSUE-11

Title STANDARD BASIC CODE BASED ENCODING/DECODING WITH AND OPERATION FOR NETWORK ON-CHIP COMMUNICATION

Volume 08, Issue 11, Pages: 147-152.

**Paper Authors**

### PATTAPAGALU POSHI, P.NAGA RAJU

KAKINADA INSTITUTE OF ENGINEERING AND TECHNOLOGY.KORANGI.ANDHRAPRADESH.INDIA.533461

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic

Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

# STANDARD BASIC CODE BASED ENCODING/DECODING WITH AND OPERATION FOR NETWORK ON-CHIP COMMUNICATION

<sup>1</sup>PATTAPAGALU POSHI, <sup>2</sup>P.NAGA RAJU

<sup>1</sup>M.TECH VLSID, DEPT OF E.C.E, KAKINADA INSTITUTE OF ENGINEERING AND TECHNOLOGY, KORANGI, ANDHRAPRADESH, INDIA, 533461

<sup>2</sup>ASSOSIATE PROFESSOR, KAKINADA INSTITUTE OF ENGINEERING AND TECHNOLOGY, KORANGI, ANDHRAPRADESH, INDIA, 533461

#### **Abstract**

Code Division Multiple Access (CDMA) is proposed as the physical layer enabler of Network-On-Chip (NoC) interconnects for its prominent features such as fixed latency, guaranteed service, and reduced system complexity. CDMA interconnects have been adopted by the NoC community as it originates in wireless communications where each bit in a CDMA encoded data word is transmitted on a separate channel to avoid interference. However, the wireless interference problem can be efficiently mitigated in on-chip interconnects eliminating the need for replicating the CDMA channel. Moreover, wireless channels are sequential by nature which is not the case in on-chip interconnects where parallel buses are the default communication means. After CDMA was adopted by the NoC community, the same wireless CDMA scheme has been maintained where each data bit is encoded in a separate CDMA channel and the encoding/decoding logic is replicated for data packets. In this work, we present a novel CDMA encoding/decoding scheme called Aggregated CDMA (ACDMA) for NoC interconnects in which all packet bits are encoded in a single CDMA channel, consequently, eliminating the area and energy overheads resulted from replicating the channel encoding/decoding logic.

#### I. INTRODUCTION

Modern Systems-on-chips (SoCs) are becoming massively parallel with many harmoniously interconnected Processing Elements (PEs). Interconnecting the PEs is commonly achieved through buses and Networks-on-Chips (NoCs) [1]. In NoCs, exchanged data is bundled into packets and traverse several network layers passing by the physical layer which defines how packets are actually transmitted between NoC units. The physical layer of a NoC is implemented by routers employing crossbar switches. Code Division Multiple Access

(CDMA) is a medium sharing technique that leverages orthogonal codes to enable simultaneous packet routing. Unlike timeshared channels, CDMA leverages the code space to enable channel sharing. CDMA has been proposed as an on-chip interconnect technique for both bus and NoC interconnect architectures [2]. Many advantages of using CDMA for onchip interconnects reduced include power consumption, fixed communication latency, reduced system complexity [3]. Utilizing CDMA in NoC interconnects is

A Peer Revieved Open Access International Journal

www.ijiemr.org

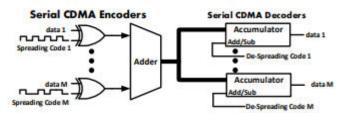

adopted from the wireless communications literature, where the data is spread by orthogonal codes at the transmitters, the spread data are added on the wireless channel, and the received sum is decoded at the receivers. Classical CDMA systems rely on the Walsh orthogonal code family to enable medium sharing. Many research groups have investigated several aspects of CDMA in NoCs, including our group which presented the Overloaded CDMA for onchip Interconnects (OCI) [4] [5] [6]. A 14node CDMA-based network has been developed in [7]. The network utilizes 7 Walsh codes and assignment of the Walsh codes to the network nodes is dynamic based on the request from each node. Two architectures have been introduced in [7]: a serial CDMA network where each data chip in the spreading code is sent in one clock cycle; and a parallel CDMA network where all data chips are sent in the same cycle. The serial and parallel CDMA-based networks have been compared to a conventional CDMA network, a meshbased NoC, and a Time Division Multiple Access (TDMA) bus. For the same network area, the throughput of the parallel CDMA network is higher than that of the mesh-based NoC and the TDMA bus due to the simultaneous medium access nature of CDMA. Standardbasis codes are proposed as a replacement to Walsh CDMA codes in [8]. Standard-basis codes resemble TDMA signaling because each code consists of only a single chip of one and the remaining chips are zeros. The TDMA codes' orthogonality enables them to replace the Walsh codes as spreading and despreading CDMA codes, which reduces

the complexity of the channel adder and decoder as the sum of TDMA codes is limited to zero or one per clock cycle.

### 2. literature survey

### 3.Existing method

Figure 1. Conventional CDMA crossbar.

The conventional CDMA crossbar employed in the literature is depicted in Figure 1. The crossbar interconnects N transmit ports to N receive ports using N-chip length Walsh spreading codes. The binary data from each transmit port is encoded using an XOR encoder; the data bit is XORed with a unique N-chip spreading code assigned to the transmit-receive pair and transmitted in N clock cycles. Data spread from all encoders are added by the CDMA channel adder and sent to all receive port. The decoder at each receive port extracts the data from the channel sum by correlating the channel sum with the assigned spreading code. The correlation operation implemented using an accumulator and a multiplexer since the despreading code chips are unipolar ("0" or "1"). In all of the CDMA interconnect related work, each data bit in a data word is encoded and transmitted in a separate CDMA channel and the encoding/decoding logic is replicated W times for data packets of width W which is a direct application of the wireless CDMA principles in NoC interconnects. However, wireless communication channels sequential by nature due to the interference

A Peer Revieved Open Access International Journal

www.ijiemr.org

problem. Multiple access and MIMO techniques can enable concurrent data transmission on the same wireless channel at the expense of increasing the transmitter/receiver complexity. in on-chip interconnects, on the other hand, a single channel can be efficiently utilized to enable parallel data transmission as noise and interference effects can be efficiently mitigated [9]. In this work, we present a single channel, multi-bit CDMA crossbar namely Aggregated CDMA (ACDMA) NoC crossbar.

# 3. PROPOSED NOC CROSSBAR ARCHITECTURE

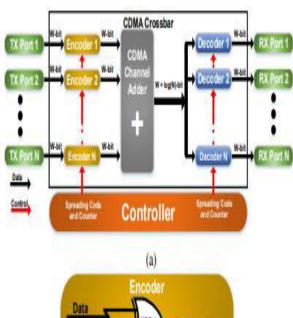

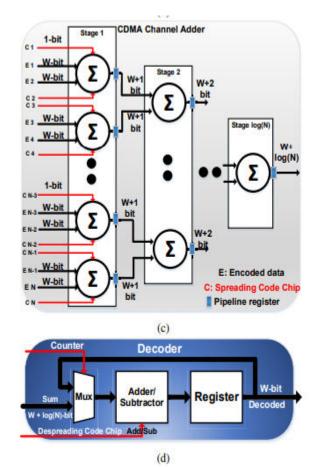

The ACDMA crossbar implements psychical layer of the NoC by interconnecting N transmit (TX) ports to N receive ports where the data width of each port is W where W = log 2 max(di). The high-level architecture of the ACDMA crossbar illustrated in Figure 2(a) is composed of three main parts; encoders, channel adder, and decoders. The encoders spread data from each TX port using W XOR gates as shown in Figure 2(b). Instead of adding the spreading chips of the Walsh orthogonal code to the result in the encoder block as suggested by (2), this operation is postponed to the channel adder block in order to merge the channel adder with the spreading code adders. The output of each encoder is, therefore, limited to W-bit width. The encoder outputs are then added together to form the sum Si of (3). To minimize the critical path of the channel adder, the addition is done using a tree adder architecture as depicted by Figure 2(c) where the leafs of the tree are the encoders

of each TX port, and the root of the tree is the channel sum output. Because there are N leafs, the height of the tree is log2(N). The width of the output wires from each adder in the tree is equal to the width of the input wires plus one to prevent overflows. Since the input to the firs level of adders is (W +1)- bit wide and the height of the adder tree is log2(N), then the width of the output wires at the root adder is W +1+log2(N). Pipeline registers are inserted after each stage in the tree to minimize the critical path of the channel. The sum Si is then sent to all the N decoders, a decoder per RX port.

Data

W-bit

Spreading

Code Chip 1-bit

XOR N

Encoded

W-bit

XOR N

Figure 2. (a) ACDMA crossbar high-level architecture

A Peer Revieved Open Access International Journal

www.ijiemr.org

Figure 2. (c) ACDMA channel adder, (d)ACDMA decoder

implement The decoders the crosscorrelation of (4) in a cost efficient manner; decoder consists of the only adder/subtracter and a register configured as an up/down accumulator as shown in Figure 2(d). Since the despreading code Ck consists of ±1 chips, cross correlation is reduced to simple addition and subtraction operations of consequent sums Si . Therefore, the decoder is implemented as an up/down accumulator: the adder/subtracter adds or subtracts the sum Si from the result saved in the registers according to the value of despreading chip Ci k. In particular, when the despreading chip is '1', the adder adds Si to the contents of the register but subtracts

Si from the contents of the register when the despreading chip is '-1'. At the end of the decoding cycle, the accumulator register holds N dk according to (5), and because N = 2n and n is an integer, data dk is decoded by shifting the accumulator content by log2(N) bits.

The number of two input XOR gates is the same for both circuits. The improvement of the ACDMA crossbar over the conventional CDMA crossbar is evident in the number of channel adder wires; in the conventional CDMA crossbar, the number of the adder wires for the single-bit channel is increased by one in each stage due to the additional carry bit. Therefore, the number of adder wires in stage i is equal to 1+log2(N)-i. For a W-bit word, the number of adder wires is increased to W+W(log2(N)-i), and since there are 2i adders at each stage, then the total number of wires is equal to log2N-1 i=0 2i (W +W(log2N -i)). In the ACDMA crossbar, conversely, the number of adder wires for a W-bit word is W +log2(N)-i, which makes the total number of wires equals to log2N-1 i=0 2i (W + log2N - i)which is a factor of W less than that of the conventional CDMA crossbar. The reduced number of carry bits of the ACDMA crossbar is the prime reason for its superiority. The number of wires for the decoder accumulator and the number of flipflops in the decoder registers is proportional to the number of channel wires—the last stage of the adder. This follows that the complexity of the ACDMA crossbar is in an order of W less than that of the conventional CDMA crossbar.

A Peer Revieved Open Access International Journal

www.ijiemr.org

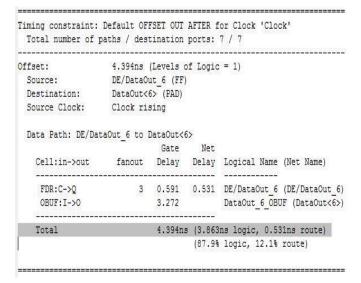

#### **Simulation RESULTS**

| Device Utilization Summary (estimated values) |      |           | E           |

|-----------------------------------------------|------|-----------|-------------|

| Logic Utilization                             | Used | Available | Utilization |

| Number of Slices                              | 20   | 14752     | 0%          |

| Number of Slice Flip Flops                    | 19   | 29504     | 0%          |

| Number of 4 input LUTs                        | 31   | 29504     | 0%          |

| Number of bonded IOBs                         | 16   | 250       | 6%          |

| Number of GCLKs                               | 1    | 24        | 4%          |

Fig 3 Design summary

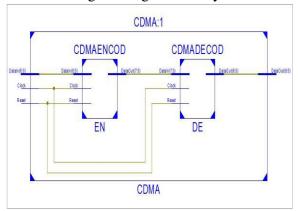

Fig 4. RTL Schematic

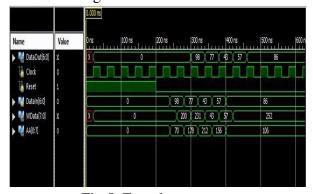

Fig 5. Encoder output

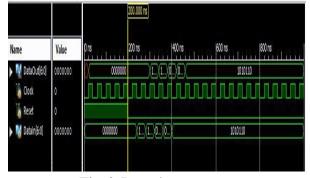

Fig 6. Decoder output

Fig 7. Encoder output

#### V. CONCLUSION

In this work, we presented the ACDMA NoC crossbar to enable parallel transmission of multi-bit data packets on a single CDMA The overhead channel. of channel replication is mitigated which results in up to 60.5% area and 55% power savings with 124% improvement in throughput per area compared to the conventional CDMA crossbar. As a future work, we plan to build and evaluate a full ACDMA-based NoC under different workloads and routing protocols

#### REFERENCES

[1] L. Wang, J. Hao, and F. Wang. Busbased and NoC infrastructure performance emulation and comparison. In Information Technology: New Generations, 2009. ITNG '09. Sixth International Conference on, pages 855–858, April 2009.

[2] R. H. Bell, Chang Yong Kang, L. John, and E. E. Swartzlander. CDMA as a multiprocessor interconnect strategy. In

A Peer Revieved Open Access International Journal

www.ijiemr.org

Signals, Systems and Computers, 2001. Conference Record of the Thirty-Fifth Asilomar Conference on, volume 2, pages 1246–1250 vol.2, Nov 2001.

- [3] B. C. C. Lai, P. Schaumont, and I. Verbauwhede. CT-bus: a heterogeneous CDMA/TDMA bus for future SOC. In Signals, Systems and Computers, 2004. Conference Record of the Thirty-Eighth Asilomar Conference on, volume 2, pages 1868–1872 Vol.2, Nov 2004.

- [4] K. E. Ahmed and M. M. Farag. Overloaded CDMA bus topology for MPSoC interconnect. In 2014 International Conference on ReConFigurable Computing and FPGAs (ReConFig14), pages 1–7, Dec 2014.

- [5] K. E. Ahmed and M. M. Farag. Enhanced overloaded CDMA interconnect (OCI) bus architecture for on-chip communication. In 2015 IEEE 23rd Annual Symposium on High-Performance Interconnects, pages 78–87, Aug 2015.