A Peer Revieved Open Access International Journal

www.ijiemr.org

#### **COPY RIGHT**

2019IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 14<sup>th</sup> Sept 2019. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-08&issue=ISSUE-09

Title DESIGN OF LOW POWER 1-BIT FULL ADDER USING ADVANCED DIFFUSION INPUT TECHNIQUE

Volume 08, Issue 09, Pages: 678-683.

**Paper Authors**

M SRINIVASA RAO, M.B NARENDRA

GVR&S COLLEGE OF ENGINEERING AND TECHNOLOGY

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic

Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

## DESIGN OF LOW POWER 1-BIT FULL ADDER USING ADVANCED DIFFUSION INPUT TECHNIQUE

<sup>1</sup>M SRINIVASA RAO, <sup>2</sup>M.B NARENDRA

<sup>1</sup>STUDENT, DEPT OF ECE, GVR&S COLLEGE OF ENGINEERING AND TECHNOLOGY

<sup>2</sup>ASSOCIATE PROFESSOR, DEPT OF ECE, GVR&S COLLEGE OF ENGINEERING AND TECHNOLOGY

**ABSTRACT:** This paper shows a plan which gives full swing yield to rationale 1 and rationale 0 for 1-piece full adder cell and decreases control utilization, deferral, and region. In this structure full snake comprises of two XOR entryway cells and one cell of 2x1 multiplexer (MUX). The presentation of the proposed structure contrasted and the distinctive rationale style for full adders through Tanner instrument dependent on TSMC 65nm innovation models The recreation results demonstrated that the proposed full adder configuration disperses low control, while improving deferral and territory among all the plan taken for examination.

#### **I.INTRODUCTION**

A adder is one of the significant building obstructs in the development of a twofold Multipler. In ecent times, applications are gone for battery worked gadgets with the goal that power dissemination ends up one of the essential structure imperatives [3]-[10]. In the past processor speed, circuit territory, execution, speed, cost unwavering quality of were prime significance. Power utilization was of auxiliary concern. Be that as it may, lately control utilization is being given equivalent significance. The explanation behind such a changing pattern is credited most likely because of the quick increment in versatile registering gadgets and remote correspondence frameworks which request fast calculations and complex usefulness with low control utilization. Notwithstanding this superior processors expend extreme power which thus builds the expense related with bundling and cooling. In this way there is an ascent in the power thickness of VLSI chips consequently

aggravating the unwavering quality. It has been discovered that each 10o ascent in working temperature generally duplicates the disappointment pace of segments made up of Silicon because of a few Silicon disappointment systems, for example, warm rampant, intersection dissemination, electro movement dispersion, electrical parameter move, bundle related disappointment and Silicon interconnect disappointment [11]. From nature perspective, the lesser the power scattering of electronic segments, lesser will be the warmth dispersed in rooms which thusly will positively affect the worldwide condition. Additionally, lesser power will be devoured. In this manner, for further streamlining of execution of a full subtractor as far as power utilization, defer time just as Power Postpone Product (PDP), a new low control, fast vitality proficient full subtractor is being proposed utilizing Gate Diffusion Input (GDI) strategy. GDI is a novel business as usual for low control advanced circuits. This strategy permits

A Peer Revieved Open Access International Journal

www.ijiemr.org

decrease in power utilization, spread deferral and transistor check of advanced circuit. The technique can be utilized to limit the quantity of transistors contrasted with regular Complementary Pass-transistor Logic (CPL) and Dual Pass transistor Logic (DPL) CMOS plan. The proposed subtractor has a transistor check of 14 a decrease of 72.00%, 63.16% and 58.82% contrasted with a full subtractor made out of CMOS rationale, transmission entryways and CPL, proposing a decrease in zone. So as to set up the innovation freedom of the plan the proposed subtractor has been reproduced utilizing 150nm innovation.

#### II. GATE DIFFUSION INPUT (GDI)

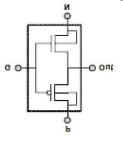

Entryway Diffusion Input (GDI) strategy depends on the use of a straightforward cell as appeared in Fig. 1 which can be utilized for low control computerized circuits [3]. This method is actualized in twin-well CMOS or Silicon on Insulator (SOI) advancements. In this procedure, the heft of both NMOS and PMOS transistors are designed to their dispersions to diminish the mass impact that is reliance of edge voltage on source-to-mass voltage [12]. The reliance of transistor limit voltage on source-to-mass voltage is as per the following:

$$V_{th} = V_{th0} + \gamma \left( \sqrt{2\phi_F + V_{SB}} - \sqrt{2\phi_F} \right) - \eta V_{DS}$$

Where VSB is source-body voltage, Vth0 is limit voltage at VSB=0,  $\gamma$  is linearized body coefficient,  $\Phi F$  is the Fermi potential and  $\eta$  is Drain nduced Barrier Lowering (DIBL) coefficient. Utilizing this technique control utilization can be decreased alongside defer time subsequently conveying a diminished power postpone item. Therefore territory of the circuit is limited.

Figure 1: Basic GDI Cell

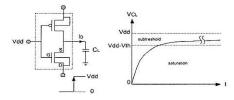

It should be noted that though the circuit takes after with standard CMOS inverter, are significant there sure contrasts contrasted with traditional one. The GDI cell contains 3 sources of info-P which is the contribution to the external dispersion hub of the PMOS transistor isn't associated with Vdd while N which is the contribution to the external dissemination hub of the NMOS transistor isn't associated with GND, and G which is the basic entryway contribution of both the NMOS and PMOS transistors. The Out hub which is the regular dispersion of both the transistors might be used as info or yield port contingent upon the circuit arrangement. The ports P and N conveys 2 additional pins which yield the GDI plan more consistent than the standard CMOS structure [3]. Fig. 2 demonstrates the transient reaction of a GDI cell which is very like that of a standard CMOS inverter [13], [14]. This examination depends on the Shockley model in which the channel flow ID is spoken to as demonstrated as follows

$$I_D = \begin{cases} I_{D0} \left( \frac{W}{L} \right) \ell^{(qV_{GS}/KT)} \\ \left( V_{GS} \leq V_{\mathrm{TH}} : \mathrm{subthreshold\ region} \right) \\ K \left\{ \left( V_{GS} - V_{\mathrm{TH}} \right) V_{DS} - 0.5 V_{DS}^2 \right\} \\ \left( V_{DS} < V_{GS} - V_{\mathrm{TH}} : \mathrm{linear\ region} \right) \\ 0.5 K \left( V_{GS} - V_{\mathrm{TH}} \right)^2 \\ \left( V_{DS} \geq V_{GS} - V_{\mathrm{TH}} : \mathrm{saturation\ region} \right) \end{cases}$$

Where K denotes device trans conductance parameter, VTH denotes threshold voltage,

A Peer Revieved Open Access International Journal

www.ijiemr.org

W denotes channel width and  $\overline{L}$  denotes channel length.

Figure 2: Transient response of a GDI cell

However, it is to be mentioned that in GDI cell Vds has to be considered as a variable of input voltage in Shockley model [3] in contrast with CMOS inverter analysis [15] where Vgs was considered as an input voltage.

#### III.LOGIC GATES BASED ON GDI METHOD

Table I shows the various operations that can be performed with a basic GDI cell.

TABLE I. DIFFERENT OPERATIONS OF BASIC GDI CELL

| N           | P   | G | Out   | Operation |

|-------------|-----|---|-------|-----------|

| <b>'</b> 0' | В   | A | ĀB    | F1        |

| В           | '1' | A | Ā+B   | F2        |

| <b>'1'</b>  | В   | A | A+B   | OR        |

| В           | '0' | A | AB    | AND       |

| С           | В   | A | ĀB+AC | MUX       |

| <b>'</b> 0' | '1' | A | Ā     | NOT       |

From table I, it tends to be seen that utilizing just 2 transistors different capacities can be performed. For example, OR door can be planned utilizing a solitary GDI cell while if there should be an occurrence of structuring of an OR entryway door can be planned utilizing just 2 transistors and even a Multiplexer MUX) can be conceived utilizing a solitary GDI cell. In this way, a straightforward change to the info design of

the GDI cell would yield bunch assortment of Boolean capacities. Various information doors can be executed by joining a few GDI cells.

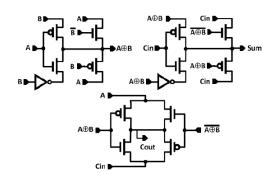

#### IV PROPOSED SYSTEM

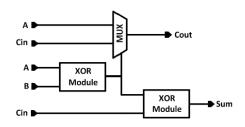

Full adder is a combinational circuit that plays out the math activity of 3 number of bits. Expansion considered a basic activity in math and rationale unit computerized sign preparing and. The 1-piece full adder contains three information bits and two yield bits, the initial two bits of the data sources are An and B called operands and the third information bit Cin is a piece conveyed in from the past less-huge stage, yield bits called entirety is the consequence of expansion activity and do which will be the info convey to the following expansion activity, and the articulation:

$$SUM = A \oplus B \oplus Cin$$

$$COUT = A \overline{(A \oplus B)} + Cin (A \oplus B)$$

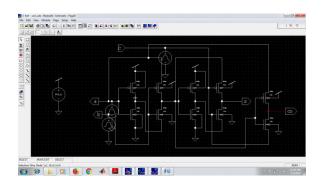

The proposed design consists of 16 transistors including two XOR gate cells to produce sum and one multiplexer cell to produce carry out, as shown in figure (1), the block diagram shown in figure (2), and the truth table of proposed full adder presented in table I

| A | В | Cin | SUM | Cout |  |

|---|---|-----|-----|------|--|

| 0 | 0 | 0   | 0   | 0    |  |

| 0 | 0 | 1   | 1   | 0    |  |

| 0 | 1 | 0   | 1   | 0    |  |

| 0 | 1 | 1   | 0   | 1    |  |

| 1 | 0 | 0   | 1   | 0    |  |

| 1 | 0 | 1   | 0   | 1    |  |

| 1 | 1 | 0   | 0   | 1    |  |

| 1 | 1 | 1   | 1   | 1    |  |

Table I. Truth Table Of Proposed Full Adder

A Peer Revieved Open Access International Journal

www.ijiemr.org

Fig.3. Proposed design for 1-Bit Full Adder

Fig. 4. Block Diagram For Proposed Full Adder

The significant advantage of utilizing GDI system is that countless capacities can be executed utilizing this procedure. We can see from the table 2 that GDI can be utilized for executing different plans, for example, MUX, AND, OR and so on. The most unpredictable structure among these is the planning of MUX, which should be possible utilizing 2 transistors. Though utilizing other customary procedures it requires 8-10 transistors for structuring a MUX. The fundamental disadvantage of GDI method is that of swing debasement. This is because of edge misfortune and to kill this we need to utilize silicon on cover or twin-well procedure to acknowledge, which is over the top expensive. Planning a full snake the real building square is XOR door utilizing GDI strategy.

#### **V IMPLEMENTATION**

Fig 5 Circuit Design

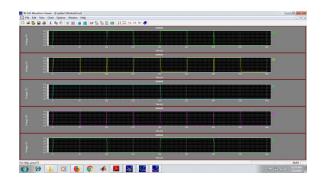

Fig 5 Simulation Result

#### VI CONCLUSION

The objective of this paper was to structure a full snake with rapid execution utilizing GDI method. From the presentation investigation table obviously the proposed framework is the best among the talked about structures as far as region, postponement and power dissemination. Since the outcomes were gotten as a result of reproduction, the readings are exact. This plan will have an improved speed and furthermore the effectiveness of framework is more contrasted with all the ordinary procedures. Further alterations can be made in the structure by including a couple of more transistors.

A Peer Revieved Open Access International Journal

www.ijiemr.org

#### **REFERENCES**

- [1] Tripti Sharma, K.G.Sharma and B.P.Singh,"High Performance Full Adder Cell: A Comparative Analysis",2010 IEEE Students' Technology Symposium 3-4 April 2010,IIT Kharagpur, 2010.

- [2] Rajkumar Sarma1 and Veerati Raju," Design and Performance Analysis of Hybrid Adders For High Speed Arithmetic Circuit", International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.3, June 2012.

- [3] A. Morgenshtein, A. Fish, and I. Wagner, "Gate-diffusion input (GDI): a power-efficient method for digital combinatorial circuits," IEEE Transactions on Very Large Scale Integration (VLSI) Systems IEEE Trans. VLSI Syst., vol. 10, no. 5, pp. 566–581, 2002.

- [4] A. Morgenshtein, I. Shwartz, and A. Fish, "Gate Diffusion Input (GDI) logic in standard CMOS Nanoscale process," 2010 IEEE 26th Convention of Electrical and Electronics Engineers in Israel, 2010.

- [5] A. Morgenshtein, V. Yuzhaninov, A. Kovshilovsky, and A. Fish, "Fullswing gate diffusion input logic—Case-study of low-power CLA adder design," Integration, the VLSI Journal, vol. 47, no. 1, pp. 62–70, Jan. 2014.

- [6] Korraravikumar, AL Reddy, M.Sadanandam, Santhoshkumar.A M.Raju," Design of 2T XOR Gate Based Adder Using GDI Technique", Full Conference on Innovative International for Industry Mechanisms **Applications** (ICIMIA 2017),2017.

- [7] Jaume Segura, Charles F. Hawkins CMOS electronics: how it works, how it fails, Wiley-IEEE, 2004, page 132

- [8] Clive Maxfield Bebop to the Boolean boogie: an unconventional guide to electronics Newnes, 2008, pp. 423-426

- [9] Albert Raj/Latha VLSI Design PHI Learning Pvt. Ltd. pp. 150-153

- [10] Yano, K, et al, "A 3.8 ns CMOS 16\*16b multiplier using complementary pass transistor logic", IEEE J. Solid State Circuits, Vol 25, p388-395, April 1990

- [11] Yingtao Jiang, Abdulkarim Al-Sheraidah, Yuke Wang, Edwin Sha, and Jin-Gyun Chung, "A Novel Multiplexer-Based Low-Power Full Adder" IEEE Transaction on circuits and systems-II: Express Brief, Vol. 51, No. 7,p-345, July- 2004

- [12] Makoto Suzuki, et al, "A 1.5 ns 32 b CMOS ALU in double pass transistor logic", ISSCC Dig. Tech. Papers, pp 90-91, February 1993.

- [13] N. Ohkubo, et al, "A 4.4 ns CMOS 54X54 b multiplier using pass transistor multiplexer", Proceedings of the IEEE 1994 Custom Integrated Circuit Conference, May 1-4 1994, p599-602, San Diego, California.

- [14] Mohamed W. Allam, "New Methodologies for Low-Power High-Performance Digital VLSI Design", PhD. Thesis, University of Waterloo, Ontario, Canada, 2000

- [15] A.Bazzazi and B. Eskafi, "Design and Implementation of Full Adder Cell with the GDI Technique Based on 0.18µm CMOS Technology", International MultiConference of Engineers and Computer Scientists (IMES) Vol II, March 17 19, 2010, Hong Kong

A Peer Revieved Open Access International Journal

www.ijiemr.org

#### **STUDENT DETAILES:**

M SRINIVASA RAO-172W1D6806 MAIL ID:srinummtl9@gmail.com

BRANCH: VLSI & ES

**GUIDE DETAILS:**

NAME: M.B NARENDRA MAIL ID: mbn399@gmail.com

Designation: ASSOCIATE

PROFESSOR(ECE)

GVR&S COLLEGE OF ENGINEERING

AND TECHNOLOGY

BUDAMPADU, GUNTUR.