A Peer Revieved Open Access International Journal

www.ijiemr.org

### **COPY RIGHT**

2019IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 14<sup>th</sup> Sept 2019. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-08&issue=ISSUE-09

Title LOW POWER TECHNIQUE FOR VECTOR PROCESSING AND ADVANCE CLOCK GATING FPGA

Volume 08, Issue 09, Pages: 670-677.

**Paper Authors**

RACHABATHUNI JYOTHI, K.VIJAY KUMAR

GVR&S COLLEGE OF ENGINEERING AND TECHNOLOGY

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic

Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

# LOW POWER TECHNIQUE FOR VECTOR PROCESSING AND ADVANCE CLOCK GATING FPGA

<sup>1</sup>RACHABATHUNI JYOTHI, <sup>2</sup>K.VIJAY KUMAR

<sup>1</sup>STUDENT, DEPT OF ECE, GVR&S COLLEGE OF ENGINEERING AND TECHNOLOGY <sup>2</sup>ASSOCIATE PROFESSOR, DEPT OF ECE, GVR&S COLLEGE OF ENGINEERING AND TECHNOLOGY

### **ABSTRACT**

The paper presents fine-grain clockgating plans for melded increase include type drifting point units (FPU). The clockgating depends on guidance type, exactness and operand esteems. The exhibited plans center around diminishing the power at pinnacle execution, where each FPU stage is utilized in almost every cycle and customary plans have little sway on the power utilization. Contingent upon the guidance blend, the plans permit to mood killer 18% to 74% of the register bits. Notwithstanding for the most pessimistic scenario guidance 18% to 37% of the FPU are closed down contingent upon the information designs.

### 1. INTRODUCTION

In the new coasting point standard IEEE 754-2008 melded increase include (FMA) A • C+B is presented as required activity. The item is registered at full exactness; adjusting possibly gets connected when including item and numbers to be added. The first FMAtype coasting point unit (FPU) was presented in 1990 and from that point forward numerous plans have been depicted in the writing [6]. The principle focal point of every one of those structure was to make the FPUs quicker, however almost no has been said about how to make such a FPU control effective. In the most recent decade, the power utilization and the exertion for cooling the processors and PC frameworks have turned into a noteworthy issue. In the market game installed and showcase, fashioners are battling for each milli-Watt, and in the server business a major spotlight is put on green IT [7].

Indeed, even supercomputers are not simply positioned by their FPU execution; the best 500 records presently additionally considers the power efficiency [5]. The most widely recognized path for sparing force is to close down bits of the equipment when they are not utilized. A powerful approach for a pipelined configuration is to clockgate register arranges that are inactive. This paper portrays how this component can be connected to a FMA-type FPU, and that it is conceivable to close down pieces of the FPU notwithstanding when the framework is running at pinnacle FPU execution. After a diagram of the structure of a FMA-type FPU (Section 1.1) and presenting the idea of clockgating (Section 2), we show how the standard clockgating plans can be connected to such a FPU and which angles should be considered. We at that point bring new clockgating plans into FMA-type FPUs, as

A Peer Revieved Open Access International Journal

www.ijiemr.org

utilized in ongoing items. Those plans are guidance based, exactness based, and information based clockgating; Sections 2, 3 and 4 depict them in detail. For every one of the plans it is indicated what level of the FPU can be closed down.

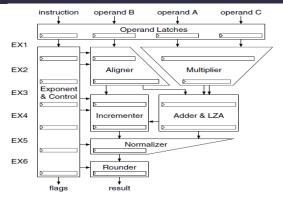

### 1.1. FMA Type Floating-point Unit

Figure 1 delineates the essential structure of a condition of-theart, 6-cycle FMA-type FPU. The aligner, multiplier, normalizer and rounder chiefly work on the mantissa of the operands. The type and sign data is handled in the type dataflow, which likewise holds the FPU control. The operand registers hold the operands; additionally incorporate rationale for prepreparing the operands, for example, unloading the operands into sign, type and mantissa. The multiplier registers halfway items for A • C and packs them into two item vectors. In parallel, the aligner adjusts the mantissa of the numbers to be added to that of the genius channel; this requires wide moves. The snake at that point figures the whole or supreme distinction of the two item vectors and of the adjusted numbers to be added. It likewise decides the quantity of driving zeros in the snake result utilizing driving zero anticipator rationale (LZA). The normalizer at that point moves out the main zeros and the rounder adjusts the middle of the road result to the required accuracy.

As described it suffices to use an aligned addend

Figure 1. Basic floating-point pipeline

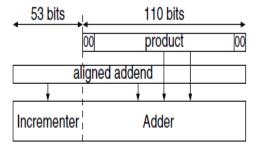

what's more, middle of the road results which are multiple times as wide as the accuracy of the operands in addition to a couple of additional bits. For twofold exactness operands, the item cushioned with two bits at either side for adjusting is 110 bits wide, and the adjusted numbers to be added to its 163 bits stands out 53 bits to one side of the item (Figure 2). So as to spare equipment, a viper is utilized for the trailing 110 bits and an incrementer for the main 53 Both incorporate recomplement bits. rationale for subtraction. he driving zeroanticipator is required for the trailing 110 bits. The situation of a main one in the incrementer part can be gotten from the aligner move sum.

Figure 2. Adder split for a doubleprecision dataflow

Aside from FMA-type activities which incorporate A • C+B and derivates like A •

A Peer Revieved Open Access International Journal

www.ijiemr.org

C-B and - A • C+B, FMA-type FPUs bolster different other gliding point guidance types, for example, include, increase, changes over among number and skimming point designs, look at tasks, least and most extreme capacity, and moves with potential sign control. It additionally offers help for separation and square root. In certain usage, the FPU is likewise utilized for whole number duplicate and increase include activities. So as to keep the FPU structure straightforward and little, every one of these guidelines are mapped onto the FMA dataflow and are executed as FMA with certain revisions. Increase A · C, for instance, can be executed as A • C+0, and a subtract A-B can be executed as A • 1-B. For the proselytes, the item example is compelled to a unique worth and an adjustment is connected to the leastnoteworthy info bits of the viper. Gauge guidelines need uncommon equipment, for example, tables and reuse just little pieces of the FMA pipeline. Separation and square root activities can be executed as a progression of appraisals and FMA tasks.

Different gliding point precisions are bolstered utilizing an inward information design which is in any event as wide as the biggest upheld accuracy. Info information are unloaded into the interior arrangement; the outcome is adjusted and pressed into the ideal outcome group. The pressing and unloading is autonomous of the executed guidance type. Consequently, changes over between various gliding point precisions can be treated as normalizing moves.

### 2. CLOCKGATING CONCEPT

To decrease the exchanging intensity of the FPU, the quantity of transitions should be

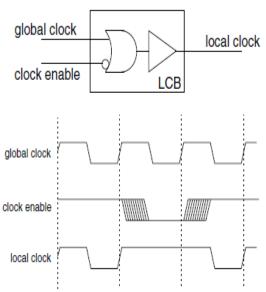

diminished. A broad depiction of methods to stay away from superfluous changes, focusing on glitch decrease, is given. For an exceptionally pipelined configuration like the FPU introduced in this paper, the registers between the rationale stages avoid glitches to engender into the following cycle and breaking point absolute glitch control. This paper utilizes clockgating so as to lessen the quantity of changes and glitches. Rather than the methodology depicted where each flipflop can be clockgated independently, the FPU portrayed in this paper uses enrolls that comprises of various flipflops and a nearby clock cradle (LCB). The LCB has a nearby clock yield, common by all associated flipflops. Incapacitating a register should be possible by gating the check signal in the LCB, as portrayed. An applied perspective on the LCB, together with a practical planning chart, is given in Figure 3. It is accepted here that the registers are activated by the rising clock edge.

At the point when the clock empower sign is 1, the worldwide clock is spread into the nearby clock net; when the empower sign is 0, the neighborhood clock quits exchanging. It is significant that the clock empower sign is steady when the worldwide clock sign is low, to maintain a strategic distance from glitches in the neighborhood clock net. Clockgating lessens the power in three different ways. Initially, decreasing the clock movement will spare power since the exchanging of the worldwide clock net does not proliferate into the neighborhood clock nets. Second, the neighborhood clock is peaceful and the register substance does not change; that spares the exchanging intensity of the register bits. Third, since the

A Peer Revieved Open Access International Journal

www.ijiemr.org

substance of the register is unaltered, there is no exchanging at the yields of the register. Thus, the exchanging factor in the resulting pipelinestage will be zero.

Figure 3. LCB with clockgating support (conceptual)

For each circuit of a plan, control recreation apparatuses can quantify the exchanging power as a component of information exchanging factor on its information inputs (SF) and clock movement. Table 1 records the exchanging power information for the 2-cycle aligner circuit of the exhibited FPU structure; the evaluated spillage control for the aligner contributes an extra 12 mW.

|      | Clock Activity |       |       |       |       |  |  |  |  |

|------|----------------|-------|-------|-------|-------|--|--|--|--|

| SF   | 0%             | 25%   | 50%   | 75%   | 100%  |  |  |  |  |

| 0 %  | 0.24           | 2.14  | 4.03  | 5.92  | 7.81  |  |  |  |  |

| 10 % | 1.67           | 7.54  | 13.41 | 19.28 | 25.15 |  |  |  |  |

| 20 % | 3.10           | 12.95 | 22.80 | 32.65 | 42.50 |  |  |  |  |

| 30 % | 4.53           | 18.35 | 32.18 | 46.01 | 59.84 |  |  |  |  |

| 40 % | 5.95           | 23.76 | 41.57 | 59.38 | 77.19 |  |  |  |  |

| 50 % | 7.38           | 29.17 | 50.95 | 72.74 | 94.53 |  |  |  |  |

# Table 1. Switching power (mW) as function of clock activity and switching factor for an FPU component

For this aligner circuit, there is an exchanging power decrease by in excess of a factor of 300 among most exceedingly terrible and best case. Inside each line and segment a request for extent can be picked up. Regardless of whether there is no exchanging at the data sources (SF=0), clockgating can decrease the exchanging power by about a factor 30. With high clock action, the diminished exchanging element still adds to a considerable power sparing.

Accepting pinnacle execution, i.e., each phase of the FPU is utilized in each cycle and an idealistic exchanging variable of 30%, the exchanging force is multiple times bigger than the spillage control. This shows including extra rationale can be a net power decrease in the event that it empowers to fundamentally expand the clockgating.

The aggregate of all registers constrained by the equivalent clockgating capacity is called clock space. Each LCB just acknowledges a solitary clockgate signal. As it were, all register bits associated with the equivalent LCB are in a similar clock space.

Subsequently, expanding the quantity of clock spaces prompts an expanding number of LCBs. Since LCBs utilize a lot of intensity, the power improvement by parting a clock space needs to surpass the punishment presented by the extra LCB. For the cutting edge CMOS SOI innovation that is utilized here, a clock area ought to contain at any rate 8 to 10 register bits.

Timing puts another requirement to clockgating. As appeared in Figure 3, the clock empower signals for the LCB must be

A Peer Revieved Open Access International Journal

www.ijiemr.org

steady before the clock sign drops, to stay away from glitches on the nearby clock net. The circuits processing the clockgating signals in this way must be kept basic or use signals which are precomputed in the past cycle.

The power utilization depends on the executed clockgating plan, yet in addition on the information exchanging, chip innovation and register type. For effortlessness, in this paper we utilize the quantity of timed register bits as a measure for exchanging power.

# 3. PRECISION BASED CLOCKGATING

The displayed FPU pipeline supports twofold exactness (DP) and single-accuracy (SP) gliding point activities. Inside, all data sources are reached out to a configuration with sign, 13-piece example, whole number piece and 52-piece portion. On the off chance that the consequence of a guidance is a SP number the least noteworthy bits of the viper and normalizer result are utilized for the clingy bit calculation. The clingy bit of the lower snake half is figured by the LZA. The clingy bit of the lower normalizer bits is pre-figured during the standardization for timing reasons. Consequently, in the event of a SP result, the lower half of the snake and normalizer result must not be figured. The hooks just used to process the lower result halfs can be clockgated. Note this does exclude the locks required for the convey system of the viper. When changing over SP contributions to the interior configuration, the least huge bits of the operands are set to zeros. Thus, the 9:2 decrease tree of the multiplier that uses the least huge bits of the C operand registers 0

• A = 0. Rather than figuring this with the decrease tree, the yield of this tree is compelled to zero and the transitional registers are killed. Since the lower half of the multiplier result is zero for SP inputs, it is conceivable to process the clingy bit of the lower half of the snake result as of now in the aligner. This would permit to clockgate the lower some portion of the aligner yield to the viper just as the lower some portion of the LZA (which record for around 3.4% of the locks). advancement would require alterations to the aligner clingy rationale and the snake convey tree and was not actualized in the plan.

Table 4 records the clock spaces that should be actuated for gliding point duplicate include directions with various accuracy. The clock spaces MR, AD and NR are isolated into subdomains HI and LO, where the area HI contains the registers that are required by any exactness and LO contains the registers that are required for twofold accuracy activities. The table shows that precison based clockgating lessens the quantity of timed register bits for SP directions by up to 11.9%. The accuracy based clockgating in the multiplier can

|          | MR   |     | AD   |     | NR  |     | Saving |

|----------|------|-----|------|-----|-----|-----|--------|

|          | HI   | LO  | HI   | LO  | HI  | LO  | (%)    |

| DP       | Χ    | Χ   | X    | Χ   | Χ   | Χ   | 0.0    |

| SP       | Χ    |     | Χ    |     | Χ   |     | -11.9  |

| Size (%) | 17.4 | 7.9 | 17.2 | 3.0 | 1.6 | 1.0 |        |

Table 2. Precision based clockgating for fma

A Peer Revieved Open Access International Journal

www.ijiemr.org

likewise be utilized for fixed-point duplicate include directions. Expecting that the fixed-point sources of info are all things considered 32 bits wide, the increase of two information sources should be possible without utilizing the third 9:2 decrease tree. This diminishes the clock movement of fixed-point increase include guidelines by 7.9%.

### 4. DATA BASED CLOCKGATING

In a twofold exactness, FMA-type FPU, the mantissa of the middle of the road information is up to 163 bits wide. For floatingpoint directions like increase include, duplicate, and include, it relies upon the operand esteems whether the full 163-piece wide middle information are required or whether the activity can do with bits of the information vectors. This area subtleties how to identify these information ward cases right off the bat in the pipeline and how this can be utilized to lessen the quantity of timed registers.

### 4.1. Special Inputs

In the event that one of the contributions of a number juggling activity is a NaN or endlessness, the aftereffect of the activity is figured utilizing rationale in the incrementer and the NaN sending rationale in the NN space. The normalizer is compelled to choose the yield of the incrementer. On the off chance that none of the operands is a NaN or endlessness, the NN space, representing 3.6% of the register bits, can be clockgated. The rationale in the NN area isn't required if at any rate one operand is endlessness however no operand is a NaN. Be that as it may, separating boundless qualities from NaNs requires a zero check onthe part, though identifying NaN or interminability just requires an each of the one check of the example. Killing the NN area for vastness just operands would in this way increment the planning weight on the initiate signal for the NN space. Since this case is thought to be uncommon, it isn't viewed as advantageous; NaN and endlessness cases are dealt with the same. For these cases, snake and driving zero-anticipator can be gated; that are the spaces AD and LZ which record for about 24% of the register bits.

An increase include guidance where either the An or C operand is zero is dealt with like a move and the comparing guidance based clockgating is connected. Something else, if the B operand is zero, the guidance is treated as a duplicate. Comparable improvements apply for the duplicate and include guidance types. Recognition of zero operands requires almost the entire first cycle, except if this data is as of now put away in the register document. The exhibited FPU has no extraordinary data in the register record. In this manner, the zero operand data is past the point of no return for controlling the gating of the primary cycle aligner and multiplier spaces AL and MR. In the event of zero item, viper and LZA are killed (24% register bits), while for zero numbers to be added the incrementer space is gated (5% register bits).

### 4.2. Operand Alignment

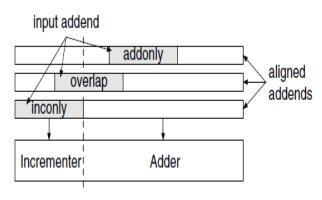

In the event that all information sources are limited, non-zero numbers, the aligner shifts the numbers to be added division dependent on the example distinction of numbers to be added and item. The adjusted numbers to be added, which is the aftereffect of this arrangement move, is apportioned into an

A Peer Revieved Open Access International Journal

www.ijiemr.org

incrementer part which is sent to the incrementer and a snake part which is sent to the viper (Figure 2). The width of the adjusted numbers to be added is restricted to 163 bits by unique treatment of the huge move sums. On the off chance that the numbers to be added is moved out on the right, all bits moved out are gathered in an aligner clingy bit. On the off chance that the numbers to be added is moved out on the left, the move sum is disregarded and the numbers to be added is constrained into the incrementer part of the adjusted numbers to be added [14]. In light of the situation of the info numbers to be added inside the adjusted numbers to be added, we recognize three cases: inconly, addonly, and cover (Figure 4). The situation where the entire numbers to be added is set in the incrementer some portion of the adjusted numbers to be added is called inconly. Addonly means the situation where the info numbers to be added is completely contained in the viper part and the aligner clingy bit. The rest of the case is called cover. The case data is accessible in the subsequent cycle, without a moment to spare for controlling the clockgating of the incrementer and snake inputs.

Figure 7. Alignment Cases

In the addonly case, the incrementer part of the adjusted numbers to be added comprises of each of the zeros. Subsequently, the incrementer some portion of the numbers to be added does not add to the whole or outright contrast of item and adjusted numbers to be added. The normalizer just needs to consider the snake yield and standardize it dependent on the data given by the main zero-anticipator. For this case, the incrementer area IN can be killed.

#### **CONCLUSION**

clockgating methodologies Conventional lessen FPU control utilization if no directions are executed, or, best case scenario, decrease the power utilization for the inert cycles between ensuing guidelines. In numerical applications with profoundly advanced drifting point schedules these customary clockgating plans productive for the FPU. We have grown new clockgating plans that address precisely this situation, i.e., they spare power regardless of whether the FPU executes a guidance each cycle. The plans clockgate parts of the FPU dependent on guidance type, exactness, and operand esteems.

### REFERENCES

[1] C. M. Abernathy, G. Gervais, and R. Hilgendorf. Method and apparatus for dynamic power management in an execution unit using pipeline wave flow control. United States Patent 7,137,013, November 2006.

[2] S. H. Dhong, S. M. Mueller, and H.-J. Oh. Power saving in FPU with gated power based on opcodes and data. United States Patent 7,137,021, November 2006.

[3] S. H. Dhong, S. M. Mueller, H.-J. Oh, and K. D. Tran. Power saving in a floating

A Peer Revieved Open Access International Journal

www.ijiemr.org

point unit using a multiplier and aligner bypass. United States Patent 7,058,830, June 2006.

[4] M. A. Filippo. Clock control of functional units in an integrated circuit based on monitoring unit signals to predict inactivity. United States Patent 6,983,389, January 2006.

[5] Green500.org. The green500 list, June 2008. http://www.green500.org/lists.php.

[6] T. N. Hicks, R. E. Fry, and P. E. Harvey. Power2 floatingpoint unit: architecture and implementation. IBM Journal of Research and Development, 38(5):525–536, 1994.

[7] IBM. Green IT, 2008.

### **STUDENT DETAILES:**

RACHABATHUNI JYOTHI

172W1D6807

MAIL ID: jyothirachabathuni@gmail.com

BRANCH: VLSI & ES

### **GUIDE DETAILS:**

NAME: K.VIJAY KUMAR MAIL ID: roi.raj24@gmail.com

Designation: ASSOCIATE PROFESSOR

(ECE)

GVR&S COLLEGE OF ENGINEERING

AND TECHNOLOGY BUDAMPADU, GUNTUR.