A Peer Revieved Open Access International Journal

www.ijiemr.org

#### **COPY RIGHT**

2019IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 4<sup>th</sup> Sept 2019. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-08&issue=ISSUE-09

Title A 3-Ø BALANCED DC-LINK MULTILEVEL INVERTER BY ABRIDGED AMOUNT OF DC SOURCES

Volume 08, Issue 09, Pages: 459-471.

**Paper Authors**

#### N SANDEEP, P NAVEEN, P KALYAN

Anu Bose Institute of Technology K.S.P Road, New paloncha, Bhadradri Kothagudem, Telangana, India

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic

Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

# A 3-Ø BALANCED DC-LINK MULTILEVEL INVERTER BY ABRIDGED AMOUNT OF DC SOURCES

N SANDEEP<sup>1</sup>,P NAVEEN<sup>2</sup>,P KALYAN<sup>3</sup>

<sup>1,2,3</sup>UG Students, Dept. of Electrical and Electronics Engineering Anu Bose Institute of Technology KSPRoad, Newpaloncha, Bhadradri Kothagudem, Telangana, India. chanti7235@gmail.com<sup>1</sup>, naveenpittala021@gmail.com<sup>2</sup>, kalyanpilli00@gmail.com<sup>3</sup>

Abstract: - This paper displays a novel three-sort out DC-interface shocked inverter topology with diminished number of information DC power supplies. The proposed inverter incorporates strategy related half-partner modules to make the astonished waveform and a fundamental H-interface module, going about as a farthest point generator. The inverter yield voltage is moved to the store through a three-sort out transformer, which supports a galvanic withdrawal between the inverter and the heap. The proposed topology highlights different central focuses when separated and the standard flabbergasted inverters proposed in the academic works. These highlights combine adaptability, major control, decreased number of DC voltage sources and less contraptions check. A central sinusoidal heartbeat width balance philosophy is utilized to control the proposed inverter. The presentation of the inverter is overviewed under various stacking conditions and an appraisal with some present topologies is besides appeared. The presence of mind and adequacy of the proposed inverter are stated through reenactment and fundamental examinations utilizing a downsized low-voltage ask about office model.

**Indexd Terms:-**Hybridmultilevel inverter; DC-linkinverter; half-bridgemodule; symmetricDC voltage supply.

#### **I.INTRODUCTION**

Amazed inverters have gotten extraordinary thought from both insightful world and industry in the past couple of decades due to their specific features appeared differently in relation to their customary two-level accomplices [1, 2]. These fuse, lower trading mishaps and weight on semiconductor contraptions, splendid yield waveforms. lessened electromagnetic impedance and more diminutive filtering necessities [3-6]. Fell Multilevel Inverters (CMLI) have gotten unprecedented tendency in various mechanical applications, especially, reasonable power source coordination [5, 7, 8]. This is especiallydue to their deliberate quality and reiteration incorporates close nonattendance of confoundedcapacitor

voltage modifying issue, which is a normal issue with various topologies, for instance, diodeandcapacitor caught inverters [9-11]. A couple of assortments of CMLI circuit topology havebeen accounted for in the open composition, wanting to fabricate the accomplished voltagelevels, which in the long run improvethe idea of the yield waveform [12]. Cross breed or hilter kilter fell stunned inverter is oneofthe proposed assortments, where distinctive information voltage levelsare ordinarily considered [13-16]. Diminished device check canbe cultivated with cream CMLIs, in any case nonappearance of estimated quality and conflicting voltage dispersal on the power switchesmakes them revolting for utilitygrade applications. Of course, another

A Peer Revieved Open Access International Journal

www.ijiemr.org

genuine test with CMLIs is the prerequisite for nothing restricted DC power supplies, which power additional constraints and multifaceted nature, especially required A undertakings represented in the open composition intended to reduce the required number of the DC power supplies [11, 17-19]. For instance, [19-21] proposed another CMLI including scaffold cells arrange the unipolar staircase-shape waveform and a fullinterface inverter as a furthest point generator. This has broadly diminished the contraptions count and the required number of DC power supplies differentiated and customary amazed inverters. Some changing capacitors are utilized inside the half-interface modules to reduce the amount of rectifiers in [19]. Anyway, as referenced in [11], changing these capacitors requires a jumbled control contrive. A growth of the topology proposed in [20, 21] was starting late point by point in [11], where a further diminishing in the required DC power supplies was practiced, in any case a possible development to three-arrange system was not uncovered. A segregated three-organize half-associate based CMLI is proposed in [22-24]. Regardless, these topologies require a higher number of isolated DC-supplies, which extends the cost and multifaceted nature similarly as the essential for snared equalization a methodology. Blend three-arrange CMLI is represented in [17, 18], where the fell halfinterface cells are related with a threeorganize voltage source inverter. This has basically diminished the amount of the semiconductor devices similarly as required DC supplies. Nevertheless, the prerequisite for restricted DC power supplies couldn't be kept up a vital good ways from. Another assortment of the topologies considered in [11] was proposed

in [25, 26], where only a singular DC power supply is used and various degrees of the vield waveform were recognized through floating capacitors. Regardless, clearly this topology is significantly load-ward and requires propelled capacitor voltage modifying figurings, are tumbled to outline the stunned yield voltages, where the amount of levels is a component of the transformers' turns extents. Despite the way this has diminished the required DC power supplies, the huge number of single-arrange transformers makes it unfeasible and not charming as the size and multifaceted nature increases with every additional level in the yield voltage [11]. It pushes toward getting to be at any rate on different occasions when extended to three-arrange variation [17-20, 22]. As needs be, this paper proposes another symmetric three-arrange CMLI reliant on half-associate cells with decreased number of DC power supplies. be considered topology can enlargement and update type of the threearrange topology proposed in [19, 20]. Regardless, practically 30% more voltage levels in the line voltages can be cultivated by utilizing a comparative number of semiconductor devices. Section II displays the action rule of the proposed symmetric CMLI close by its guideline strategy. Zone III shows and looks at picked amusement and probably affirmed results. Assessment between proposed topology conventional CMLI is pulled in SectionIV. Finally, the work is done up in Section V.

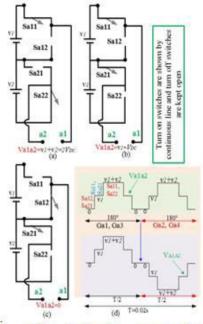

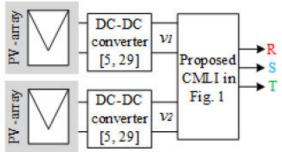

Fig. 1 the proposed three-phase CMLI with two half-bridge cells per phase leg

A Peer Revieved Open Access International Journal

www.ijiemr.org

# II.THE PROPOSED MULTILEVEL INVERTER AND ITSMODULATION STRATEGY

Figure 1 shows the proposed CMLI, incorporates 2 phases. The central stage isa level generator, which makes theunipolar stunned voltage waveformsby using the fell half-lady vital modules. As appeared in Fig. 1, every three half-interface modules in the three-sort out legs-A, B and C are proceeded from a non-kept DC power supply. Extremely, the DC-control supplies can be battery sources, or rectifier yield terminals. Besides. the DC supplies equivalently picked up from photovoltaic (PV) yield terminals or other supportable power source. To perceive suffering yield power and voltage for efficient power wellsprings of irregular qualities, some control figurings, for example, unsurprising voltage source mode can be utilized [29]. It is critical that the half-interface modules will have a practically identical blocking voltage fundamental since they connected over a near DC-supply. This guarantees mien and fundamental control strategies. The ensuing stage is the uttermost point generator, which uses a reasonable full-partner inverter to bipolarize the paralyzed yield voltage waveforms passed on by the standard stage. A threemastermind transformer couples the yields of the farthest point generator with the store, giving a galvanic partition correspondingly as boosting to the yield voltage. It ought to be seen that in spite of the path that in Fig. 1 the transformer right hand windings are related in  $\Delta$ , it could be moreover related in Y, at whatever point required. In addition, the CMLI showed in Fig. 1 can be adequately reached out to make higher number of levels in the yield voltage waveform by including even more halfassociate modules into the level generator.

$$m=2n+1$$

(1)

$v_1 = v_2 \dots = v_n = V_{DG}$  (2)

Where VDC addresses a predictable worth While the half-interface modules in the level generator utilize low voltage, high trading repeat contraptions, the low repeat switches used in the full-associate modules in the furthest point generator experience a voltage stress of a size counterparts to the summation of the information DC voltage sources [20]. In this way, the voltage stress or standing voltage, Vpg, weight on the extremity generator switches can be communicated as,

$$V_{pg, stress} = nV_{DC}$$

(3)

It is to be seen that since they are working at the focal trading repeat of 50 Hz, fullmodules don't demonstrate associate tremendous trading hardships. On the contrary side, top tier development right presently offers trading contraptions, for instance, Insulated Gate Bipolar Transistors (IGBT)- module, FZ500R65KE3 that can withstand a specialist to maker voltage up to 6.5 kV [30]. Additionally, the working voltage cutoff of the trading contraptions can be extended by partner various switches in course of action. Different CMLIs topologies utilizing half-augmentation and H-associate modules have been completed for high voltage applications and can be found in the artistic works [19, 31]. It justifies referencing that as the threephase transformer is a fundamental part in the proposed topology, it will naturally fulfill the galvanic separation essential reasonable power source grid related **Applications**

A Peer Revieved Open Access International Journal

www.ijiemr.org

Fig. 2 switching logics for generating different levels in the level generator output voltages: (a) logic for generating  $2V_{DC}$ , (b) logic forgenerating  $V^{DC}$ , (c) logic for generating  $\theta$ , (d) desired output in the level generator and polarity generator output voltage

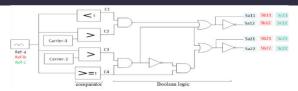

Figures 2(a)- (c) demonstrate diverse exchanging conditions of the level generator, creating distinctive yield voltage levels (v1+v2, v1, 0). Figure2(d) represents the produced AC yield voltage in the extremity generator at stage leg-A, where the extremity generator flipsthe waveform each 1800. The primary focal point of this article is to build up another inverter topology. Customary Sinusoidal Pulse-Width Modulation (SPWM) system is a notable and simple to actualize strategy [32]. Henceforth, SPWM is embraced to show the viability of the proposed topology. As appeared in Fig. 3, the reference signals, Ref-a,Ref-b,Ref-c arethe corrected sinusoidal waveforms with a 1200 stage move from one another. These are then contrasted and two transporter signals (bearer 1 and transporter 2) to produce the required gating signals. Same exchanging signals age rationale is used for each stage leg.

## III.SEMICONDUCTOR LOSSES AND CONVERTER EFFICIENCY

The semiconductor misfortunes are considered as a vital structure and determination measure for any converter circuit as they impact and characterize the required warm administration, which adds estimation of the general cost/volume/weight of the inverter. There are two predominant misfortunes in the semiconductor gadgets; the static and the misfortunes. dvnamic The on-state obstruction and theforward voltage dropof thesemiconductor gadgets are in charge of the conduction misfortunes, while the dynamic misfortunes are delivered during the turn on/off activities managed by the exchanging recurrence of the device.

$$\sigma_{c,T}(t) = [V_T + R_T i^{\beta}(t)]i(t)$$

$\sigma_{c,D}(t) = [V_D + R_D i(t)]i(t)$

(4)

Where, the on-state voltage drops of the transistor and diode are communicated by  $V_T$  and  $V_D$ , separately. The on-state protections of the transistor and diode, are given by  $R_T$  and  $R_D$ , correspondingly.  $\beta$  and i(t) are the transistor enhancement factor and a transistor or diode current at any moment of time, separately.

Henceforth, the normal conduction misfortunes in both, the transistor and the diode, meant by  $P_{c,T}(t)$  and  $P_{c,D}(t)$ , respectively are given by:

$$P_{c,T}(t) = \frac{1}{2\pi} \int_0^{2\pi} [\{V_T + R_T i^{\beta}(t)\} i(t)] d(\omega t)$$

$$P_{c,D}(t) = \frac{1}{2\pi} \int_0^{2\pi} [\{V_D + R_D i(t)\} i(t)] d(\omega t)$$

(5)

The total average conduction losses can then be calculated from,

$$P_{c}(t) = \int_{0}^{2\pi} [\{N_{Transistor}(t) * P_{c,T}(t)\} + \{N_{Diode}(t) * P_{c,T}(t)\}] d(\omega t)$$

(6)

where  $N_{Transistor}$  and  $N_{Diode}$  are the number of transistors and diodes, respectively, in the same current path at any instant of time.

A Peer Revieved Open Access International Journal

www.ijiemr.org

Fig. 3 Block diagram of the modulation technique

$$E_{on} = \int_{0}^{t_{on}} v(t)i(t)dt$$

$$= \int_{0}^{t_{on}} \left[ \left( \frac{V_{SW}}{t_{on}} * t \right) \left( -\frac{I}{t_{on}} \right) * (t - t_{on}) \right] dt$$

$$= \frac{1}{6} V_{SW} * I * t_{on}$$

$$E_{off} = \int_{0}^{t_{off}} v(t)i(t)dt$$

$$= \int_{0}^{t_{off}} \left[ \left( \frac{V_{SW}}{t_{off}} * t \right) \left( -\frac{I'}{t_{off}} \right) * (t - t_{off}) \right] dt$$

$$= \frac{1}{6} V_{SW} * I' * t_{off}$$

$$(7)$$

where  $V_{sw}$  and I, represent the off-state voltage and current of the device, respectively. I' represents the device current measured just before the device is turned off. The total switching power losses ( $P_{sw}$ ), for a time-period T can be calculated from,

$$P_{sw} = \frac{1}{\tau} \left[ \sum_{1}^{N_{switch}} \left\{ (N_{on} * E_{on}) + (N_{off} * E_{off}) \right\} \right]$$

(8)

where the number of turn-on and off counts of a switch in a cycle is given by  $N_{on}$  and  $N_{off}$ ; respectively.

The overall semiconductor losses of the proposed CMLI can be estimated by the total conduction and switching losses of all used semiconductors, expressed as:

#### $Ptotal\_loss = (t) + Psw$ (9)

If the output power is  $P_{out}$ , the inverter efficiency  $(\eta)$  can be calculated from:

$$\eta\% = \left(\frac{P_{out}}{P_{total\ loss} + P_{out}}\right) * 100\% \tag{10}$$

Where the output power is calculated from:

$$P_{out} = \sqrt{3} * \frac{3V_{dc}}{\sqrt{2}} * \frac{I_{line}}{\sqrt{2}} * PF$$

(11)

# TABLEI: PROPERTIES SYSTEM SPECIFICATIONS OF THE PROPOSED INVERTER

Input DC sources  $(v_1, v_2)$  60V each

Carrier frequency

4 kHz

Switching controller

TMS320F2812

Ratings of IGBT

HGTG20N60B3D

Magnitudes of the line voltages

270V (peak)

Number of levels in line voltages

13

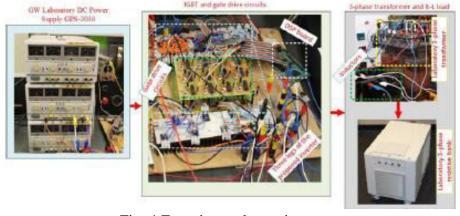

Fig. 4 Experimental test-rig setup

# IV.SIMULATION AND EXPERIMENTAL RESULTS

Fig. 4 shows the trial test-apparatus of the proposed inverter, created at the Green Electric Energy Park (GEEP), Curtin University [33]. Then again, reproduction examination is completed utilizing the

Matlab/Simulink programming bundle. The principle parameters of the inverter model are condensed in Table 1. The information DC voltages from the 'GW Laboratory DC power supplies GPS-3030' are set to give a steady DC voltage of 60V, for example (v1=v2=60 volts). Both, the level generator

A Peer Revieved Open Access International Journal

www.ijiemr.org

and extremity generator stages require twelve IGBTs, each. An advanced sign processor (DSP), TMS320F2812 is utilized to create the constant exchanging door signals. The door signals from the DSP are associated with the IGBT entryways through 24-entryway drive circuits. The job of entryway drive circuits is to detach the shared conviction of the DSP yield door heartbeats and lift up their sizes to almost 15 volts. As appeared in Fig. 4, there are two printed circuit sheets including 24-entryway drive circuits for the 24 IGBTs in the level generator and extremity generator stages. In this paper, the customary SPWM balance technique is considered with a transporter recurrence of 4kHz for both, reproduction and test thinks about. The adjustment record Mi is communicated as [32].

$$M_i = \frac{A_m}{(N_p - 1)A_c} \tag{12}$$

where Am is the greatness of the reference sine waveform and AC is the size of the bearer signal. Regulation file, Mi has an effect on the extent of the yield line voltages and line flows [32]. The yield of the extremity generator is associated with the essential of a three-stage segregation transformer with a turn proportion of 1:1, as appeared in Fig. 4.

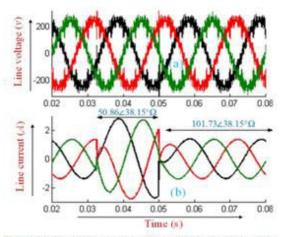

Fig. 5 Simulation results of the output line voltages and line currents for (a) load of nearly 0.8-lagging power factor and (b) load of nearly unity power factor

$$\begin{bmatrix} V_{RS} \\ V_{ST} \\ V_{TS} \end{bmatrix} = \frac{1}{3} \begin{bmatrix} 2 & -1 & -1 \\ -1 & 2 & -1 \\ -1 & -1 & 2 \end{bmatrix} \begin{bmatrix} V_{C1C2} \\ V_{B1B2} \\ V_{A1A2} \end{bmatrix}$$

(13)

$$\begin{bmatrix} V_{RS} \\ V_{ST} \\ V_{TS} \end{bmatrix} = \begin{bmatrix} 1 & -1 & 0 \\ 0 & 1 & -1 \\ -1 & 0 & 1 \end{bmatrix} \begin{bmatrix} V_{C1C2} \\ V_{B1B2} \\ V_{A1A2} \end{bmatrix}$$

(14)

The performance of the proposed inverter undervarious loading conditions is assessed as elaborated in the following cases tudies.

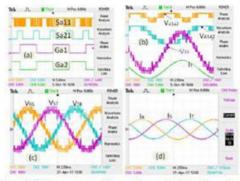

Fig. 6 Different experimental results for phase leg-A with a load of nearly 0.8 lagging power factor: (a) gate pulses in half-bridge and full bridge module at phase leg-A, (b) level and polarity generator output voltages along with the line voltage and line current for phase leg-A, (c) three phase line voltages and (d) three phase line currents.

# A. Case study 1: The impact of load power factor

Fig. 5 shows the simulated results of the line voltage and line current waveforms of the proposed inverter under load power factor of nearly 0.8 (lagging) and unity power factor, when each phase leg is connected with balanced inductive loads of  $(20+j15.7\Omega)$  and  $(20+j1.57\Omega)$ , respectively.

Fig. 7 Different experimental results for phase leg-A with a load of nearly unity power factor: (a) gate pulses in half-bridge and full bridge module at phase leg-A, (b) level and polarity generator output voltages along with the line voltage and line current for phase leg -A, (c) three phase line voltages and (d) three phase line currents.

A Peer Revieved Open Access International Journal

www.ijiemr.org

Then again, Figs.6&7 outline distinctive trial resultsfor about 0.8 slacking and solidarity powerfactorloads, individually. TektronixTPS2014B advanced capacity oscilloscopeis used for catching exploratory waveforms and showing their symphonious ranges. It merits referencing that, no consonant channels were used while taking the outcomes. Figs.6(a)&7(a) represent the test gatingsignals forboth, the levelgenerator and extremity generator switches, Sa11,Sa21,Ga1,Ga2in stage leg-A. The comparing levelgenerator yield voltage extremity (Va1a2)the generator voltage (VA1A2), line voltage (VTR) and linecurrent (IT) are appeared in Figs. 6(b) & 7(b). Also, Figs. 6(c), 6(d) and 7(c), 7(d) demonstrate the 3stage linevoltages and line flows, individually.

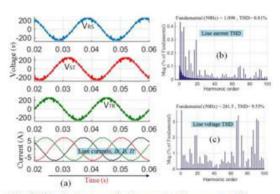

Fig. 8 THD results for nearly 0.8 lagging PF load:

(a) THD for line voltage waveform, (b) THD for line current waveform

The all out symphonious twists (THD) of the line voltage and line current waveforms of the two cases above are appeared in Figs. 8 and 9, separately. It tends to be seen that the difference in the heap PF from 0.8 slacking to solidarity does not impact the quantity of levels in the line voltage waveforms. Be that as it may, the THD in the line voltage and line current waveforms is changed because of the adjustment in the heap PF.

Fig. 9 THDresults fornearly unityPFload:

- (a) THDfor linevoltagewaveform,

- (b) THDfor linecurrentwaveform

It merits referencing that the inductance of an inductive burden goes about as a linecurrent symphonious channel [34], thus, the linecurrent contains sounds on account of 0.8 slacking PF load instead of solidarity PF load. The THD of the line current waveforms is under 5% inboth stacking conditions, which fulfills the IEEEstandard[35]. Then again, the estimation of voltage THD is not exactly the fell MLIproposed in [18-20, 22]. The linevoltage THD canbe kept inside worthy point of confinement, if a little channel is associated at the yield terminals orthrough expanding the quantity oflevels inthe linevoltages by falling all morehalf-connect cells ineach stage leg.

Fig. 10 Simulation results for a dynamic change in the load from nearly unity PF  $(100.31 \angle 4.49^\circ\Omega)$  to 0.8 lagging PF  $(127.13 \angle 38.13^\circ\Omega)$ : (a) level generator output voltage, (b) polarity generator output voltage (phase voltage) and (c) line voltage and line current

A Peer Revieved Open Access International Journal

www.ijiemr.org

## **B.**Casestudy **2:** Theperformance of inverter underloaddynamics

Inverter yield voltage&current waveforms are seen during burden dynamic conditions. Fig.10 demonstrates the reproduction results when heap of almost solidarity powerfactor  $(100+j7.85\omega)$  per stage leg) changed at t=0.0325s to  $100+j78.5\omega$  per stage leg. It expected that this change goes on for a span of 0.0175s afterwhich the first burden is held.

Fig. 11 Simulation results for a dynamic change in the load from nearly 0.9 lagging PF (108.01∠22.21°Ω) to 0.7 lagging PF (142.88∠45.58°Ω): (a) level generator output voltage, (b) polarity generator output voltage (phase voltage) and (c) line voltage and line current

In spite of the fact that alittle mutilation canbe seen in the line voltage waveforms in Fig. 10(c) during the change time frame, no impact is found on the level generator yield voltages appeared in Figs. 10(a)&10(b). Comparable perception can be found in Fig. 11 when a heap of  $100+j40.82\omega$  per stage leg changes to  $100+j102.05\omega$  per stage leg at t=0.0325s for a term of 0.0175s.

Fig. 12 Simulation results for a dynamic change in the load magnitude with the same PF: (a) Line voltage, (b) Line current

The presentation of the proposed CMLI is likewise examined withan adjustment in the heap size with a similar powerfactor. Fig. 12 demonstrates the inverter linevoltage and line current waveforms whenthe heap is multiplied at t=0.0325s for a term of 0.0175s. Same perceptions in the over two cases can be seen for this situation study also.

Fig. 13 Simulation results for carrier frequency of 8 kHz: (a) line voltages and currents, (b) line current IHD, (c) line voltage IHD

# C. Case study 3: Impactofchanging the carrierfrequency on the inverter performance

To evaluate the exhibition oftheproposed inverterwithhigh bearer recurrence, the transporter recurrence is expanded from 4kHz to8kHz. Fig.13 demonstrates the inverter's yield linevoltages and line flows at 8 kHz bearer recurrence and a heap of

A Peer Revieved Open Access International Journal

www.ijiemr.org

$20+j15.7\omega$  Fig. 11 Simulationresults fora powerful changeinthe heap from about 0.9/stage leg. For this situation, the THD of the linevoltage and lineslacking PF(108.01 22.21° $\omega$ ) to 0.7 slacking PF (142.88 45.58° $\omega$ ): (a) levelgenerator yield voltage, (b) extremity generatoryield voltage (stage)

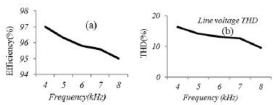

Fig. 14 Effect of carrier frequency on (a) Semiconductor efficiency, (b) Line voltage THD

The efficiency of the proposed inverter and the quality of the linevoltage waveformsare evaluated ina wide range ofcarrier frequenciesFigs.14(a)&14(b) show the THD linevoltagewaveforms andinverter semiconductorefficiency for a setof carrier frequencies. Whilethe quality linevoltagewaveforms is found betterfor highercarrier frequenciessemiconductor efficiencydegrades withhigher frequencies dueto increased switchinglosses.

Table 2: InverterPerformance AtDifferent ModulationIndex (BasedOnSimulation Results)

|                                 | _     |       |      | _    |      |

|---------------------------------|-------|-------|------|------|------|

| Modulation index                | 0.6   | 0.7   | 0.8  | 0.9  | 1    |

| Inverter efficiency (%)         | 76    | 80    | 94   | 95   | 97   |

| Peak line voltage (V)           | 190   | 200   | 210  | 250  | 270  |

| Peak line current (A)           | 3.3   | 3.54  | 3.8  | 4.6  | 5.2  |

| THD <sub>line voltage</sub> (%) | 38.11 | 36.92 | 34   | 23.3 | 15.6 |

| THD <sub>line current</sub> (%) | 3.62  | 2.51  | 2.14 | 1.53 | 1.37 |

A wide scope of SPWM exchanging recurrence (1 kHz to 12 kHz) hasbeen A A A wide scope of the proposed in the writing for various staggered inverterstopologies [19, 22, 36, 37]. The ideal exchanging recurrence is an exchange of the the yieldvoltage and henceforth the size of the framework. As indicated by Fig. 14(a), to keep up the proficiency of the proposed

current waveforms is decreased from 15.6% and 1.37% if there should be an occurrence of and (c) line voltage and line current 4 kHz bearer recurrence to 9.55% and 0.81%; individually if there should be an occurrence of 8 kHz transporter recurrence.

inverterat97% or over, a bearer recurrence of4kHzis considered. The productivity will be diminished to 95.8% if a transporter recurrence of6kHz is utilized. Then again, theline voltageTHD comparing to 4 kHz bearer recurrence 15.6% while it marginally decreased 13.14% with a to transporter recurrence of6kHz. Thus, forthe proposedtopology a transporter recurrence of4kHz gives an attractive execution as far as inverter effectiveness and nature ofthe yield waveforms. Atthis recurrence, the THD inthe linecurrent was observed tobe1.37% according theabove to contextual investigations.

## **D.**Casestudy4: Impact of Modulation index

Tab2 demonstrates theinverter proficiency oftheinverter extents linevoltage and linecurrent for various balance files, Miwhen the inverteris stacked by 20+j15.7ω ineach stage legand worked at transporter recurrence of 4 kHz. effectiveness essentially diminished when under0.8.Table2 Mi is likewise demonstrates that while the sizes of the linevoltage and linecurrent increment withthe expansion of the regulation record, theTHD in the two waveformsis diminishing.

A Peer Revieved Open Access International Journal

www.ijiemr.org

Fig. 15 Simplifiedblock diagramfor PVCMLI -application of the proposed

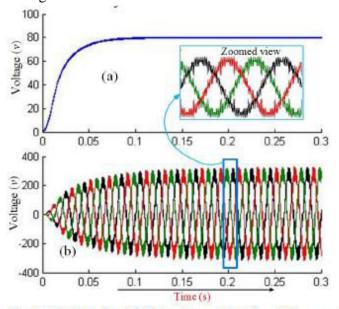

#### E.Casestudy 5: photovoltaicapplication

Asreferenced ofsegmentII, the information DCsupplies canbe acquired fromphotovoltaic yield terminals orother sustainable power source. For situation studythe achievability of the proposed inverterwithPV framework is surveyed. The exhibition of the proposed inverter is researched supplanting the two info

**DC**power supplies inFig.1 bytwo PVmodules. A square graph of PV-cluster associated with the proposedCMLI inthis paper is appeared inFig.15. DC-DCconverter is used to keep up the DC voltages v1 and v2 at consistent levels according to the control approach proposed in [5, 29]. It is accepted that steady voltagecontrol calculation as introducedin[5, 29] used to keep up the PV-modules yield voltage at 80 volts as appeared in Fig. 16(a). With a heap of 20+j15.7ω, theMLI yield linevoltage waveformsare appeared as inFig.16(b). The quantity oflevels and the THD of the yield linevoltage waveforms stay unaltered contrast with vield waveformsdelineated in Casestudy1.

Fig. 16 PV application: (a) PV module output voltage, (b) proposed inverter output line voltage

Notwithstanding their applicationin PV control transformation, halfbridgemodule based staggered invertershavebeen additionally used formedium voltageand electric electric applications as announced in [18, 38]. Itis normal that the topology proposed in this paper likewise be used for the

previously mentioned applications and give extra points of interest, for example galvanic disengagement and decreased info DC-voltage supplies. As indicated by makers' information sheets [39] used three-stage transformerisof high effectiveness (up to 99%).

A Peer Revieved Open Access International Journal

www.ijiemr.org

TABLE 3

COMPARISON RETWEEN THE PROPOSED TOPOLOGY AND CONVENTIONAL MILE

| COMPARISON BETWEEN THE PROPOSED TOPOLOGY AND CONVENTIONAL MET |               |                  |           |               |  |  |  |

|---------------------------------------------------------------|---------------|------------------|-----------|---------------|--|--|--|

|                                                               | Diode clamped | Flying Capacitor | CHB       | Proposed CMLI |  |  |  |

| Number of clamping diodes [20]                                | 3*(m-1)*(m-2) | 0                | 0         | 0             |  |  |  |

| Number of clamping capacitors [20]                            | 0             | 3(m-1)*(m-2)/2   | 0         | 0             |  |  |  |

| Number of voltage divider capacitors [20]                     | 3*(m-1)       | 3*(m-1)          | 0         | 0             |  |  |  |

| Number of switching devices [20]                              | 6*(m-1)       | 6*(m-1)          | 6*(m-1)   | 3*(m+3)       |  |  |  |

| Number of DC supplies [20]                                    | 1             | 1                | 3(m-1)/2  | (m-1)/2       |  |  |  |

| Output Transformer [28]                                       | 1             | 1                | 1         | 1             |  |  |  |

| Inverter Efficiency [40] [41] [42]                            | Up to 96%     | Up to 97%        | Up to 95% | 97%           |  |  |  |

Consequently, the general proficiency of the proposed inverter won't fundamentally influenced inexamination withother existing halfbridge based CMLI. Also, as this topology requires less number of intensity electronic gadgets in contrast with other fell topologies the general misfortunes are relied upon to be diminished.

#### V.COMPARISON WITH OTHER MLI TOPOLOGIES

#### A. Comparison with

#### conventionaltopologies

Table3 demonstrates ageneral correlation between the proposedCMLI and traditional MLI for example diode clasped, flying capacitor and fell H-connect topologies regarding the gadget check (an element of the quantity oflevels inthe yield voltage, m) and by and large productivity. In opposite with ordinaryMLITable3 demonstrates that the proposed CMLIdoes

is the principle issueof customary diode cinched and flyingcapacitor topologies [20]. Thetable additionally demonstrates that theproposed topologyrequires3(m+3) exchanging different gadgets are topologiesrequire 6(m1)exchanging gadgets. Subsequently, forany number of levels over 5, the proposed CMLI will require minimal number of exchanging gadgets. Besides, the proposedCMLI requires less number of DC supplies than the CHB inverter.

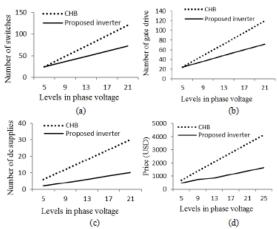

Fig. 17 Device counts and cost comparison with CHB: (a) number of switching devices, (b) number of gate drivers, (c) number of DC power supplies, (d) cost comparison per phase voltage level

InFig.17 demonstrates correlation betweenthe proposedinverter & ordinary course H-connect (CHB)inverter[4243] as a component of the quantity of levels m in the yield voltagewaveform. As appeared in Fig. 17(a-c)execution ofthe proposedinverter callsfor lessnumber of intensity electronicswitches, door drivecircuits and DCsuppliesFig.17(d) demonstrates a cost examination betweenthe proposedCMLI and traditional CHB-basedMLI to get 1.5kV linevoltage. Costestimation (top) inthe incorporates IGBT modules, entryway driversandfull-connect rectifiers depends 2017 market costs [44]. It merits referencing thatathree stage transformer is a fundamental part in he regular staggered inverters for highpower lattice reconciliation to give the requiredgalvanic confinement Consequently, [28]. the detachment

A Peer Revieved Open Access International Journal

www.ijiemr.org

transformer in the proposed topology in this article does not acquire additional cost when the proposed fell inverter is used as a framework associated PV inverter. Fig. 17 demonstrates that the proposed topology is a financially savvy decision when contrasted and the regular CHB staggered inverter topologies.

# **B.** Comparisonwith other half-bridge basedtopologies

The fundamental accentuation ofthe proposed inverter planned for amplifying the quantity of yield voltagelevels with diminished number of DCvoltage supplies by using the symmetryproperties. In this manner, itis basic to contrast theproposed topology and other proportionate halfconnect basedtopologies announced in the writings [18,19,22] affirm its prevalence. As condensed from Table 4, unique angles are considered to draw a reasonable correlation, this incorporates: the quantity ofhalfconnect cells, complete number of intensity electronic exchanging gadgets, door drivecircuits, number of DC-control supplies or DC-interface capacitors, numberofthe voltagelevels feasible vield inthe linevoltages. As can be found in Table 4, theproposedtopology accomplishes higher number of yield voltagelevels by using a similar number of intensity electronic exchanging gadgets and door drivecircuits Strangely, the proposed fell staggered inverter inthis paperrequires the least number of DCsuppliesthan some other topology introduced in Table 4.

#### **VI.CONCLUSION**

Thispaper demonstrates another symmetrical amazed inverter topology with 2 particular stages. The proposed inverter requires less power electronic contraptions and features estimated quality, in this way direct structure, less cost, & high versatility. The amount of data DC-supplies for the

when contrasted and topologies proposed in [18, 19, 22].

In particular, thetopology proposedin[22], requires morethan double the quantity of absolute exchanging gadgets, entryway drivecircuits and DCsupplies for producing lowernumber oflevels in theline voltage contrasted and theproposed topology in this paper. Then again, in spite of the fact that the topologyproposedin[18], requires less numberofsymmetric half-connect cells, it just produces seven-levels inthe yield linevoltage. The topologyproposed in [18] wouldrequire 7symmetric halfbridge modules in each stage leg to create 13-level atthe vield linevoltage, whichis accomplished in the proposed topology inthispaper by just utilizing 3 symmetrichalf-connect modules. This implies, 42-exchanging gadget alongside 19 DC-control supplies willbe required, ifthe topologyproposedin[18], is reached produce 13-levels in the linevoltage.

Table 4 Comparison of the proposed these-phase symmetric half-bridge topology with other half-bridge topologies proposed in the

| LITERATURES                     |                           |                      |                      |                      |  |  |  |  |

|---------------------------------|---------------------------|----------------------|----------------------|----------------------|--|--|--|--|

|                                 | Proposed topology in this | Three phase topology | Three phase topology | Three phase topology |  |  |  |  |

|                                 | рарег                     | proposed in [19]     | proposed in [22]     | proposed in [18]     |  |  |  |  |

| No of half-bridge cells         | 6                         | 6                    | 15                   | 9                    |  |  |  |  |

| No of total switching devices   | 24                        | 24                   | 42                   | 18                   |  |  |  |  |

| No of gate driver               | 24                        | 24                   | 42                   | 18                   |  |  |  |  |

| No of DC supplies or capacitors | 2                         | 6                    | 15                   | 9                    |  |  |  |  |

| No levels in the line voltage   | 13                        | 9                    | 11                   | 1                    |  |  |  |  |

proposedtopology is seen tobe practically 67% not actually the tantamount symmetric halfbridge topologies, whichisa remarkable achievementfor present day applications. This miracle diminish multifaceted design of DC voltage the administrators. Like a symmetric structure, all the trading devices experience same voltage stress, which is a critical factor for high voltage applications. The believability of the proposed inverter is insisted through reenactment and

A Peer Revieved Open Access International Journal

www.ijiemr.org

exploratory assessment for different working conditions.

#### **REFERENCES**

- 1. L.G.Franquelo,J.Rodriguez,J.I.Leon,S.Kour o, R. Portillo, and M. A. Prats, "The period of staggered converters arrives," IEEEIndiaElectronmagazine, volume2,pp. 28-39,2008.

- 2. Nabae,I.Takahashi,H.Akagi,"anothernonpart isan pointclamped PWM inverter,"IEEETrans.Ind.Appl.,pp.518-523,1981.

- 3. S.Kouro, M.Malinowski, K.Gopakumar, J.Po u, L.G. Franquelo, B. Wu, et al., "Ongoing advances and mechanical uses of staggered converters," IEEE Trans. Ind Electron., vol. 57, pp. 2553-2580, 2010.

- 4. B.Xiao,L.Hang,J.Mei,C.Riley,L.M.Tolbert, and B. Ozpineci, "Measured fell H-connect staggered PV inverter with circulated MPPT for matrix associated applications," IEEETrans.Ind.Appl.vol.51,pp.1722-1731,2015.

- J.Pereda, J.Dixon, "High-recurrenceinterface: an answer for utilizing just a single dc source in lopsided fell staggeredinverters," IEEE Trans. Ind. Electron., vol. 58, pp. 3884-3892, 2011.

- 6. MR.Islam,G.Youguang,andZ.Jianguo,"A high-recurrence interface staggered fell medium-voltageconverter fordirect lattice joining of sustainable power source frameworks," IEEETrans.PowerElectron., vol.29pp.4167-4182,2014.

- 7. HAkagi, "Arrangement, wording, and utilization of the modular staggered course converter (MMCC)," IEEE Trans. Power. Electron., vol. 26, pp. 3119-3130, 2011.

- 8. N. Kawakami, S. Ota, H. Kon, S. Konno, H. Akagi, H. Kobayashi, et al., "Improvement of a 500-kW particular staggered course converter for battery vitality stockpiling frameworks," IEEE Trans. Ind. Appl., vol. 50, pp. 3902-3910, 2014.