A Peer Revieved Open Access International Journal

www.ijiemr.org

### **COPY RIGHT**

2019IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 4<sup>th</sup> Sept 2019. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-08&issue=ISSUE-09

Title 1Ø MULTILEVEL INVERTER TOPOLOGIES BY SELF-VOLTAGE EQUIVALENT CAPABILITIES

Volume 08, Issue 09, Pages: 402-418.

**Paper Authors**

### B KARTHIK, B ANWESH KUMAR, K SATYANARAYANA

Anu Bose Institute of Technology K.S.P Road, New paloncha, Bhadradri Kothagudem, Telangana, India

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic

Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

# 1Ø MULTILEVEL INVERTER TOPOLOGIES BY SELF-VOLTAGE EOUIVALENT CAPABILITIES

B KARTHIK<sup>1</sup>,B ANWESH KUMAR<sup>2</sup>, K SATYANARAYANA<sup>3</sup>

<sup>1,2,3</sup>UG Students, Dept. of Electrical and Electronics Engineering, Anu Bose Institute of Technology, K.S.P Road, New paloncha, Bhadradri Kothagudem, Telangana, India. karthikbhukya225@gmail.com<sup>1</sup>, anweshanu291@gmail.com<sup>2</sup>, komaramsatya1999@gmail.com<sup>3</sup>

Abstract: Inthis examination, two new structures of single-stage half and half staggered both symmetrical and hilter kilter arrangements that canbe utilized indrives and controlof electrical machines&association of sustainable power sources. The proposed arrangement utilizes a lessnumber of semiconductor gadgets and DCsources as contrasted and regular and recently created topologies whichlead toa decrease in expense and establishment zone. Theproposed topology represents an indispensable bit of leeway of self-voltage adjusting ofits capacitor voltage paying little mind to load type, load elements and balance record. Additionally, the proposed topology is extended in a fell manner which decreases the multifaceted nature and improves the exhibition essentially. Awide scope of correlation is finishedwith traditional and recently created topologies to demonstrate the predominant exhibition of proposed topologies in regards to an all out number of switches and DCsources. Themulti-bearer beat width balance system is embraced for creating exchanging beats for individual switches. A lab model is produced fortestingthe presentation oftheproposed topology for9-leveland17-levelinverters.

### 1. INTRODUCTION

Staggered inverter (MLI) gives the answer for conquer the voltage confinement of the old style 2-levelinverter and to arrive at the utilizing higher powerlevel by association of different arrangement semiconductor gadgets with reasonable control method. The first MLItopology was presented around fourdecades back, and from that point forward immense push is found inthefield of intensity converters and theirapplications [1–3]. MLI is utilized in highpower applications, for example, AC enginedrive[4, 5], dynamic power channels [6, 7] and reconciliation of sustainable power source intothe framework [8, 9]. Aside fromhigh-voltage similarity, MLI likewise acts advantageous advantages such like improved power quality, diminished absolute consonant twisting, less voltage

worry over the switches, great electromagnetic similarity, decreased exchanging misfortunes dv/dt and stressTraditionally,MLIs are ordered intothree classifications, and they are: fell Hconnect, flyingcapacitor and nonpartisan point braced (NPC) andthese topologies are generally alluded toas 'Old style Topologies' [10, 11]. Notwithstanding, the old style topologies have a few imperatives, for example the quantity of DCsources and switches are expanded which additionally increment fringe gadgets, for example, door driver circuit, insurance circuitand warmth sink. This augmentation in the parts prompts increment in cost, by and large framework multifaceted nature, misfortunes and lessens the dependability and effectiveness of the converter. Consequently, alongside

A Peer Revieved Open Access International Journal

www.ijiemr.org

investigation of old style topologies, a generous push is found in the advancement of use arranged more up date topologieswith decreased a numberof gadgets [12-14] andtheir regulation/control strategies requires a lot of bidirectional switcheswhich increment the misfortunes in theproposed topology as contrasted and regularCHB. Additionally, theproposed topology can't be worked in an uneven mode, thus falls behind ordinary lopsided CHB. The topologyof[18] at first proposes sub-MLIand after that for accomplishing a most extreme number of yield levels in awry setup, the fell structure hasbeen proposed. It requires an alternate assortment ofswitches with respect to blockingvoltage capacities which increment the expense unpredictability ofthe converter. Additionally, the power adjusting among various information sources is unimaginable and subsequently life is diminished. The topologies of [19, 201 utilize the arrangement association of DC sources. Likewise, a fell structure is proposed for acquiring the most extreme number of levels in yield. It requires an enormous number of bidirectional switches which expands the misfortunes the general of proposed topologies inverter. The of [17–20] experience the ill effects of one noteworthy disadvantage, for example the switches of its Hbridge need to hold up under the complete info voltage which limits the activity at higher-voltage levels. topologies of [21-23] propose inverter which decreases switches essentially when contrasted and ordinary CHB. Notwithstanding, both double and trinary blends of DC hotspots for the hilter kilter activity of the proposed topologies are unrealistic because of which it lingers the regular CHB.In symmetrical topology of MLI is proposed

which decreases the quantity of segments and has a basic tweak conspire. Switches of its H-connect need to manage the full evaluated voltage of the inverter which limits its application at high-voltage levels which is a noteworthy inconvenience. In [18], another topology for MLI is proposed, however the primary downsides for this topology are the utilization of bidirectional switches, an assortment of switches and limitation on high-voltage applications. In [25], another symmetrical MLI topology has been proposed utilizing less number of switches and lessening the exchanging misfortunes up, all things considered, as contrasted and regular MLI. Be that as it may, a noteworthy disadvantage is the loss of its measured quality. The topologies of [26, 27] require more switches as contrasted and the proposed topology. In [28], topologies have been displayed for both symmetrical and hilter kilter MLIs, yet the fundamental disadvantage is the scope of accessible power factor being exceptionally thin; just loads with power factor near solidarity can be provided. In [29, 30], two topologies dependent on created H-spans are presented. The principle disadvantage of these topologies is the necessity of countless autonomous DC sources which builds the expense of these topologies. From the above writing, it is reasoned that, to accomplish a higher number of yield levels with a less number of gadgets, extraordinary trade off has been made regarding number of bidirectional switches, unidirectional switches, DC sources, assortment switches, assortment of warmth sinks. assortment of DC sources, unwavering seclusion, straightforwardness, quality, adaptability and exchanging misfortunes. The worry referenced above has been downsized, as it were, in the proposed

A Peer Revieved Open Access International Journal

www.ijiemr.org

topologies.

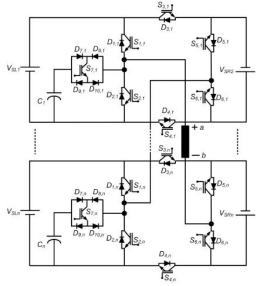

**Fig. 1-**Configuration of the proposed topology-I

Table 1 Switching table for 9-level inverter of topology-I

| Output levels                         | 'ON' state                                       | Effect on capa     | citor voltage      |

|---------------------------------------|--------------------------------------------------|--------------------|--------------------|

|                                       | switches                                         | If ' <i>i</i> ∟>0' | If ' <i>i</i> L<0' |

| C <sub>V</sub>                        | S <sub>4</sub> , S <sub>6</sub> , S <sub>7</sub> | discharging        | charging           |

| V <sub>SR</sub>                       | S <sub>2</sub> ,S <sub>4</sub> , S <sub>5</sub>  | no effect          | no effect          |

| C <sub>V</sub> + V <sub>SR</sub>      | S <sub>4</sub> , S <sub>5</sub> , S <sub>7</sub> | discharging        | charging           |

| V <sub>SL</sub> + V <sub>SR</sub>     | S <sub>1</sub> , S <sub>4</sub> , S <sub>5</sub> | no effect          | no effect          |

| 0 V                                   | S <sub>2</sub> , S <sub>4</sub> , S <sub>6</sub> | no effect          | no effect          |

| -C <sub>V</sub>                       | S <sub>3</sub> , S <sub>5</sub> , S <sub>7</sub> | discharging        | charging           |

| -V <sub>SR</sub>                      | S <sub>1</sub> , S <sub>3</sub> , S <sub>6</sub> | no effect          | no effect          |

| -(V <sub>SL</sub> + V <sub>SR</sub> - | S <sub>3</sub> , S <sub>6</sub> , S <sub>7</sub> | discharging        | charging           |

| C <sub>V</sub> )                      |                                                  |                    |                    |

| $-(V_{\rm SL} + V_{\rm SR})$          | S <sub>2</sub> , S <sub>3</sub> , S <sub>6</sub> | no effect          | no effect          |

A symmetrical topology is introduced in [31] which uses single DC source in parallel of arrangement associated capacitors. The principle disservice of this topology is that solitary symmetrical setup is given. Also, four of its switches need to manage the all out voltage of the inverter limiting its application to medium voltage. topology of [32] proposes a fell variant of the topology of [31] that can be worked at high-voltage levels as the sub-squares are associated in a fell way. In [33], the topology of [31] has been altered to lopsided form to arrive at a greatest number of yield levels. Usage of numerous bidirectional switches is the primary disadvantage of this topology. In [34], the topology of [31] has been displayed for both symmetrical and lopsided MLIs which arrive at a higher number of yield levels. fundamental downside is the prerequisite of an enormous number of autonomous DC sources which builds its expense tremendously.In [35], topology of the MLI is proposed for 5-level inverter utilizing single DC source and two arrangements. In this topology, capacitor voltage of one of the CHB squares is managed by a stage move balance procedure which decreases the quantity of separated DC sources considerably sum. The primary constraint of this topology is that the switches of its fundamental Hconnect need to hinder the all out yield voltage of the inverter which confines its application in higher-voltage application. The topologies of [36–39] propose pressed U-cell topology which diminishes the quantity of confined DC sources by a huge edge contrasted and traditional CHB. The principle bit of leeway of these topologies is that they don't require any outside hardware for keeping up its capacitor voltage in a [40], reasonable state. In another exchanging procedure is created consolidating particular symphonious alleviation and specific consonant disposal strategies for four leg NPC inverter which diminishes the power misfortunes, yet in addition keeps up the DC capacitors voltage in a fair state with low-voltage swells even at lower exchanging frequencies. The topology of [41, 42] proposes topologies of MLI that diminishes the DC source necessity by utilizing capacitors without the help from an outside circuit, for example the topologies of [41, 42] have self-voltage adjusting capacities, yet the two topologies require an enormous number of switches as contrasted and proposed topologies. In this paper, two new topologies are exhibited

A Peer Revieved Open Access International Journal

www.ijiemr.org

which can be worked in both symmetrical just as deviated designs. The proposed topology has a secluded structure as it is associated in a fell manner and gives dependable activity to symmetrical and unbalanced designs with less voltage weight on the semiconductor switches. It doesn't require any outside circuit for adjusting its capacitor voltage because of its self voltage adjusting ability. 'Self-voltage adjusting' signifies the capacity of the capacitor to keep up its voltage in a decent state without requiring any guide from the outer circuit regardless of burden elements, balance file or homeless people. The symmetrical and deviated setups of proposed topologies produce the most extreme number of yield levels with less number of switches and confined DC sources relatively. The quantity of bidirectional switches additionally decreases altogether in the proposed topologies. The proposed topologies likewise have included the upside of equivalent DC source use and misfortunes. A nitty gritty decreased correlation of proposed topologies with traditional topologies and some as of late recently created topologies done dependent on the quantity of switches and DC hotspots for both symmetrical and hilter kilter setups to viably demonstrate the advantages of the proposed topology.

### 2 Proposed MLI topologies

### 2.1 Proposed topology-I:

The summed up arrangement of topology-I in a symmetrical design is appeared in Fig. 1. Every cell in topology-I is made out of seven controlled switches, ten power diodes, two DC sources and one capacitor. The DC source on the left-hand side is numbered as VSL1, VSL2, ..., VSLn and on the righthand side is numbered as VSR1, VSR2, ..., VSRn ('n means the quantity of arrangement cell'). The summed up numerical articulation for topology-I in the symmetrical design for 'N' cells

number of DC sources =

$$2N$$

(1)

number of capacitors =

$$N$$

(2)

number of IGBT's =

$$7 \times N$$

(3)

number of diodes =

$$10 \times N$$

(4)

number of output levels =

$$(8 \times N + 1)$$

(5)

Exchanging plan for 9-level of topology-I is given in Table 1 alongside the capacitor charging and releasing states. It must be noticed that for unadulterated resistive burden, the capacitor releases at voltage levels 'CV' and 'CV+VSR', while charging of capacitor happens at voltage level '-CV' and '(VSL+VSR-CV)'. No different states can influence the capacitor voltages. Fig. 2 shows the progression of current at all the individual levels.

A Peer Revieved Open Access International Journal

www.ijiemr.org

Fig. 2 Current flow direction of topology-I for 9-level output

- (a) Output voltage =  $C_V$ , (b) Output voltage =  $-(V_{SL} C_V)$ , (c) Output

- voltage =  $V_{SR}$ , (d) Output voltage =  $-V_{SR}$ , (e) Output

- (b) voltage =  $(V_{SR}+C_V)$ , (f) Output voltage =  $-(V_{SR}$

A Peer Revieved Open Access International Journal

www.ijiemr.org

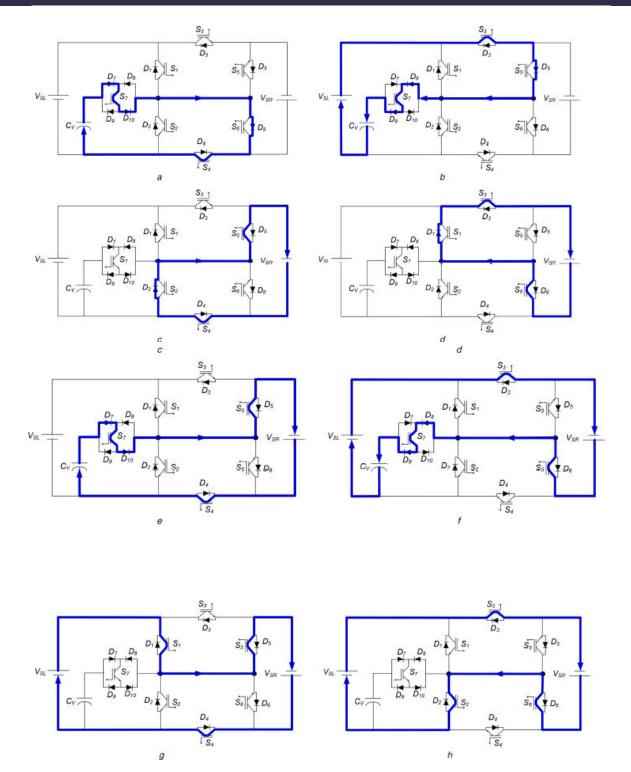

$+V_{SL}$  -  $C_V$ ), (g) Output voltage =  $(V_{SR}+V_{SL})$ , (h) Output voltage =  $-(V_{SR}+V_{SL})$ , (i) Output voltage =  $0_V$  in every cell, and its summed up structure is given in Fig. 3 and called it as proposed topology-II. Like topology-I, the topology-II is likewise associated in a fell way to accomplish seclusion. The DC source on the left-hand side is numbered as VSL1, VSL2, ..., VSLnand on the right-hand side is

numbered as VSR1, VSR2, ..., VSRn. It can likewise be worked as symmetrical arrangement by utilizing similar estimations of DC sources. Table 2 gives the distinctive exchanging states for 9-level yield for the proposed topology-II. For topsy-turvy activity, the estimations of DC sources are allocated by Table 3. In customary lopsided CHB, the

Fig. 3 Configuration of the proposed topology-II

Table 2 Switching table for 9-level inverter of topology-II

| Output Levels                         | 'ON' state switches                              |                                 | acitor voltage                  |              |                    |

|---------------------------------------|--------------------------------------------------|---------------------------------|---------------------------------|--------------|--------------------|

|                                       |                                                  | Capacit                         | or C <sub>L</sub>               | Capacit      | or C <sub>R</sub>  |

|                                       |                                                  | If ' <i>i</i> <sub>L</sub> > 0' | If ' <i>i</i> <sub>L</sub> < 0' | If $i_L > 0$ | If ' $i_{L} < 0$ ' |

| CL                                    | S <sub>4</sub> , S <sub>6</sub> , S <sub>7</sub> | discharging                     | charging                        | no effect    | no effect          |

| $C_L + C_R$                           | S <sub>4</sub> , S <sub>7</sub> , S <sub>8</sub> | discharging                     | charging                        | discharging  | charging           |

| C <sub>L</sub> + V <sub>SR</sub>      | S <sub>4</sub> , S <sub>5</sub> , S <sub>7</sub> | discharging                     | charging                        | no effect    | no effect          |

| V <sub>SL</sub> + V <sub>SR</sub>     | S <sub>1</sub> , S <sub>4</sub> , S <sub>5</sub> | no effect                       | no effect                       | no effect    | no effect          |

| 0 V                                   | S <sub>2</sub> , S <sub>4</sub> , S <sub>6</sub> | no effect                       | no effect                       | no effect    | no effect          |

| -(V <sub>SL</sub> - C <sub>L</sub> )  | S <sub>3</sub> , S <sub>5</sub> , S <sub>7</sub> | discharging                     | charging                        | no effect    | no effect          |

| $-(V_{SL} + V_{SR} - C_L - C_R)$      | S <sub>3</sub> , S <sub>7</sub> , S <sub>8</sub> | discharging                     | charging                        | discharging  | charging           |

| $-(V_{SL} + V_{SR} - C_L)$            | S <sub>3</sub> , S <sub>6</sub> , S <sub>7</sub> | discharging                     | charging                        | no effect    | no effect          |

| -(V <sub>SL</sub> + V <sub>SR</sub> ) | S <sub>2</sub> , S <sub>3</sub> , S <sub>6</sub> | no effect                       | no effect                       | no effect    | no effect          |

A Peer Revieved Open Access International Journal

www.ijiemr.org

Table 3 Realization of different levels of proposed topology-II incorporating 'n' number of cells

| Algorithm | Values of DC sources                                                                                                                                                                                                | Number of output levels                                                                                  | Configuration |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------|

| first     | $V_{\mathrm{SL}1} = V_{\mathrm{SR}1} = \dots = V_{\mathrm{SL}n} = V_{\mathrm{SR}n}$                                                                                                                                 | $8 \times n + 1$                                                                                         | symmetrical   |

| second    | $\frac{V_{\text{SL}1}}{2^0} = \frac{V_{\text{SR}1}}{2^1} = \frac{V_{\text{SL}2}}{2^2} = \frac{V_{\text{SR}2}}{2^3} = \dots = \frac{V_{\text{SL}n}}{2^{2 \times n - 2}} = \frac{V_{\text{SR}n}}{2^{2 \times n - 1}}$ | $4 \times \left[ \sum_{m=1}^{n} (V_{\mathrm{SL}m} + V_{\mathrm{SR}m}) \div V_{\mathrm{SL}1} \right] + 1$ | asymmetrical  |

| third     | $\frac{V_{\text{SL1}}}{3^0} = \frac{V_{\text{SR1}}}{3^1} = \frac{V_{\text{SL2}}}{3^2} = \frac{V_{\text{SR2}}}{3^3} = \dots = \frac{V_{\text{SL}n}}{3^{2 \times n - 2}} = \frac{V_{\text{SR}n}}{3^{2 \times n - 1}}$ | $4 \times \left[ \sum_{m=1}^{n} (V_{\mathrm{SL}m} + V_{\mathrm{SR}m}) \div V_{\mathrm{SL}1} \right] + 1$ | asymmetrical  |

| fourth    | $V_{\rm SL1} = {\rm initialise}$                                                                                                                                                                                    | $4 \times \left[ \sum_{m=1}^{n} ((V_{SLm} + V_{SRm}) \div V_{SL1}) \right] + 1$                          | asymmetrical  |

|           | $V_{\rm SR1} = 3 \times V_{\rm SL1}$                                                                                                                                                                                | ,,                                                                                                       |               |

|           | $V_{\text{SL}n} = 4 \times \left[ \sum_{m=1}^{n-1} (V_{\text{SL}m} + V_{\text{SR}m}) \right] + V_{\text{SL}1}$                                                                                                      |                                                                                                          |               |

|           | $V_{SRn} = 2 \times \left[ V_{SLn} + \left( \sum_{m=1}^{n-1} (V_{SLn} + V_{SRn}) \right) \right] + V_{SL1}$                                                                                                         |                                                                                                          |               |

estimations of DC sources are doled out in a predefined way of either double (2:1) or trinary (3:1) mix and as needs be the yield levels increment. Be that as it may, some as of late distributed writing demonstrates the working of deviated topology by allocating estimations of DC sources in a predefined way of 4:1 [33], 5:1 [33] and even 7:1 [30], because of which the quantity of yield levels colossally increments as contrasted and hilter kilter CHB. Hence, so as to arrive at the most astounding number of yield levels in the proposed topology-II, another calculation is embraced which is given in Table 3 (fourth calculation).

### 2.3 Capacitor voltage balancing

In the proposed topology, the capacitor voltage consistently stays in a reasonable state independent of the heap type, balance file or burden qualities. Likewise, the proposed topology does not require any convoluted strategies for keeping up its capacitor voltage in a adjusted state. This wonder can be clarified scientifically by ampere-second capacitor equalization condition; as indicated by this condition, the net change in capacitor voltage over single exchanging cycle under enduring state condition ought to be zero. Current crosswise over capacitor is given by

$$i_{\rm C}(t) = C \frac{{\rm d}v_{\rm C}(t)}{{\rm d}t} \tag{6}$$

where  ${}^{(t)}Ct$  ' is the instantaneous capacitor' current and ' $v_Ct$ ' is the corresponding voltage across the capacitor at the same instant.

Integration of the above equation over single switching cycle yields

$$\int_{0}^{T_{S}} i_{C}(t) dt = C \int_{0}^{T_{S}} \left( \frac{dv_{C}(t)}{dt} \right) dt$$

(7)

$$\int_{0}^{T_{S}} i_{C}(t) dt = V_{C}(t) - V_{C}(0)$$

(8)

Presently from (8), it tends to be said that the net change in capacitor voltage over single exchanging cycle is equivalent or corresponding to vital of capacitor current over a similar exchanging cycle. In enduring state, beginning and last estimations of capacitor voltages are the equivalent. In this manner

average capacitor current =

$$\frac{1}{T_{\rm S}} \int_0^{T_{\rm S}} i_{\rm C}(t) \, dt = 0$$

(9)

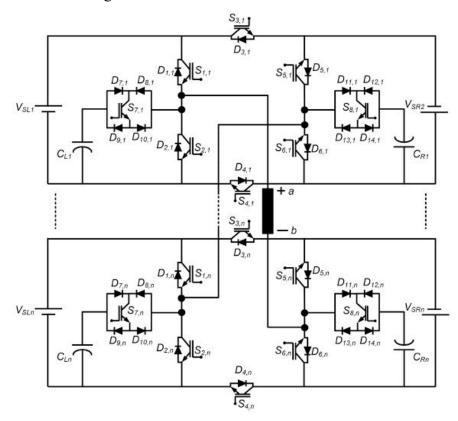

From (9), it tends to be presumed that the normal worth or DC segment of the capacitor current must be zero in harmony. The point by point examination of capacitor voltage adjusting is displayed in Fig. 4a.

A Peer Revieved Open Access International Journal

www.ijiemr.org

### 3 Comparison studies

The proposed topology-I offers more advantages in symmetrical setup and topology-II in a deviated design. Along these lines, in this area, an appropriate correlation is drawn for topology-I in a symmetrical arrangement and topology-II is contrasted and recently created awry topologies.

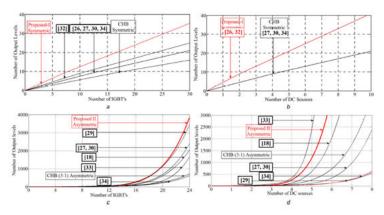

### 3.1 Comparison of symmetrical MLI

Examination of the proposed topology-I with recently created topologies of regular CHB worked in symmetrical arrangement isgiven inFigs.5a and b. It very well may be seen that the proposed topology-I requires measure of switches in minimal symmetrical setup. In addition from Fig. 5b, it very well may be seen that the DCsource prerequisite in the proposed topology-Iis not topologies27,30,34and as much [26, 32]. equivalent to topologies of Henceforth, topology-I the proposed insymmetrical setup requires minimal number of gadgets as contrasted & ordinary and recently created topologies.

### 3.2 Comparison of asymmetrical MLI

Correlation of the proposed topology-II with recently created topologies of 18,27,29,30, 33,34]and regular CHB worked in hilter kilter design is exhibited in Figs. 5c and d. It tends to be seen thatthe proposed topology-Hrequires minimal measure of switchesin awry setup as contrasted and regular topologyand recently created topologies. Likewise, DCsource necessity is less as contrasted and CHBand the recently created of[18,27,29,30,34], topologies requires more sources as the topology of [33] as delineated in Fig. 5d. Fig. 5 demonstrates that the proposed topologies in symmetrical and uneven setups require minimal number of gadgets (switches and DC sources) as contrasted and regular and recently created topologies. In addition, the proposed topologies don't require any outside circuit for keeping up its capacitor voltage in a fair state. Table 4 gives the summed up correlation between the proposed topology-I and recently created topologies for 'N' number of yield levels which incorporates all out parts required for the single-stage inverter. Table 4 likewise gives the examination of different topologies dependent on all out kVA evaluations.

### 4 Simulation and experimental results

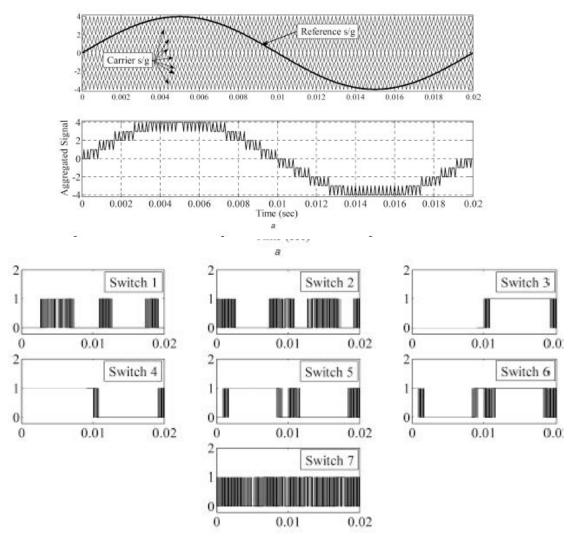

#### 4.1 Modulation scheme

For controlling theswitches, the door sign are created utilizing a reasonable multitransporter beat width tweak (MCPWM) method for bothtopology-Iandtopology-II. The transporter exchanging recurrence is keptat 100Hzand5kHz, though the reference signal recurrence iskeptat 50Hz. InMCPWM procedure, thebeatare produced by reasonable sensible activity among bearer and reference sign and after that the beats are bolstered tothedriver circuitwhich enhances the size of created heartbeats totrigger the individual switch [43]. In MCPWM system, the quantity of transporter sign required is reliant on the quantity of yield levels('M-1'). The essential methodology forMCPWM is given inFig.6a entryway beats forthe proposed topology-I for 9-level aregiveninFig.6b.

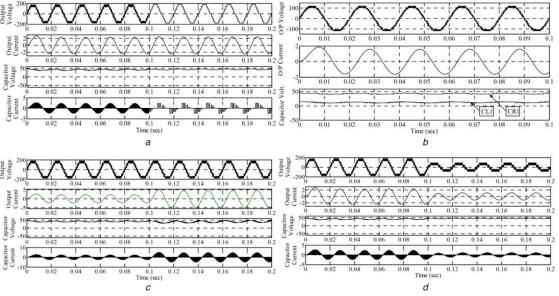

#### 4.2 Simulation results

Totest and look at the exhibition of the proposed topologies, a recreation study has been completed utilizing MATLAB/Simulink. Topology-I is mimicked for symmetrical design as 9-level inverter and topology-II for the 17-level inverter. Diverse recreation and test parameters for both the topologies are given in Table 5. For figuring the capacitor esteem, beneath recipe is utilized:

$$C_{\rm S} \ge (I_{\rm out} \times t_{\rm on})/(\% \text{ripple} \times V_{\rm in})$$

(10)

A Peer Revieved Open Access International Journal

www.ijiemr.org

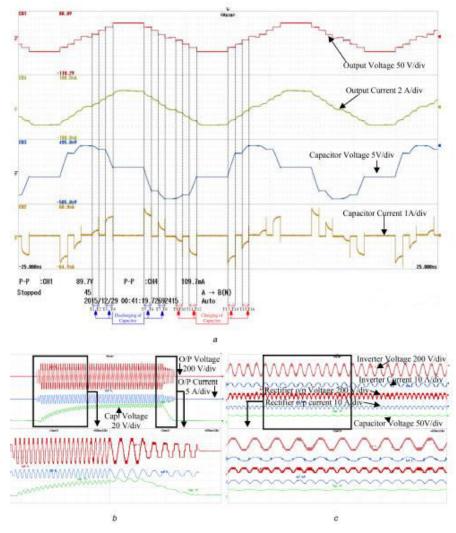

where Iout isthecurrent conveyed bya capacitor, ton isthe charging/releasing time ofthecapacitor, %ripple is the most extreme permissible swell substance incapacitor voltage (10% remittance istaken proposedtopologies) and Vin is the capacitor adjustedvoltage. Fig.7a demonstrates the reenactment consequences design under two diverse exchanging example the exchanging recurrence is all of a sudden changedfrom 5kHzto100Hz.Fig. 7a portrays the waveforms of the yield voltage, yield current, capacitorvoltage and capacitorcurrent. From Fig. 7a, it very well may beseen thatthe inverter exchanging recurrence hasno effect oncapacitor voltage and capacitor keeps up itsvoltage at a fair stateatboth the exchanging frequencies. To look the exhibition of the

kilter proposedtopology-II hilter in arrangement, 17-level yield waveformsare delineated in Fig. 7b. From thewaveforms portrayed in Fig. 7b, it tends to be een that the capacitorvoltage is in a fair state at exchanging recurrence of 5 kHz.To successfully demonstrate the self-voltage adjusting of its capacitorvoltage under unexpected burden change, under various modulationindex and diverse reference frequenciesthe reproduction study iscarried dependent on 9-levelinverter topology-Iandresults aregiven in Figs. 7c and d. Theworking oftopology-I when thesudden burden progress happens at 0.1 s is appeared in Fig. 7c. Itcan be seen from thatat0.1s the yield current Fig. increments;

A Peer Revieved Open Access International Journal

www.ijiemr.org

Experimental Fig.4 results for demonstratingself-voltage balancing capabilities of the proposed topology henceforth, the capacitor current likewise builds, whichresults in more swells in capacitorvoltage, yet at the same time the voltage stays in decent state. Theworking of topology-I when itis changed starting with one balance file then onto the next at 0.1s is appeared in Fig. 7d. It tends to be seen that at 0.1 s whenthe topology is changed solidarity adjustment file to 0.5 tweak file the yield current abatements of whichcapacitor because current additionally diminishes, which at last outcomes in a reduction in capacitorvoltage swell, however with adjusted voltage. Consequently from Figs. 7c and d.it very well may be said thatthe capacitorvoltage inthe proposed topology consistently stays ina fair state, paying little heed to stack elements, adjustment record, exchanging recurrence orreference recurrence.

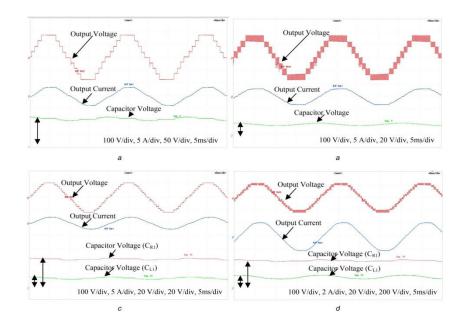

### 4.3 Experimental results

Here the definitely testing theworking of proposedtopologies, alaboratory model hasbeen created forthe 9-/17-level inverter of topology-I&topology-II, individually. For creating the constant exchanging beats, the dSPACE1103 controller hasbeen utilized

and the produced heartbeats are then given to door drivercircuit for intensifying the created heartbeats and afterward at long last nourished separate switches. to exploratory waveforms are dissected by the utilization ofscopecoder YOKOGAWA DL850E. Trial waveform, for example, vield voltage, vield current capacitorvoltages for 9-level proposed topology-I diverse exchanging frequencies is given in Figs. 8a and b. So also, resultsfor 17level of topology-II are givenin Figs. 8c and d. From Fig. 8, it is seen thatthe proposed topology functions atlower just admirably asat higher exchanging recurrence while keeping up itscapacitor voltage in a fair state forboth symmetrical and unbalanced configurations. To look at the charging and releasing ofthe capacitorvoltage in the proposed inverter, a trial study beencarried out for the 9-levelinverter and result is given in Figs. 4a. FromFig. 4a, it tends to be seen thatthe normal estimation of thecapacitor current is constantly zero of every one completecycle. Therefore, it is presumed that voltage ofthe capacitor consistently remains adjusted regardless burden &tweak record.

Fig. 5 Comparison of number of output levels (a) Versus number of IGBT's in symmetrical MLI, (b) Versus number of DC sources in symmetrical MLI, (c) Versus number of IGBT's in asymmetrical MLI, (d) Versus number of DC sources in asymmetrical MLI

A Peer Revieved Open Access International Journal

www.ijiemr.org

Table 4 Generalized comparisons for single-phase symmetrical MLI

| Components                                                                            |                                     |                                  |                                  | MLI to                           | opology                              |                                  |                                  |                                      |                                      |

|---------------------------------------------------------------------------------------|-------------------------------------|----------------------------------|----------------------------------|----------------------------------|--------------------------------------|----------------------------------|----------------------------------|--------------------------------------|--------------------------------------|

|                                                                                       | Topology-I                          | CHB                              | NPC                              | FC                               | [26]                                 | [27]                             | [30]                             | [32]                                 | [34]                                 |

| main switches                                                                         | (N + 19)/4                          | 2(N-1)                           | 2(N-1)                           | 2(N-1)                           | 3(N-1)/2                             | 3(N-1)/2                         | 3(N-1)/2                         | 5(N - 1)/4                           | 3(N-1)/2                             |

| main diodes                                                                           | (N+1)                               | 2(N-1)                           | 2(N-1)                           | 2(N-1)                           | 7(N-1)/4                             | 7(N-1)/2                         | 3(N-1)/2                         | 2(N-1)                               | 3(N-1)/2                             |

| clamping diodes                                                                       | 0                                   | 0                                | (N−1)×(N−<br>2)                  | 0                                | 0                                    | 0                                | 0                                | 0                                    | 0                                    |

| DC bus capacitor/<br>isolated supply                                                  | (N+3)/4                             | (N-1)/2                          | (N-1)/3                          | (N-1)/3                          | (N-1)/2                              | (N - 1)/2                        | (N-1)/2                          | 3(N-1)/4                             | (N-1)/2                              |

| FC                                                                                    | 0                                   | 0                                | 0                                | (N-1) × (N-<br>2)/2              | 0                                    | 0                                | 0                                | 0                                    | 0                                    |

| total number of components                                                            | (1/2)(3N+13)                        | (9/2) × (N –<br>1)               | (N-1) × (3N<br>+7)/3             | (N-1) × (3N<br>+ 20)/3           | 15(N - 1)/4                          | 11(N-1)/2                        | 4(N-1)                           | 4(N-1)                               | 4(N-1)                               |

| total blocking voltage<br>on the switches<br>('V <sub>DC</sub> ' as input<br>voltage) | (17/8) × (N-1) ×<br>V <sub>DC</sub> | 2 × (N - 1)<br>× V <sub>DC</sub> | 2 × (N - 1) ×<br>V <sub>DC</sub> | 2 × (N - 1) ×<br>V <sub>DC</sub> | (9/4) × (N –<br>1) × V <sub>DC</sub> | 2 × (N – 1)<br>× V <sub>DC</sub> | 2 × (N - 1)<br>× V <sub>DC</sub> | (9/4) × (N –<br>1) × V <sub>DC</sub> | (9/4) × (N –<br>1) × V <sub>DC</sub> |

Additionally, a hypothetical clarification of capacitor voltage equalization should be possible from Fig. 4a. It very well maybe seen thatin the positive cycle the capacitor is associated in arrangement with the heap, subsequently releasing wonder happens, though thenegative halfcycle example T9-T10, T11-T12, T13-T14 and T15-T16) thecapacitor associated arrangement withthe sourceand henceforth charging wonder happens. Presently, the time term of charging and releasing is kept up equivalent by utilizing reasonable exchanging procedure. Consequently, net vitality got is equivalent to net vitality conveyed by acapacitor inone complete cycle. Along these lines, capacitorvoltage consistently stays in a decent state. Fig. 4b demonstrates and settlesat half ofthe information voltage, for example 45Vand again returns to zeroatthe switch 'OFF' time. It must be noticed that thecapacitors utilized inthe proposed topologies set aside some effort to arrive at the relentless state conditionwhich causes some postponement while exchanging 'ON' theinverter. This sort of postponement is likewise found in the topologies exhibited in [35-38] additionally utilizes capacitors to decrease the DC source prerequisite. In every thesetopologies, the chargingand releasing procedures are straightforwardly relative to the heap esteem, for example forthe lower estimations of burden the capacitorcharges rapidly & bad habit versa. Totest theselfvoltage adjusting abilities oftheproposed inverter, ithasbeen tried tentatively under non-straight loads, for example, diode rectifierand distinctive burden drifters and regulation records. Fig. 4c demonstrates the non-direct burden, for example diode rectifier. From Fig. 4c, it very well may be said thatthe capacitorvoltage stays in a reasonable stateunder non-straight burden. Consequently, it is seen that independent of burden type, tweak record or burden elements, the capacitorvoltage consistently stays ina fairstate.

### 4.4 Loss analysis and efficiency

Computation of misfortunes isextremely fundamental piece of the framework plan. MLI experiences three methods of tasks and and exchanging mode. In blockingmode, the gadgets need towithstand the voltage over itsterminal, consequently no present will stream inthismode over the gadget because of which the misfortunes in thismodeare viewed as irrelevant. Henceforth, the larger parts of the misfortunes in MLI arein conduction and exchangingmode

$$P_{\text{Total}} = P_{\text{C}} + P_{\text{SW}} \tag{11}$$

A Peer Revieved Open Access International Journal

www.ijiemr.org

Fig. 6 Modulationscheme(a) Modulation strategiesfor the 9-levelMLI, (b) Gatepulses for respectiveswitches for9-level

**Table 5 Simulationand experimentation parameters**

| Parameters              | Topology-I for 9-level | Topology-II for 17-level |

|-------------------------|------------------------|--------------------------|

| source-I                | 90 V                   | 30 V                     |

| source-II               | 90 V                   | 90 V                     |

| capacitor, μF           | 1200                   | 1200                     |

| load resistance, Ω      | 40, 80                 | 40, 80                   |

| load inductance, mH     | 20, 200                | 20, 200                  |

| modulation index        | unity, 0.5             | unity                    |

| switching frequency, Hz | 100 and 5000           | 100 and 5000             |

where  $P_{\text{Total}}$  is the totalloss, i.e. conductionloss ( $P_{\text{C}}$ ) and switchingloss ( $^{P}_{\text{SW}}$ ).

### 4.4.1 Conduction losses:

Conduction mode is depicted as the measure of intensity lost when the gadget is in 'ON' state [44]. Inthispaper, the two diodes and protected entryway bipolartransistors

(IGBTs)are utilized creating yield levels; subsequently, conduction misfortunes for both the gadgets are appeared. First conduction misfortunes for individual

A Peer Revieved Open Access International Journal

www.ijiemr.org

gadgets are determined and afterward summed up to the proposed MLI. The voltagedrop over an IGBT canbe composed as instantaneousvalue of IGBT conductionlosses is

$$p_{\text{C,T}}(t) = V_{\text{CE}}(t) \times i_{\text{c}}(t) = V_{\text{CEO}} \times i_{\text{c}}(t) + r_{\text{c}} \times i_{\text{c}}^{2}(t)$$

(13)

$V_{\text{CE}}(i_{\text{c}}) = V_{\text{CEO}} + r_{\text{c}} \times i_{\text{c}}$  (12) where " $^{V}_{\text{CEO}}$ " is the forwardvoltage drop acrossthe IGBT, " $^{c}_{\text{c}}$ " is the internal resistance of IGBT and " $^{i}_{\text{c}}$ " is the collector current. The

Where ' $i_c t$ ' is the instantaneous current. Average losses can be expressed as

Fig. 7Simulation results

(a) 9-Levelwaveforms oFtopology-I at twodifferent switchin frequencies of 5 kHz and 100 Hz, (b) 17-Level waveforms of topology-II at 5 kHz switching frequency, (c) Suddenload transition, (d) Suddenchange in modulation index, i.e. from unity to 0.5

Fig. 8Experimental results(a)9-Level waveforms of topology-Iat carrier frequency 100 Hz

Vol 08 Issue09, Sept 2019 ISSN 2456 - 5083 Page 414

A Peer Revieved Open Access International Journal

www.ijiemr.org

b) 9-Level waveforms of topology-I at carrier frequency5 kHz, (c) 17-Levelwaveforms oftopology-IIat carrier frequency 100 Hz, (d) 17-Levelwaveforms oftopology-II atcarrier frequency5 kHz

$$P_{\text{C,T}} = \frac{1}{T_{\text{SW}}} \int_{0}^{T_{\text{SW}}} p_{\text{C,T}}(t) \, dt = \frac{1}{T_{\text{SW}}} \int_{0}^{T_{\text{SW}}} (V_{\text{CEO}} \times i_{\text{c}}(t) + r_{\text{c}} \times \hat{\mathcal{L}}(t)) \, dt$$

(14)

$$P_{C,T} = V_{CEO} \times I_{c, av.} + r_c I_{c, rms}^2$$

(15)

where 'Icav .' is the average value of collectorcurrent and 'I<sub>crms</sub>.' isthe rms. value ofcollector current. Similarly, conduction lossesfordiode can alsobe approximatedas

**Table 6** Forwardvoltagedrop and internal resistanceofIGBT anddiode[45]

| _, _        | ,                   | -                   |                                  |                           |                                 |                          |

|-------------|---------------------|---------------------|----------------------------------|---------------------------|---------------------------------|--------------------------|

| Series      | Blocking voltage, V | Current capacity, A | IGE                              | BT.                       | Dic                             | ode                      |

|             |                     |                     | $V_{\mathrm{CEO}}, \ \mathrm{V}$ | $r_{\rm c},~{ m m}\Omega$ | $V_{\mathrm{DO}}, \ \mathrm{V}$ | $r_{ m d},~{ m m}\Omega$ |

| FF600R06ME3 | 600                 | 600                 | 1.9                              | 1                         | 1.95                            | 0.8                      |

| FF600R12KE3 | 1200                | 600                 | 2.15                             | 1.25                      | 2.5                             | 1                        |

| FF500R25KF1 | 2500                | 500                 | 3.6                              | 3                         | 2.8                             | 1.4                      |

**Table 7 Conduction losses for CHB**

| Switch number | Conduction losses<br>FF600R06ME3 |          |  |  |

|---------------|----------------------------------|----------|--|--|

|               |                                  |          |  |  |

|               | IGBT, W                          | Diode, W |  |  |

| 1             | 11.543                           | 7.621    |  |  |

| 2             | 13.044                           | 0.098    |  |  |

| 3             | 5.934                            | 0.489    |  |  |

| 4             | 11.886                           | 0.274    |  |  |

| 5             | 10.627                           | 2.799    |  |  |

| 6             | 13.044                           | 0.098    |  |  |

| 7             | 10.619                           | 1.428    |  |  |

| 8             | 11.886                           | 0.274    |  |  |

| 9             | 9.193                            | 0.900    |  |  |

| 10            | 13.044                           | 0.098    |  |  |

| 11            | 12.491                           | 2.898    |  |  |

| 12            | 11.886                           | 2.224    |  |  |

| 13            | 5.458                            | 0.008    |  |  |

| 14            | 13.044                           | 0.098    |  |  |

| 15            | 12.817                           | 6.686    |  |  |

| 16            | 11.888                           | 0.274    |  |  |

| total loss    | 178.406                          | 26.267   |  |  |

**Table 8** Conduction losses for the proposed tonology-I

| Switch number | Conduction losses |          |  |  |

|---------------|-------------------|----------|--|--|

|               | FF600             | R06ME3   |  |  |

|               | IGBT, W           | Diode, W |  |  |

| 1             | 6.509             | 2.108    |  |  |

| 2             | 7.092             | 2.259    |  |  |

| 3             | 25.464            | 0.099    |  |  |

| 4             | 22.800            | 0.170    |  |  |

| 5             | 12.166            | 1.029    |  |  |

| 6             | 14.427            | 1.755    |  |  |

| 7             | 10.847            | 22.110   |  |  |

| total loss    | 99.304            | 29.530   |  |  |

$$P_{\rm C, D} = V_{\rm DO} \times I_{\rm D, av.} + r_{\rm d}I_{\rm D, rms}^2$$

(16)

where  ${}^{\prime}_{DO}$  is the forward voltage drop,  ${}^{\prime}_{d}$ is the on-state resistance and  $I_{Dav}$ ,  $I_{Drms}$  are the average and root-mean square (RMS) current of diode. For calculating the abovementioned losses and to draw a suitable comparisonbetween CHBand proposed inverter, a MATLAB/Simulinkmodel is built inwhich data provided in the datasheets areused. Specificationsof MATLABmodel are:

Total input voltage: 2000 V.

Number of DCsources:four(500Vsuppliedby

each DCsource).

Valueofresistance:  $100 \Omega$ . Valueofinductor: 100 mH.

Table 6 offers the values of the forward fall across IGBT and diodeas obtainedfrom datasheets at the side of itsinternal ofseries resistances for IGBT's FF600R06ME3andFF500R25KF1. **Table** seven offers the worth of conductivity losses forCHB. Table eight offers the conductivity lossesfor proposed-I electrical converter.As may be seen from Tables seven and eight, conductivity losses square measure morein CHB as compared with proposedtopology-I. conductivity losses square measure thirty seventh (approx.) less in proposedtopology-I for each IGBT and diodes as compared with symmetricalCHB. Asseen fromTable eight, within thelowest voltage ratedswitch, i.e. S7, the foremost losses square measure within thediode; this is often as a result of the two-way switch that consists of 1 IGBT and 4 diodes. Hence, mostofthe lossesoccur

A Peer Revieved Open Access International Journal

www.ijiemr.org

within the diode. the very best voltagerated switches havemajor losses in IGBT since the conductivity throughthe diode is negligible.

### 4.4.2 Switching losses:

Calculation of shift losses is complicated asno straightforward equation may be found forvoltage and current throughout a shift transient. shift lossesdepends on variety of shift transitions, i.e.transition from 'ON'to 'OFF' and transition from 'OFF' to 'ON', block voltagecollector current, gate resistance and junction temperature. It conjointly depends on modulation strategy enforced.

$$\Xi_{\text{off, }i} = \int_{0}^{t_{\text{off}}} v(t) \times i(t) \, dt = \int_{0}^{t_{\text{off}}} \left[ \left( \frac{V_{\text{B, }i}}{t_{\text{off}}} \times t \right) \left( -\frac{I}{t_{\text{off}}} \times (t - t_{\text{off}}) \right) \right] \\

dt = 1/6 \times V_{\text{B, }i} \times I \times t_{\text{off}} \tag{17}$$

where  $^{E}_{\text{off}}$ ,  $_{i}$  is the energy of the 'ith' switch,  $^{V}_{\text{B}}$ ,  $_{i}$  is the blocking voltage of the 'ith' switch,  $^{I}$ is the current through the 'ith' switch before turning of  $^{f}$  and  $^{f}$  is the turn-off time of the 'ith' switch. mathematical expression for calculation of energy loss during turn-on period is

$$E_{\text{on, }i} = 1/6 \times V_{\text{B, }i} \times I' \times t_{\text{on}}$$

(18)

where  $E_{\text{on, }i}$  is theenergy loss ofthe '*i*th' switch,  $E_{\text{B, }i}$  is the blocking voltage of the '*i*th'switch,  $E_{\text{on, }i}$  is the current through the '*i*th' switch after turning ON and  $E_{\text{on, }i}$  is the turn-on time of the '*i*th'switch. Hence assuming  $E_{\text{on, }i}$  the total switching powerlosses for individual switch can be calculated as

$$P_{\text{loss}, i} = (E_{\text{off}, i} + E_{\text{on}, i}) \times f_s = \frac{1}{6} \times V_{\text{B}, i} \times I \times (t_{\text{on}} + t_{\text{off}}) \times f_s$$

(19)

where  $f_s$  is the switching frequency of the 'ith' switchand  $f_{loss}$ , i is the power loss for the 'ith' switch. From (19), it is clear that

$$P_{\text{loss}, i} \propto V_{\text{B}} \text{ and } P_{\text{loss}, i} \propto f_{\text{s}}$$

(20)

Asearlier mentioned thatthe obstruction voltage of the H-bridge switches utilized in several topologies hasbeen reduced to 0.5 in proposed topology-I, therefore from (20) it's terribly clear that the switch losses of the

switches of H-bridge scale back to half the polygon cellin proposedtopology. To compare the switch lossesof 9-level symmetrical CHB thereupon of 9-level projected topology-I, (19) will bewritten as

$$P_{\text{loss}} = \frac{1}{6} \times V_{\text{B}} \times I \times (t_{\text{on}} + t_{\text{off}}) \times f_{\text{s}}$$

(21)

Assuming that  $_{\text{on}}^{t}$  &  $_{\text{off}}^{t}$  are of same period and they carry the same current I, (21) can be written as

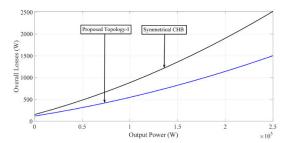

**Fig. 9**Comparison of overalllosses on multipleoperatingpoints

$$P_{\text{loss}} = c \times V_{\text{B}} \times f_{\text{s}} \tag{22}$$

where  $c = \frac{1}{6} \times (I \times t_{\text{on}}) + t_{\text{off}}$  is a constant thus from (22) switching losses for 9-level symmetrical CHB having's voltage source  $V_{\text{DC}}$  can be written as

$$P_{\text{loss, 9-level CHB}} = 16 \times c \times V_{\text{DC}} \times f_{\text{s}}. \tag{23}$$

Now within the projected topology-Ithere's one IGBT with obstruction avoltage of VDC, fourIGBTs with obstruction voltage  $2 \times VDC$ and 2 IGBTswith obstruction voltage 4×VDC. the2IGBTs with obstruction voltage 4×VDC ar switched one time throughout a basic cycleas mentioned earlier. Letthe shift frequency bedenoted by fs and harmonic bedenoted by FO. Then by mistreatment (19), shift losses for 9-level projected inverter-I havingvoltage supply 2VDC will be written as

A Peer Revieved Open Access International Journal

www.ijiemr.org

$$P_{loss, 9-level Prop-1} = c \times (V_{DC} \times f_s + 4 \times 2 \times V_{DC} \times f_s + 2 \times 4 \times V_{DC} \times f_s + 2 \times 4)$$

$$\times V_{DC} \times f_o)$$

(24)

$$P_{\text{loss, 9-levelProp-I}} = 8 \times c \times V_{\text{DC}} \times \left(\frac{9}{8} \times f_{\text{s}} + f_{\text{o}}\right)$$

(25)

Since  $(\frac{9}{8} \times f_s \gg f_o)$ , (25) can be written as

$$P_{\text{loss, 9-level Prop-I}} = 9 \times c \times V_{\text{DC}} \times f_{\text{s}}$$

(26)

From (23) and (26)

$$P_{\text{loss, 9-level Prop-I}} \cong \frac{P_{\text{loss, 9-level CHB}}}{2}$$

(27)

Hencefrom (27), itis clear that theswitching lossesof the 9-level proposedinverter-I are almosthalf as thatof9-level symmetrical CHBunder similar operating conditions.

4.4.3 Overall losses: **Inthis** area, correlation hasbeen made between the proposedtopology and the regular CHB dependent on in general misfortunes and delineated in Fig. 9. For examination reason, the reenactment results havebeen takeninwhich the qualities gave datasheetsare utilized to viably figuring the general misfortunes. To demonstrate the predominance of the proposedtopology over traditional CHB, the recreation results havebeen takenat different working focuses. FromFig.9, it very well may be seen thattheproposed topology haslower general misfortunes as contrasted and CHB.

### 5 Conclusions

This paperproposes two new mixture topologies of symmetrical and unbalanced MLI withthe self-voltage adjusting of its capacitorvoltage and witha number of gadgets. For acquiring the most extreme number of yield levels in awry arrangement, another calculation proposed. Theproposed topologies have been tried tentatively for9-level and 17-level invertersunder various exchanging frequencies. For successfully exhibiting adjusting theself-voltage wonder capacitor voltage, the proposedtopologies havebeen tried undernon-straight burden, responsive burden, under various balance file and diverse burden progress. Awide scope of correlation is drawnbetween theproposed topologies, ordinary andthe recently created topologieswhich demonstrate that theproposed topologies require minimal numberofswitches and DCsources as contrasted and differenttopologies.

#### 6 REFERENCES

- 1. Akagi,H.:'Order, wording, and utilization of the measured staggered course converter(MMCC)', IEEETransPower Electron., 2011,26, (11), pp. 3119–3130

- 2. Liu, C.-H., Hsu, Y.-Y.: 'Plan of a selftuning PIcontroller fora STATCOM utilizing molecule swarm advancement', IEEETransIndElectron. 2010, 57, (2), pp. 70 2–715

- 3. Ristow,A,Begovic,M.,Pregelj, An, etal.: 'Advancement of technique for improving photovoltaicinverter unwavering quality', IEEETrans.Ind. Electron., 2008, 55, (7), pp. 2581–2592

- 4. Hagiwara,M.,Nishimura,K.,Akagi,H.:'A medium-voltageengine drive witha secluded staggered PWMinverter', IEEE TransPowerElectron2010,25,(7),pp.1786 –1799

- 5. Franquelo, L.G. Rodriguez, J., Leon, J.I. et al. 'The time of staggered converters arrives', IEEE Ind Electron Mag., 2008, 2, (2), pp. 28–39

- 6. Cheng, Y. Qian, C. Crow, M. L. et al. 'A correlation of diode-clasped and fell staggered converters for a STATCOM with vitality stockpiling', IEET rans. Ind. Electron., 200653, (5), pp1512–1521

- 7. Barrena, J.A, Marroyo, L., Vidal, M.A.R., et al.: 'Singularvoltage adjusting procedure for PWM fell H-connect converter-based STATCOM', IEE TransInd. Electron., 2008, 55, (1), pp. 21–29

A Peer Revieved Open Access International Journal

www.ijiemr.org

- 8. Alepuz,S.Buquets-Monge,S.,Bordonau, J.,etal.:'Interfacingsustainable power sourcesto the utilitymatrix utilizing a three-levelinverter', IEEETrans. IndElectron2006, 53, (5), pp. 1504–1511

- 9. Walker, G. Sernia, P. 'FellDC–DC converter association of photovoltaic modules', IEEETrans. Power Electron., 2004, 19, (4), pp. 1130–1139

- 10. Nami,A,Zare,F.,Ghosh,An,etal.'Ahalf and half courseconverter topologywith arrangementassociated symmetrical and lopsideddiode-braced H-connect cells', IEEETransPower Electron., 2011, 26, (1), pp51–65

- 11. Veenstra,M.RuferA.'Control of ahalf and half lopsided staggeredinverter forfocused medium-voltage moderndrives', IEEETransIndAppl.,2005, 41, (2), pp. 655–664.