A Peer Revieved Open Access International Journal

www.ijiemr.org

#### **COPY RIGHT**

2019IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 4<sup>th</sup> Sept 2019. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-08&issue=ISSUE-09

Title A NOVEL APPROACH FOR 49-LEVEL STACKED DRIVES FOR INVERTER TOPOLOGY

Volume 08, Issue 09, Pages: 325-336.

**Paper Authors**

#### J UMA MAHESWARI, V SWATHI, D NAVYA PRAVALIKA

Anu Bose Institute of Technology K.S.P Road, New paloncha, Bhadradri Kothagudem, Telangana, India

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic

Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

# A NOVEL APPROACH FOR 49-LEVEL STACKED DRIVES FOR INVERTER TOPOLOGY

J UMA MAHESWARI<sup>1</sup>, V SWATHI<sup>2</sup>, D NAVYA PRAVALIKA<sup>3</sup>

<sup>1,2,3</sup>UG Students, Dept. of Electrical and Electronics Engineering, Anu Bose Institute of Technology KSPRoad, NewPaloncha, Bhadradri Kothagudem, Telangana, India. umamaheswarijukanti@gmail.com<sup>1</sup>, swathi24051998@gmail.com<sup>2</sup>, pravallikadatla333@gmail.com<sup>3</sup>

Abstract:- This article proposes a novel approach for 49-level stacked inverter topology fordrives. The 49 levelsare cultivated by stackingthree 17-levelinverters. All ofthe 17levelinverter is made by falling a flyingcapacitorinverter with 3 capacitor supported Hranges. The contraption count canbe diminished by making theFC and thethree fell H-ranges (CHBs) standard to the DC interface in each stage using selectors witches in them. The selector changes needto work at essential recurrence as it were. Additionally the gadgets need to square lowvoltages. Henceforth MOSFETs canbe utilized. This topologyrequires three DC sources, each of Vdc/6 no one but, which can be supplanted withstackedbatteries for electric vehicleapplications. It decreases in the DC voltage prerequisite is accomplished by utilizing a typical symmetricsix stage enlistment engine (IM) withparallel association of the contrary stage windings. Allthe drifting capacitors in he topology canbe adjusted regardless of any regulation list, burden powerfactor. Because of the highnumber of voltagelevels, closest levelcontrolcan be utilized rather than heartbeat width tweak, which decreases the exchanging misfortunes. The dv/dt duringtheinverter activity is likewise less. Nitty gritty exploratory outcomes at various paces of activity and during homeless people guarantee thatthe novel topology canbea practical choice for highpower flexible speeddrives.

**Index Terms:**-Induction MotorDrive, MultilevelConverter(MLC), Topology, CascadedH-bridge, FlyingCapacitorInverter, NearestLevelControl (NLC).

#### I. INTRODUCTION

Here in staggered inverters (MLI) havegone far sincethe innovation of nonpartisan point braced MLI [1]. The upsides of NPC incorporate diminished ratingofswitches and improved symphonious execution. Later FCwas presented where highernumber of voltage levels was accomplished through a few chargedcapacitors [2]. Dynamic NPCs (ANPC) werethen acquainted with level the misfortunes semiconductorswitches[3]. Asthe quantity of voltagelevels is expanded, NPC experienced impartial point adjusting utilization issues andthe extra powerdiodes. In FC likewise, the quantity of flyingcapacitors definitely expanded and additionally wound up complex. Fell Hconnect topologies are presented which don't havetheabove downsides. Be that as it may, it required extra a few disengaged DC hotspots for producing high ofvoltagelevels[4]. The cumbersome modifiers related withthe frontendDC supplies makeitaless reasonable alternative. Numerous Hybridtopologies are presented concentrating onimproving the quantity of voltagelevels. In [5], a7-leveltopology is created by broadening the possibility of ANPCs. A diminished gadget tally seven

A Peer Revieved Open Access International Journal

www.ijiemr.org

level mixture topologyis examined in[6]. A 9-level MLI sustaining an open finished windingIM is broke down in [7]. A17levelinverter with single DC connect, created by falling a FC withthreeCHBs is depicted in [8]. Additionally researchhas proceeded onward which wipes out low request music relying upon the quantity of sides. To accomplish a close. In three unbalanced DC sources are utilized and a methodology utilizing the volt second equalization is utilized to discover the changing edges to change to the following adjoining voltage level. In a continuous calculation for acquiring the exchanging points is dissected for getting a stage regulation. Comparative investigation is accomplished for staggered converters with differing voltage ventures in. Both of the above calculations don't go through any look tables. In any case, their continuous application should be checked for still bigger numberof voltagelevels in light of the fact that the changing edges to be registered increments with increment inthe quantity of voltagelevels. In a space vector approach for changing to the closest examined reference vector is talked about for a 11level inverter. The partner of this space vector approach for the closest level exchanging is talked about in and this is ordinarily called as closest level control (NLC). In a superior torque and transition control of staggered encouraged IM drive is talked about which uses the closest level exchanging. NLC is carefully not a regulation method. It just changes to the shaft voltage levels closest to the examined estimation of the regulating signal. Because of the enormous number of voltage levels, the related blunder in acquiring the tested vector is irrelevant. Likewise because of the high caliber of yield voltage, torque swell is profoundly decreased and the drive does not require any extra channel. Another

producing inalienable technique for capacitor adjusting. Here every one of the 5level inverter has a DC wellspring of Vdc/2. In, the stacking strategy to assemble a 49level inverter with diminished gadget check is examined. The stacking technique was stretched out to a six stage IM drivein. Itwas appeared insix stage IM drive that asolitary DCsourcewould get the job done, through legitimate choice of exchanging redundancies that guarantees, in exchanging interim. normal midpoint winds current up zero.

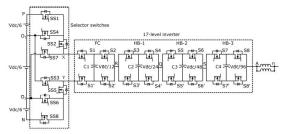

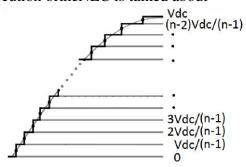

Figure 1: Reduced gadget tally stacked49-levelinvertertopology for stage 'A' by falling a FCwiththreeCHBs andstacking them utilizing selectorswitches.

In this investigation work, a completely 49-level electrical unique converter topology through stacking 3 17-level inverters every of Vdc/3 (which are often reduced to Vdc/6 if a six section machine reconfigured as a 3 section machine is used) is planned. The dv/dt connected with the electrical converter voltages square measure furthermore less. thanks to the low voltage DC sources want at side, they'll be displaced with stacked batteries. It will notice applications in electrical vehicles. All of the 17-level electrical converter is formed by falling a FC with 3 CHBs [8]. For stacking, selector switches square measure used, that lessens the gismo check. The forty nine levels ends up in a thick area vector structure for the straight guideline extend and after the area vector zone nearest to the

A Peer Revieved Open Access International Journal

www.ijiemr.org

reference area vector are often used, that's the NLC [15], [16], helper of the area vector approach are often accustomed deliver the pole voltages that diminishes the mercantilism incidents. From currently on this drive are going to be unusually charming for top management applications.

## II. INVERTER TOPOLOGY AND ITS FEATURES

#### A. Stacked Operation

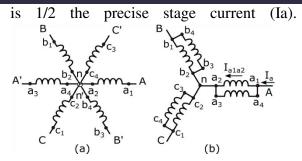

The stacked action to get higher range of voltage levels is mentioned in [18], [20] within sight its numerous options, for 3 section and 6 section IM drives. The higher than work showed the stacked movement for 2 stackings. This work extends it 3|to 3|to a few} stackings with three DC sources as showed up in Fig. 1. The 3 DC sources is shrunken to Vdc/6 (as opposition Vdc/3) if a six section IM is employed during a 3 section contorting arrange by interfacing the a hundred and eighty deg reverse windings in parallel course of action with affordable furthest purpose as showed up in Fig. 2(b). this may reduce the DC interface voltage want at forepart in lightweight of the manner that, for a comparable power yield from a 3 section IM and a six section IM, a six section machine wants solely a large a part of the DC associate voltage. specifically once the DC interface voltage diminishes altogether, the apparent voltages of the capacitors within the FC and therefore the 3 CHB modules reduces considerably and currently MOSFETs is used that improves the adequacy of the drive. it's to be seen that the present through all of the parallel turning (Ia1a2 in Fig. 2(b))

Figure 2. (an) A symmetric six phase IM windings ousted 60 by Reconfigured symmetric six phase turning as a three phase winding, as documented beforehand, the 49-level electrical converter is formed by stacking 3 17-level inverters. All of the 17-level electrical converter is formed by falling a FC with 3 capacitance strengthened HBridges [8]. Here to diminish the gadget count, the 17-level electrical converter is formed typical and therefore the electric switch is joined between the DC interface therefore the and 17-level electrical converter in every part as showed up in Fig.1. The four capacitors in every stage should be maintained at Vdc/12, Vdc/24, Vdc/48 and Vdc/96, so the voltage rating of the switches in FC is Vdc/6 and therefore the voltage evaluations of the switches in HB-1, HB-2 and HB-3 (showed up in Fig. 1) area unit Vdc/24, Vdc/48 and Vdc/96 individually. The switches S1-S1', S2-S2'.....S8-S8' add a correlative structure. intrinsically acceptable deadband should run between them. due to the low voltage assessments of the switches. MOSFETs is used that improves the profitableness on a really basic level. The selector switches relates the 17-level electrical converter to the affordable DC wellspring of Vdc/6 relying upon the pole voltage needed at any minute. The voltage rating of the selector switches is Vdc/6 for the switches SS1, SS2, SS4, SS5, SS6 and SS8 but switches SS3 and SS7 should be evaluated for Vdc/3. The switches SS1SS4, SS6-SS8, SS3-SS5, SS2-

A Peer Revieved Open Access International Journal

www.ijiemr.org

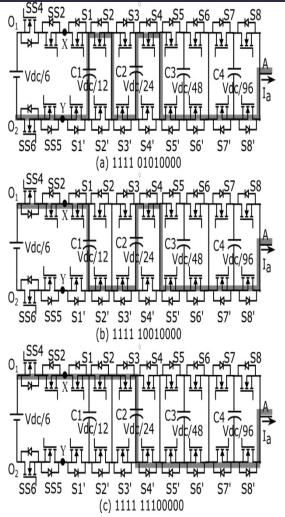

SS7 should be worked in an important structure. so once more acceptable deadband should run between them. The capacitance voltage modifying within the 17-level electrical converter is finished exploitation the post voltage redundancies connected with all of the pole voltages. All of the capacitors contains a skillfulness band delineate within that the voltages have to be compelled to lie throughout the movement of the electrical converter. Fig. three exhibits the dynamic of capacitance voltages exploitation the commercialism state redundancies for shaft voltage of 28Vdc/96. to attain post voltage of 28Vdc/96, ony the center DC supply have to be compelled to be used. Hereafter simply SS4, SS2, SS5, SS6 area unit ON from among the selector switches throughout this post voltage. Fig. 3(a) shows the discharging of C1 and C2 throughout shaft voltage of 28Vdc/96. C1 is charged exploitation redundancy showed up in Fig. 3(b) anyway it discharges C2 any. To charge C2, overabundance showed up in Fig. 3(c) is employed. the various capacitors in stage 'An' area unit unaffected once this post voltage is associated. much identical technique is wont to alter all of the capacitors within the obstruction band within the topology. Here the capacitance voltages area unit balanced in 2 or 3 testing intervals and is solidly compelled by keeping the capacitance on the movement of current or against the movement of current in every examining break, as in an exceedingly flying capacitance topology. therefore merely the capacitance voltage level and course of current stream is needed choose the commercialism redundancy to charge management the capacitance. a section of the references what is more address this issue, for low surprised structures, as documented within the [6],

[8]. This dynamic computation depends upon the commercialism state redundancies of the post voltage levels and therefore real for any operating techniques for the motor or transient conditions. For the 49-level electrical converter, Table-I shows one amongst solely a couple few commercialism state redundancies to attain all of the forty nine shaft voltage levels close its impact on capacitance voltages for positive heading of current stream from the electrical converter to the machine terminal. The movement of the electrical converter is in line with the related . The electrical converter has to create post voltages (VAN) from zero, Vdc/96, 2Vdc/96, 3Vdc/96... up to 48Vdc/96. The voltage VXY is regularly maintained at Vdc/6 through the action of the selector switches. therefore the 17-level electrical converter dependably creates post voltages (VAY) from zero, Vdc/96, 2Vdc/96....upto 16Vdc/96 with reference to Y. The potential at Y regarding N (VYN) will take 3 characteristics, 0, Vdc/6 and Vdc/3 relying upon the short estimation of the modifying signal that is explained beneath. The tweaking sign is scaled to crest estimation of forty eight starting from zero. For the piece of the tweaking sign turned ON and also the 17-level electrical converter is related to the lower DC supply (VO2N) wherever in VYN = zero. once it ranges from sixteen to thirty two, the switches turnedON, throughout that the 17level electrical converter is related to the middle DC supply (VO1O2) wherever in VYN = Vdc/6. what is a lot of, forthe remainder of the partfrom 32to48, the switchesSS1,SS2,SS3 ar turned ON and also the 17-levelinverter is related to the higher DCsource (VPO1) whereby

A Peer Revieved Open Access International Journal

www.ijiemr.org

Figure 3. Capacitorvoltage adjusting utilizing exchanging stateredundancies for shaft voltageof28Vdc/96. Exchanging state is characterized as SS4SS2SS5SS6S1S2S3S4S5S6S7S8. '1' shows switchisON and '0' demonstrates turn isOFF.

$V_{YN} = Vdc/3$ .

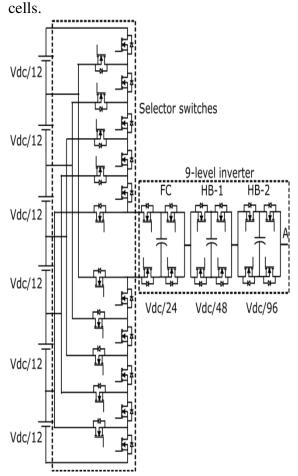

The 49-levelinverter can likewise be created by stackingsix 9-levelinverters utilizing diverse courseof action of selector switchesas appeared in Fig. 4. Here the frontend DCsources required is decreased to Vdc/12, which can be acknowledged utilizing stacked battery cells. Thus it will discover applications in electric vehicles which are additionally sustained from stacked battery

Figure 4. Diminished gadget check 49-levelinverter created by stackingsix9-levelinverters, prompting lowvoltage frontend DC wellsprings of Vdc/12.

A Peer Revieved Open Access International Journal

www.ijiemr.org

Table I: SWITCHING STATES

TOACHIEVE THE 49-POLE

VOLTAGE LEVELS WITHTHEIR

EFFECT ON THE

CAPACITORVOLTAGES

| St No | V <sub>AN</sub> | Switching States  | C1 | C2 | C3 | C4 |

|-------|-----------------|-------------------|----|----|----|----|

| 1     | 0               | 11100000-00000000 | U  | U  | U  | U  |

| 2     | Vdc/96          | 11100000-00000001 | U  | U  | U  | D  |

| 3     | 2Vdc/96         | 11100000-00000100 | U  | U  | D  | U  |

| 4     | 3Vdc/96         | 11100000-00000101 | U  | U  | D  | D  |

| 5     | 4Vdc/96         | 11100000-00010000 | U  | D  | U  | U  |

| 6     | 5Vdc/96         | 11100000-00010001 | U  | D  | U  | D  |

| 7     | 6Vdd/96         | 11100000-00010100 | U  | D  | D  | U  |

| 8     | 7Vdd/96         | 11100000-00010101 | U  | D  | D  | D  |

| 9     | 8Vdc/96         | 11100000-10000000 | D  | U  | U  | U  |

| 10    | 9Vdd/96         | 11100000-01000001 | D  | U  | U  | D  |

| 11    | 10V dc/96       | 11100000-01000100 | D  | U  | D  | U  |

| 12    | 11Vdc/96        | 11100000-01000101 | D  | U  | D  | D  |

| 13    | 12V dc/96       | 11100000-01010000 | D  | D  | U  | U  |

| 14    | 13V dc/96       | 11100000-01010001 | D  | D  | U  | D  |

| 15    | 14V dc/96       | 11100000-01010100 | D  | D  | D  | U  |

| 16    | 15V dc/96       | 11100000-01010101 | D  | D  | D  | D  |

| 17    | 16V dc/96       | 11100000-11000000 | U  | U  | U  | U  |

| 18    | 17V dc/96       | 01011100-00000001 | U  | U  | U  | D  |

| 19    | 18V dc/96       | 01011100-00000100 | U  | U  | D  | U  |

| 20    | 19V dc/96       | 01011100-00000101 | U  | U  | D  | D  |

| 21    | 20V dc/96       | 01011100-00010000 | U  | D  | U  | U  |

| 22    | 21Vdc/96        | 01011100-00010001 | U  | D  | U  | D  |

| 23    | 22V dc/96       | 01011100-00010100 | U  | D  | D  | U  |

| 24    | 23V dc/96       | 01011100-00010101 | U  | D  | D  | D  |

| 25    | 24V dc/96       | 01011100-10000000 | D  | U  | U  | U  |

| 26    | 25V dc/96       | 01011100-01000001 | D  | U  | U  | D  |

| 27    | 26V dc/96       | 01011100-01000100 | D  | U  | D  | U  |

| 28    | 27V dc/96       | 01011100-01000101 | D  | U  | D  | D  |

| 29    | 28V dc/96       | 01011100-01010000 | D  | D  | U  | U  |

| 30    | 29V dc/96       | 01011100-01010001 | D  | D  | U  | D  |

| 31    | 30V dc/96       | 01011100-01010100 | D  | D  | D  | U  |

| 32    | 31Vdc/96        | 01011100-01010101 | D  | D  | D  | D  |

| 33    | 32V dc/96       | 00001011-11000000 | U  | U  | U  | U  |

| 34    | 33V dc/96       | 00001011-00000001 | U  | U  | U  | D  |

| 35    | 34V dc/96       | 00001011-00000100 | U  | U  | D  | U  |

| 36    | 35V dc/96       | 00001011-00000101 | U  | U  | D  | D  |

| 37    | 36V dc/96       | 00001011-00010000 | U  | D  | U  | U  |

| 38    | 37V dc/96       | 00001011-00010001 | U  | D  | U  | D  |

| 39    | 38V dc/96       | 00001011-00010100 | U  | D  | D  | U  |

| 40    | 39V dc/96       | 00001011-00010101 | U  | D  | D  | D  |

| 41    | 40V dc/96       | 00001011-10000000 | D  | U  | U  | U  |

| 42    | 41Vdc/96        | 00001011-01000001 | D  | U  | U  | D  |

| 43    | 42V dc/96       | 00001011-01000100 | D  | U  | D  | U  |

| 44    | 43V dc/96       | 00001011-01000101 | D  | U  | D  | D  |

| 45    | 44V dc/96       | 00001011-01010000 | D  | D  | U  | U  |

| 46    | 45V dc/96       | 00001011-01010001 | D  | D  | U  | D  |

| 47    | 46V dc/96       | 00001011-01010100 | D  | D  | D  | U  |

| 48    | 47V dc/96       | 00001011-01010101 | D  | D  | D  | D  |

| 49    | 48V dc/96       | 00001011-11000000 | U  | U  | U  | U  |

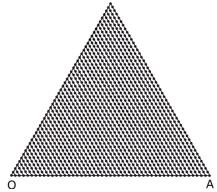

#### **B. Nearest Level Control**

NearestLevelControl or its spacevector partneris utilized whenthe quantity of produce is very high [15], [16]. Ina regular spacevector PWM, the examined vectoris arrived at the midpoint of out in an inspecting timewiththethree adjoining vectorswhich structures thetriangle, wherein the tipofthe tested vectorlies yet when there are enormous number of voltage levels, very thick as appeared in Fig. 7 for the 49-level invertertopology andthe inspected vector lies in all respects near the genuine space vector area. Sothe closest spacevector area is changed prompting just an exceptionally little stator transition swell vector [22] which means that the voltageTHD. The execution of the NLC is talked about

Fig5. NearestLevelControl accomplished by changing tothe closest accessible voltagelevel'n' represents the greatest number of reachable post beneath. The testing recurrence is taken as indispensable numerous of the working recurrence. The examples per cycle are taken as a various of to have both 3-stage and wavesymmetry. As referenced previously, the regulating sign is scaled from 0 to 48. The tested adjusting sign worth is part into a fundamental and fragmentary part where the necessary part is the most minimal whole number not exactly or equivalent to the

A Peer Revieved Open Access International Journal

www.ijiemr.org

inspected worth. The partial part chooses whether to change to the following neighboring voltage level or stay in the present voltage level. Contingent upon the post voltage level, capacitor voltage status and the present bearing, fitting exchanging state repetition is chosen. This exchanging state repetition guarantees that the capacitor voltages are well inside the resistance band in each examining interim. A similar procedure is accomplished for all the shaft voltage levels utilizing DSP and FPGA and the inverter produces the required number of post voltage levels relying upon the speed order.

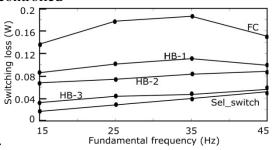

#### C. Switching Loss

The mercantilism mishap connected with the electrical converter is attributable to the setbacks on account of the switchings within the selector switches, the FC and also the 3 CHBs. The switchings within the selector switches square measure the smallest amount and also the switchings will increase from the FC to the 3 CHBs however the interference voltages reduces basically on moving from FC to the CHBs. therefore the mercantilism adversities square measure controlled

Figure 6. Selectorswitches, FCandthe H-bridges (Fig. 1) switchinglossesat various frequencies of operation.

The quantity of shaft voltage exchanging's at various frequencies of activity for the for stage 'An' are classified in Table-II. The general misfortunes of the inverter for various 7.5KW, 415V framework is considered in the reenactment for

computation of the exchanging misfortunes. The exchanging vitality misfortune (ESW) related with the MOSFET can be determined utilizing the formulae,

$$E_{\,\mathrm{SW}} = \frac{V_{\,\mathrm{b}} \star i(t)}{2} \star (t_{\,\mathrm{S(L-H)}} + t_{\,\mathrm{S(H-L)}})$$

V<sub>b</sub> is the blocking volatge ofthe switch and i(t) is the

Figure 7. Highly densespacevector (SV) structure of 49-levelinvertertopology for 60deg (sector-1). Dots

indicatetheSVlocations.OA=Vdc

Ouick estimation of the current. individually is considered for the misfortune computation. From thedatasheet. progress times, tS(L-H)andtS(H-L)arenoted. Point by point technique on the most proficient method to ascertain the MOSFET misfortunes isgivenin [17]. ESW determined overacycle, is partitioned by the time frame getthepower essential to misfortune. It very well may be een from Fig.6that the exchanging misfortune related withthe selector switches, which need hinder the most elevated voltage (Vdc/6), isthe least. The misfortunes related with different modules are practically identical sincethe modules with the most elevated switchings needto hinder the least voltage, as obvious from Table-II. For diminishing the conduction misfortunes in such topologies, where the yield waveforms are almost sinusoidal with less switchings, gadgets with extremely low Rds-on like the SiCbased gadgets must beconsidered or the

A Peer Revieved Open Access International Journal

www.ijiemr.org

ease MOSFETs canbe paralleled which additionally bring about decreased conduction misfortunes. The warmth sink configuration depends onthe powerloss of themodule which disseminates the most extreme misfortunes. Intheproposed plan the action disseminate greatest power when contrasted with the lowvoltage fell Hconnect modules. Sothe warmth sink configuration canbe founded onthe greatest power scattering modules. Be that as it may, this can be additionally decreased and furthermore the conduction term of these modules, (1/n)\*T stacked modules and T is the crucial yield time frame will likewise lessen as the quantity of stacking increments. Table II: POLEVOLTAGE SWITCHINGS (FIG. 1) FORPHASE'A'

| Operating frequency | Selector<br>(V <sub>XN</sub> ) | FC<br>(V <sub>RN</sub> ) | HB-1<br>(V <sub>QR</sub> ) | HB-2<br>(V <sub>SQ</sub> ) | HB-3<br>(V <sub>AS</sub> ) |

|---------------------|--------------------------------|--------------------------|----------------------------|----------------------------|----------------------------|

| 15 Hz               | 4                              | 56                       | 102                        | 142                        | 172                        |

| 25 Hz               | 4                              | 30                       | 71                         | 110                        | 128                        |

| 35 Hz               | 4                              | 28                       | 48                         | 86                         | 109                        |

| 45 Hz               | 4                              | 17                       | 47                         | 82                         | 102                        |

#### III. EXPERIMENTAL RESULTS

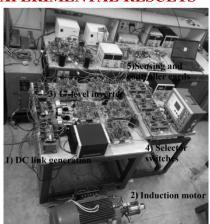

Figure 8. Laboratory prototype forthe 49levelinverter topology. 1) DClink generation, 2) InductionMotor, 3) 17levelinverter, 4) SelectorSwitches, 5) Sensingandcontrollercards.

A symmetric6-stage IM isdriven utilizing the 49-levelinverter topology appeared in Fig. 1 in the wake of designing it as a 3-stage IM. Theinverter iscontrolled utilizing two DSPs (TMS320F28335) and two FPGAs

(Spartan3XCS3200). The research facility model is appeared in Fig. 8. Thetwo **DSPsare** synchronized and theFPGAs conveys gating heartbeats totheMOSFETs. Deadband of 2.5 us is given between all the corresponding sign. The selectorswitches are controlled utilizing DSP-1andFPGA-1. TheDSP-2 alongside FPGA2 controls the 17level inverter. Allthecapacitor voltages andcurrent headings are detected utilizing the ADC module inthisDSP. Contingent upon the detected qualities, advanced sign are conveyed to the FPGAs which select the right exchanging state hid away look into table in FPGA, in view of the contributions from the DSPs. The capacitance esteem, C is chosen by  $C = IpTs/\Delta Vc$ , Ip is the pinnacle loadcurrent,  $\Delta Vc$  is the crest to crest voltage swell and Ts is inverter inspecting time. The trial results are itemized underneath.

#### A. Steady State Results

A isobilateral 6-organize IM is driven victimisation the 49-level electrical converter topology showed up in Fig. one within the wake of structuring it as a 3arrange IM. The electrical converter is controlled victimisation 2 **DSPs** (TMS320F28335) and 2 FPGAs (Spartan three XCS3200). The exploration workplace model is showed up in Fig. 8. the 2 DSPs square measure synchronised and therefore the FPGAs passes on gating pulses to the MOSFETs. Deadband of two.5us obtainable between all the relating hint. The selector switches square measure controlled victimisation DSP-1 and FPGA-1. The DSP-2 obtainable FPGA2 controls the 17electrical converter. capacitance voltages and current headings square measure known victimisation the ADC module during this DSP. Dependent upon the distinguished characteristics, propelled sign square measure passed on to

A Peer Revieved Open Access International Journal

www.ijiemr.org

the FPGAs that choose the privilege commerce state shrouded away investigate table in FPGA, in perspective on the commitments from the DSPs. The strength band obligated all the flying capacitance voltages and therefore the capacitance voltages for the CHBs square measure I Chronicles round the reference regards. The capacitance regard, C is picked by C = IpTs/ $\Delta$ Vc, informatics is that the celestial point load current,  $\Delta Vc$  is that the peak to peak voltage swell and Ts is electrical investigation converter time.The preliminary outcomes square measure separated beneath.

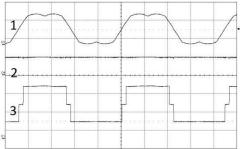

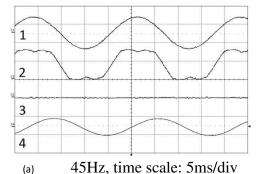

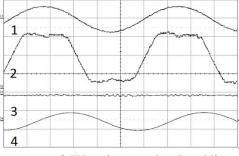

Figure 9. Activity of the selectors witches (Fig. 1) at 45Hz activity.

1) Modulating signal from DAC module of DSP. 2) Constant voltage (VXY) which is equivalent to Vdc/6, 50V/div 3) Polevoltage acquired from the activity of the selector switches (VXN), 50V/div.

#### Timescale: 5ms/div.

It ought to be noticed that the CHB which is most distant from the DC interface (HB-3), hinder the least voltage (Vdc/96). The CHBs (HB-1 and HB-2) closer to the DC connection needs to square marginally however the switchings are less. Therefore the exchanging misfortunes are controlled. It ought to be noticed that the switchings in these CHBs incorporate both for shaft voltage exchanging just as the exchanging for capacitor voltage adjusting. Fig. 11

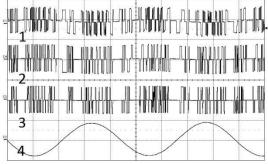

Figure 10. H-bridges (Fig. 1) switching waveformsat 45Hzoperation. 1) V<sub>AS</sub>, 5V/div, 2) V<sub>SQ</sub>, 10V/div, 3) V<sub>QR</sub>, 20V/div. 4) Phase current (I<sub>a</sub>), 5A/div. Timescale: 5ms/div.

demonstrates post voltageat various areas inthe inverter at 45Hz activity. Follow 1 demonstrates the shaft voltage (VRN) which is acquired proportionally because of stackingthreeFCs. Follow 2&3 demonstrates the post voltages at areas (VQN and VSN) which are gotten proportionately because of stackingthree 5-levelinverters and three 9-levelinverters. It ought to benoted from follow 1,2,3that thewaveform is moving toward a 3<sup>rd</sup> symphonious infused sinewave.

#### The outcomes at various

Figure 11. Polevoltages at different locations in the inverter topology (Fig. 1) at 45Hz operation. 1)  $V_{RN}$ , 100V/div, 2) $V_{QN}$ ,100V/div,3) $V_{SN}$ ,100V/div, 4) Phase current ( $I_a$ ), 10A/div. Time scale: 5ms/div.

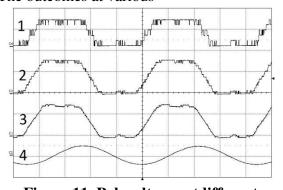

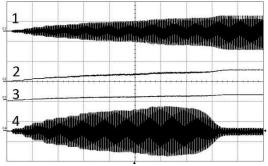

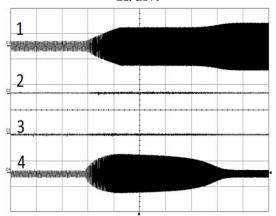

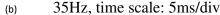

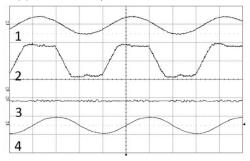

relentless states working frequencies are appeared in Fig. 15(a) to (d). Follow 1 in every one of the above outcomes demonstrates the stage voltage ( $V_{An}$ ). Follow 2 demonstrates the shaft voltage ( $V_{AN}$ ) waveform

A Peer Revieved Open Access International Journal

www.ijiemr.org

alongside the third symphonious infusion. It very well may be seen that the quantity of ventures in the post voltage waveform increments asthe working recurrence is expanded on the grounds that the quantity oflayers in thespacevectorstructure increments as the tweak record orthe working recurrence increments. Follow 3 demonstrates the capacitorvoltage swell whichis firmly controlled inside demonstrates resistanceband. Follow 4 thestagecurrent (I<sub>a</sub>).

Figure 12. 10Hz waveform with adjacent vector switching. 1) Motorphasevoltage  $(V_{An})$ , 50V/div

- 2) Inverterpolevoltage(V<sub>AN</sub>),50V/div,

- 3) Rippleinthecapacitorvoltage ( $\Delta V_{c4}$ ), 2V/div, 4) Phasecurrent( $I_a$ ),10A/div. Timescale:20ms/div.

On the off chance that THD should beimproved furtherat extremely low frequencies, thethree contiguous vector exchanging canbe utilized is appeared in Fig. 12 for 10Hz activity.

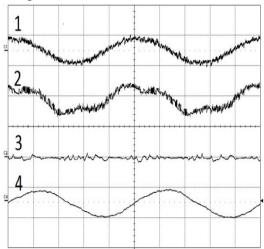

#### **B.** Transient Results

Duringthe engine turning over, thecapacitorvoltages develop with no extra precharging circuit necessity in light of the fact that the capacitor voltage adjusting technique itself guarantees the right changing state to energize the capacitors till they goes in close vicinity to the resilience

band. Fig. 13 demonstrates the equivalent

Figure 13. Capacitorvoltage builds up duringmotorstarting.

- 1) Motorphasevoltage (V<sub>An</sub>), 100V/div

- 2) Capacitorvoltage(V<sub>c2</sub>), 50V/div,

- 3) Capacitorvoltage (V<sub>c3</sub>), 50V/div,

- 4) Phasecurrent (I<sub>a</sub>), 5A/div. Timescale: 1s/div.

Figure 14. Motoracceleration.

- 1) Motorphasevoltage( $V_{An}$ ), 50V/div

- 2) Rippleinthecapacitorvoltage ( $\Delta V_{c3}$ ), 2V/div,

- 3) Rippleinthecapacitorvoltage ( $\Delta V_{c4}$ ), 2V/div,

- 4) Phasecurrent(I<sub>a</sub>),5A/div. Timescale: 1s/div.

Procedure wherethe capacitors energizing totheirset qualities consequently during the engine startup. Fig.14 demonstrates its engine increasing speed waveforms when it quickens from 15hz to noticed existing in the resistance band characterized for them. The over two transient outcomes guarantee thatthe capacitorvoltage adjusting calculation deals with the transient conditions also.

A Peer Revieved Open Access International Journal

www.ijiemr.org

#### IV. CONCLUSION

paper proposes a unique objectives electrical converter for drives applications. the upper variety of voltage levels square measure gotten by stacking inverters with lower variety of voltage levels. Here 3 17-level electrical converters square measure stacked to induce a 49level inverter. The gadget voltageevaluations definitely lessens and henceforth MOSFETs canbe utilized which improvesthe effectiveness of theinverter. Byparalleling minimal effort MOSFETs orby utilizing theSiC put together gadgets withlow Rdswith respect to, the conduction misfortunes can diminished. For getting highernumber of voltagelevels, the quantity of stackingscan be expanded further andthe of quantity fell H-extensions diminished. This will further diminish theindividual DC voltage prerequisite atthe frontend. In this manner the frontend DC source canbe acknowledged utilizing stackedbatteries. In this manner the invertertopology discover broad can applicationsinelectric vehicles. Closest levelcontrol is utilized for exchanging exchanging which further lessens the misfortunes related withthe MOSFETs. The capacitorvoltage adjusting plan utilized, is autonomous ofany tweak file or burden power factor. The topologyis tried fordifferent

(d) 15Hz, timescale: 20ms/div

Figure 15. Enduring state results for V/f activity. 1)MotorStageVoltage (VAn), 100V/div

- 2) InverterShaftVoltage (VAN), (a)-100V/div,(b),(c),(d)50V/div,

- 3) Ripple inthecapacitorvoltage ( $\Delta Vc4$ ), 2V/div, 4)

Stage current (I<sub>a</sub>), 10A/div, stage 'A' for various frequencies of activity. Consistent stateand transientconditions andthe trial results guarantee thatthe proposedtopology is a reasonable alternative for highpower IMdrives.

#### REFERENCES

1. Nabae,I.Takahashi,andH.Akagi,"A new neutral-point-clamped pwm inverter," IEEETransactionsonIndustryApplication s,vol.IA-17,no.5,p.518–523, Sept1981.

A Peer Revieved Open Access International Journal

www.ijiemr.org

- T.A.MeynardandH.Foch, "Multi-level conversion: high voltage choppers and voltage-source inverters," inPower ElectronicsSpecialistConference, 1992. PESC'92Record., 23<sup>rd</sup> Annual IEEE, Jun 1992, pp. 397–403 vol.1.

- 3. P.Barbosa, P.Steimer, J.Steinke, M.Winke Inkemper, and N.Celanovic, "Activeneutral-point-clamped (anpc) multilevel converter technology," in 2005 European Conference on Power Electronics and Applications, Sept 2005, pp. 10 pp. –P. 10.

- 4. M.Malinowski, K.Gopakumar, J.Rodrigu ez, and M.A.Perez, "A survey on cascaded multilevel inverters," IEEETransactions on Industrial Electronics, vol. 57, no. 7, pp. 2197–2206, July 2010.

- 5. M.Saeedifard,P.M.Barbosa,andP.K.Stei mer,"Operation and control of a hybrid seven-level converter," IEEETransactionsonPowerElectronics, vol.27,no.2,pp.652–660, Feb2012.

- P.R.Kumar,R.S.Kaarthik,K Gopakumar, J.I.Leon,andL.G.Franquelo, "Seventeenlevel inverter formed by cascading flying capacitor and floating capacitor hbridges," IEEETransactions on PowerElectronics, vol.30,no.7,pp. 3471– 3478, July2015.

- 7. K.K.Mohapatra,K.Gopakumar,V.T. Somasekhar,andL.Umanand,"A harmonic elimination and suppression scheme for an open-end winding induction motor drive," IEEETransactions onIndustrial Electronicsvol.50,no.6,pp.1187–1198, Dec2003.

- 8. K.Mathew,K.Gopakumar, J.Mathew,N. A.Azeez,A.Dey,andL.Umanand, "Medium voltage drive for induction motors using multilevel octadecagonal voltage space vectors," IEEE

TransactionsonPowerElectronics,vol. 28, no.7,pp.3573–3580,July2013.