A Peer Revieved Open Access International Journal

www.ijiemr.org

#### **COPY RIGHT**

2019IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 4<sup>th</sup> Sept 2019. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-08&issue=ISSUE-09

Title OPTIMIZED SPWM CONTROL METHOD AND ENHANCED POWER-DECOUPLING ABILITY FOR SWITCHED-CAPACITOR-BASED MULTILEVEL INVERTER

Volume 08, Issue 09, Pages: 258-273.

**Paper Authors**

#### SK MYBELLI, N SRIJA, SK SANAHA

Anu Bose Institute of Technology K.S.P Road, New paloncha, Bhadradri Kothagudem, Telangana, India

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic

Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

# OPTIMIZED SPWM CONTROL METHOD AND ENHANCED POWER-DECOUPLING ABILITY FOR SWITCHED-CAPACITOR-BASED MULTILEVEL INVERTER

SK MYBELLI<sup>1</sup>, N SRIJA<sup>2</sup>, SK SANAHA<sup>3</sup>

<sup>1,2,3</sup>Dept. of Electrical and Electronics Engineering, Anu Bose Institute of Technology K.S.P Road, New paloncha, BhadradriKothagudem, Telangana, India.

mybelli.sk@gmail.com<sup>1</sup>,sanahshaik14883@gmail.com<sup>3</sup>

Abstract: -Small scale inverters strolling into the unmarried-installation form from new imperativeness supply with low-voltage yield face the issues of functionality bottleneck and times-line-repeat series. This paper proposed a taken aback inverter reliant on framework remoted traded capacitor (BMSC) circuits with its predominance in exchange adequacy and strength thickness. The topology is made out of DC-DC and DC-AC degrees with selfenough manipulate for every level, looking to improve device adequacy and alter the manipulate method. The BMSC DC-DC mastermind, which may be stretched out to fuse extra degrees, competencies taken aback voltage benefit just as not completely replaces the principle mass facts capacitor and boundaries as a working essentialness pad to beautify energy decoupling restrict among DC and AC aspects. In DC-AC kind out, the manipulate technique of reducing aspect unipolar repeat multi managing sine-wave beat width exchange (UFD-SPWM) is proposed to enhance the concept of yield waveform. in the period inbetween, the surprised voltage diploma has been progressed to decrease the impact incident further. subsequently, a version has been advanced and attempted. associated with the reenactment, the exploratory consequences suggest the practicability of these examinations. **Index Terms:** Switched-capacitor circuit, staggered inverter, manipulate decoupling, superior unipolar recurrence multiplying SPWM.

#### **I.INTRODUCTION**

In reasonable vitality source age structure (REGS), the low voltage made by utilizing the PV or essentialness gadgets should be maintained to a passably pick need DC transport voltage sooner than making it to AC conveyance for gadget affiliation [1]-[3]. A thermoelectric generator, a battery, and a ultra-capacitor are typical instances of such low-voltage DC importance assets in addition. evaluation article [4] affirmed some top notch understanding on the

converter topology for least dissipated age (DG) inverters. starting late, stand-out converter topologies for the power trade from low-voltage DC to high-voltage AC for matrix affiliation have been spoken to supervise express issues, as an example, sufficiency, value, and success symphonious. All issues considered speakme, there are styles of topology plans for REGS, for example, single-degree and bearing organize. it's miles practical to

A Peer Revieved Open Access International Journal

www.ijiemr.org

blend a DC-DC reinforce exchange and DC-AC trade in one phase to capture voltage raise and reversal [5]-[6]. Indeed, even that relative less parts are required, it's far hard to increase high voltage gain. some other typical technique requires a lift converter as the front-end form and an inverter as the returned-end plan the gadget affiliation. In light of detached control for every degree, high return waveform acceptable might be generally perfect to get. in the period in the middle of, it is down to earth for wide assortment enter voltage by means of of inordinate development prudence insistence [7]-[8]. beginning at now, incredible raise circuits inside the front-a couple of bit of the arrangement have been significantly asked roughly. To maintain a strategic distance from wellknown convey converter downsides underneath inordinate development, similar to crazy responsibility cycle, high voltage/advanced weight and overwhelming recuperation shortage, zsource, coupled-inductor or traded capacitor net-work are familiar into raise circuits with realization DC-DC exchange [9] [10]. especially for exchanged capacitor converter, they have changed over into a hot contender in perspective on alluring less segments, high reasonability and quality thickness [11]-[12]. In like way, exchanged capacitor converter may be broadened voltage increase through creating exchanged capacitor evaluated [12]-[14]. regardless, canvases of goliath switches and bottleneck of wave best achieve course engineer REGS a couple of horrible. With the movement of astonished advancement, astounded structure related inside the front-a couple of part of the course of activity been proposed [15] [16]. In [17], 3-degree hoist circuit is inside the front stop to help the vehicle voltage and diode-got fivelevel inverter orchestrates inside the again surrender. To

control the voltage course of of development capacitors, two more prominent changing over circuits are utilized, which make the shape expensive and bulkily. In [18], exchanged capacitor anticipated with four switches and one capacitor is about in the front of extreme recurrent assistant DC-AC converter to yield three voltage stages, other than it calls for helper circuit to control the capacitor voltage with now not as a great deal as twice voltage advantage. In works [19][20], two-organize sevenlevel inverter proposed, where an exchanged capacitor astounded circuit could yield four voltage ranges: zero, Vin, 2Vin and 3Vin. It has central focuses in term of switches number and voltage strain separated and regular astounded converter, however a fanciful oversee approach is required to change the capacitor voltage at some phase in voltage level headway. Separated and converter in [19][20], converters showed in [21][22] have adaptable voltage degree improvement and voltage development might be raise comparatively with the exchanged capacitor module expanding, the need lies in more noteworthy area's need underneath a tantamount voltage degree yield. one of the inconveniences respected by course make little scale inverter is the need to cushion the multiple times-line-rehash centrality. unprecedented vitality decoupling systems have been utilized to deal with the twiceline-rehash centrality trouble. exceptionally essential stage, it could be analyzed three sorts of power decoupling system: PV-viewpoint decoupling, DCbuddy decoupling and ACside decoupling. For PV-side decoupling approach, addressing the decoupling capacitor direct transversely over on the PV yield terminal will be the lovely decision from a benefit point of view. in any case, the required

A Peer Revieved Open Access International Journal

www.ijiemr.org

capacitance might be especially remarkable, which fundamentally gathers the expense, reduces the power thickness and truncates the lifetime [23] [24]. as to alliance framework, decoupling essential. expense is low in light of the way that no additional circuit is regular, prompting conventionally high ampleness also. in any case, inconspicuous control system should be utilized to consider higher voltage swell and to hold up the low present THD embedded to the shape [25]. In AC-aspect decoupling system, the capacitance might be little a quick aftereffect of the high voltage swing. regardless, another degree leg is incorporated, with the goal that it will accumulate the expense [26] [27]. There are a few change systems to drive a paralyzed the space inverter: substitute vector (SVPWM) [28][29], the particular symphonious stop (SHEPWM)[30] [31], and the multicarrier SPWM, for example, the then again plan inconvenience disposition(APOD)PWM[30][32]. SHEPWM, the goal is a piece of the great symphonious, purchase even significant thing consonant must be happy. On the off chance that this objective can't be gotten, the most tremendous practical consonant streamlining is needed. dealing with SHEPWM non-liner conditions is a basic issue in getting purchasing and selling centers. In SVPWM, relative over the top voltage use and intermittent yield cutting edge swell can be won, yet is directly for three-set up inverter with low levels yield. In APODPWM, it puts progressively consonant centrality into triple sideband symphonious that drops on a line-to-line premise. regardless, the end symphonious augmentations and it has triple sideband consonant losing just in 3-set up inverter. This paper acclimates another trade system with region the as much as referenced

issues, the fresh out of the box new structure gives exchanged capacitor improvement and oversee arrangement of streamlined unipolar continue expanding SPWM (UFD-SPWM), while it permits exceedingly inordinate ability and espresso yield voltage THD. The proposed converter structuring wires an assortment expected exchanged capacitor (BMSC) with extraordinarily astounded growth and Hstage to get weight of the over the top proficiency amazed inverter movement run, things considered improving usefulness H-interface of converter coordinate. The BMSC circuit also limit of the way replaces the chief mass information capacitor and gives the multiple times-linerehash significance buffering among DC and AC sides. The token of this paper is taken care of as looks for after. The proposed converter and development well known is depicted in segment II. the perfect structure of level parameters and power decoupling assessment are appeared in area III. Section IV gives the delight and test outcomes and seeking with proclaimed converters. at last, closes are recorded in area V.

### II.THE PROPOSED CONVERTER AND OPERATION PRINCIPLE

#### **A.Topology Description**

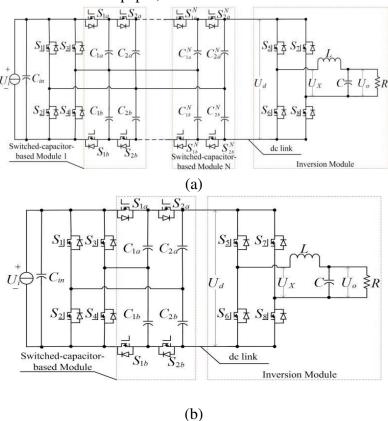

the general topology of amplification limited exchanged capacitor fundamentally based extraordinarily shocked inverter is in Fig.1(a). proposed appeared The capacitor converter joins exchanged module, as appeared in left and awareness dashed edges, and H-accomplice module, as appeared inside the favorable position dashed zone. it will collect four levels for yield voltage with each exchanged capacitor interesting secured. DC-DC adventure up exchange is cultivated inside the exchanged capacitor module, the pivotal topology

A Peer Revieved Open Access International Journal

www.ijiemr.org

portrayal of that is spoken to in [33]. DC-AC trade is analyzed dependent on Hbridge. change extents are impartial movement with decoupling control. inside the paper, a

seven-level inverter with one exchanged capacitor one of a kind, as appeared in Fig.1(b), is done for test and test.

Fig.1 Topology of the proposed converter. (a) General topology of bridge modular switched-capacitor-based multilevel inverter. (b) Seven-level inverter

**B.**Operation of reversal module with best control

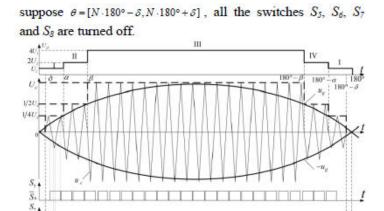

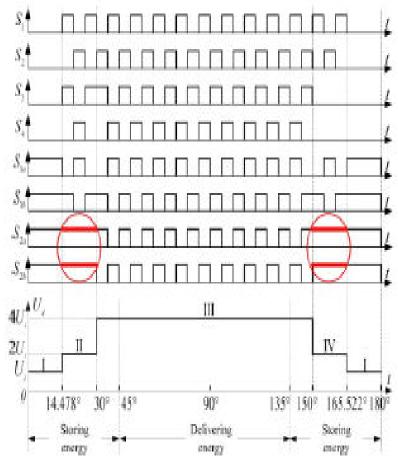

considering the unfastened manage for inversion degree and voltage got here upon DC-interface, SPWM with best a solitary transporter, which requires clean figuring, is the nice hazard for equalization method. Differentiated and one of a kind SPWM methods, unipolar repeat duplicating SPWM (UFD-SPWM) suggests robust symphonious camouflage and suits comparable shopping for and promoting repeat without developing shopping for and selling incident. To enlarge chief element in the movement wave, the control device for **UFD-SPWM** with diploma progression is used for inversion

unique, as regarded in Fig.four. The bitriangle transporter wave uc with 3 one-ofa-type voltage stages (1/4Uc, 1/2Uc, Uc) appears at to the adjusted sine wave ug with inverse polarities (ug and - ug) to create driving sign for switchesS5~S8.To make sure constrained replacing misfortune and accomplish higher have an effect on factor, DC be a part of current identification have to approach zero at 0 intersection of the street voltage .anyhow, because of proper right down to earth steady hobby for exchanged capacitor module, it's miles difficult to preserve identification=zero. Henceforth, a deadangle  $\delta$  of some degree is needed to set previously or after the 0-

A Peer Revieved Open Access International Journal

zero.1. 2.

www.ijiemr.org

intersections of the road recurrence. At N

Fig. 4 The waveforms of optimized UFD-SPWM control method.

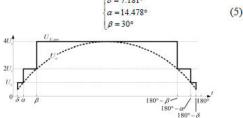

As seemed in desk I, the itemized hobby of switches S5~S8 in reversal unique is portrayed. exclusive with general unipolar recurrence multiplying SPWM, the bearer wave uc in proposed UFD-SPWM has 3 throughout numerous interims of tweak wave ug, whose level enhancement might be mentioned in subsequent segment. every time uc signal for S5 and S6 are uncommon united states of america and low degree, for my part, and conversely at uc>ug. on the factor whilst uc<-ug, driving signal for S7 and S8 are unusual nation and occasional degree, one after the other, and irrespective of what is probably anticipated whilst uc>-ug. At top notch half of of cycle, UX is managed by using manner of driving signal purpose of switches S5 and S8. Have the proper to be referenced, switches S6 and S7 will in no way be have become-on at the same time in mild of the reality that the peculiar country for using signal of S5 is in each case longer than the low degree for the usage of sign of S7. At each mode, it will yield degrees but: (zero, Ui) for mode I, (0, 2Ui) for modes II 4Ui) for and IV, (0,modes subsequently, high nice voltage degrees (Ui,

2Ui, 4Ui) and zero level are yielded for UX at some point of fantastic half of of cycle. similarly, UX has bad voltage tiers (- Ui, - 2Ui, - 4Ui) and zero diploma within the path of terrible half of cycle. when you consider that there are two degrees changing however for yield voltage at some point of each changing duration, the recurrence of yield stages copies the replacing recurrence. below the stability approach, the yield waveforms at channel the front-stop and lower again-stop are regarded in Fig.5.

In view of referenced exam, it may be reasoned that, under the proposed manipulate method, changing misfortune might be diminished similarly to the yield voltage symphonious may be chopped down due to the increasing voltage degrees and multiplying proportionate changing recurrence.

Table I: Switches Operation Under Optimized Ufd-Spwm Method

|                                                                                                        | Posi                                            | ive half  | cycle        |     |       |                                                         |

|--------------------------------------------------------------------------------------------------------|-------------------------------------------------|-----------|--------------|-----|-------|---------------------------------------------------------|

|                                                                                                        |                                                 | $S_5$     | $S_{\delta}$ | S7  | $S_8$ | $U_X$                                                   |

| $u_{c>}u_{g}$                                                                                          |                                                 | OFF       | ON           | OFF | ON    | 0                                                       |

| $\begin{array}{c} 1/4U \geq u \geq -1/4Uc \\ 1/2U \geq u \geq -1/2Uc \\ U \geq u \geq -Uc \end{array}$ | u <sub>g</sub> ≥u≥-u <sub>g</sub>               | ON        | OFF          | OFF | ON    | $U_i$<br>$2U_i$<br>$4U_i$                               |

| $u_c < u_g$                                                                                            |                                                 | ON        | OFF          | ON  | OFF   | 0                                                       |

|                                                                                                        | Nega                                            | tive half | cycle        |     |       |                                                         |

| $u_c > u_g$                                                                                            |                                                 | ON        | OFF          | ON  | OFF   | 0                                                       |

| $1/4U_c \ge u_c \ge -1/4Uc$<br>$1/2U_c \ge u_c \ge -1/2Uc$<br>$U_c \ge u_c \ge -Uc$                    | -u <sub>g</sub> ≥u <sub>c</sub> ≥u <sub>g</sub> | OFF       | ON           | ON  | OFF   | -U <sub>i</sub><br>-2U <sub>i</sub><br>-4U <sub>i</sub> |

| $u_c < u_g$                                                                                            |                                                 | OFF       | ON           | OFF | ON    | 0                                                       |

A Peer Revieved Open Access International Journal

www.ijiemr.org

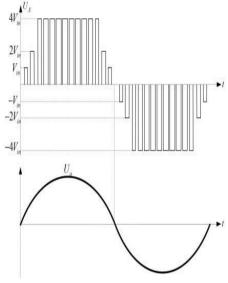

Fig. 5 Output waveform of inversion module.

## III. OPTIMAL DESIGN OF PHASE PARAMETERS AND DECOUPLING ANALYSIS

#### A. Optimal Design of Phase Parameters

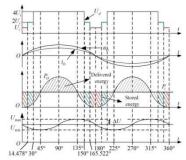

To restrict the voltage alternate scope of reversal and reduce the electricity misfortune, Ud must be ventured with the street voltage as regarded in Fig.6. considering maximum excessive estimation of 4Ui for yield voltage Uo, it is anticipated that Uo =4 Ui - sinø.

Then, UX, evp is predicted due to the fact the wrap of immoderate recurrence yield voltage beat UX, that is same to Ud. As identified

from Fig.6, with the aid of manner of making Uo =UX env, at  $\emptyset = \alpha$ ,  $\emptyset = \beta$ , the difference amongst UX,evp and Uo can arrive at minimization esteem, It yields:

$$U_o(\alpha) = 4U_i \cdot \sin \alpha = U_i$$

(1)

$$U_{\rho}(\beta) = 4U_i \cdot \sin \beta = 2U_i$$

(2)

C. The standardized difference amongst UX, env and Uo, which need to be restrained, is probably measured as  $\Box$ (UX env $\Box$ Uo)  $\Box$  Uo

As appeared in Fig.6, it's miles whatever but difficult to establish that the limit of this standardized difference just takes place at one of the accompanying line elements:  $\emptyset = \delta, \emptyset = \alpha, \ \emptyset = \beta$  as a result, the development target okay to be restrained may be communicated as:

$$k = \max \begin{bmatrix} \frac{U_i - 4U_i \cdot \sin \delta}{4U_i \cdot \sin \delta}, \frac{2U_i - 4U_i \cdot \sin \alpha}{4U_i \cdot \sin \delta}, \\ \frac{4U_i - 4U_i \cdot \sin \beta}{4U_i \cdot \sin \beta} \end{bmatrix}$$

(3)

Submit formulas (1) and (2) to formula (3), it yields:

$$k = \max \left[ \frac{U_i - 4U_i \cdot \sin \delta}{4U_i \cdot \sin \delta}, 1, 1 \right]$$

(4)

From formula (4), it can be concluded that when  $U_i - 4U_i \cdot \sin \delta = 1$ , the voltage difference comes to the minimum  $4U_i \cdot \sin \delta$

ralue. And the results can be calculated out:

Fig. 6 Output Waveforms of inverter module with dead zone.

#### B.energyDecoupling evaluation

In a gird-linked unmarried-inverter, the injected contemporary to the grid io(t) and the grid voltage uo(t) are given by using

$$\begin{cases} u_o(t) = U_o \sin(\omega_o t) \\ i_o(t) = I_o \sin(\omega_o t + \varphi) \end{cases}$$

(6)

in which,  $\omega$ o is the matrix recurrence, Uo and Io are the amplitudes of the community voltage and modern-day, in my opinion.  $\phi$  is level flow into among the infused modern-day and the lattice voltage, it really is appealing to be 0 for crew spirit power issue. on the point whilst level flow into  $\phi$  is 0, the on the spot yield control Po(t) is yielded as pursues:

$$P_o(t) = \frac{1}{2}U_oI_o + \frac{1}{2}U_oI_o\cos(2\omega_o t)$$

(7)

A Peer Revieved Open Access International Journal

www.ijiemr.org

The yield brief electricity in (7) comprises of terms: the normal yield manage 1/2UoIo, and the throbbing pressure 1/2UoIo•cos(2ωot), which sways at double the road recurrence. in any case, the electricity from the DG supply (like PV measured, thermoelectric particular and so on.) should be managed to be everyday as feasible for optimum extreme energy factor music (MPPT). looking forward to a lossless inverter arrange, the strength created through the usage of the DG secluded equivalents to the regular yield control, as show in Fig.7. To hold up power balance, the throbbing pressure, Poac=Po-Pi, for the most factor is sorted with the resource of "decoupling capacitor".

it's miles anticipated that the converter is manage lossless, as indicated through power protection law, the electricity placed away in the proportionate DC interface capacitor Cd may be communicated as a issue of capacitor voltage UCd at a few random time with a sinusoidal shape superimposed on a DC counterbalance. As indicated by way of the use of the vitality balance famous, the power charged or launched from the capacitor Cd can be decided coordinating considered certainly one of shadowed as regarded in Fig.7. In view of ideal plan of degree parameters in segment A, modes I, II, IV and halfway III will enjoy setting away vitality manner and the rest mode reviews conveying IIIpower approach.

$$E_{Cd} = \int_{0}^{\frac{\pi}{2\omega_{0}}} (P_{i} - P_{o}(t)) dt = \frac{1}{2} C_{d} (U_{Cd_{\max}} - U_{Cd_{\min}})$$

(8)

in which, UCd\_max and UCd\_min are the greatest and least voltage over the decoupling capacitor. The incorporation interim  $[0 \pi/2\omega o]$  recommends half energy swaying length for conveyed power or located away vitality, the voltage crosswise over Cd will reap as much as best incentive

from least nicely well worth or reach right down to least an incentive from most severe sincerely worth.

Brushing recipes (7) and (8), the required decoupling capacitance may be given as:

$$C = \frac{P_i}{\omega_O U_{Cd} \Delta U_{Cd}}$$

(9)

Where,  $U_{Cd}$  is the average DC voltage across  $C_d$ , and  $U_{Cd}$  is the voltage ripple across  $C_d$ .

Fig.7 Total power processed by the decoupling capacitor.

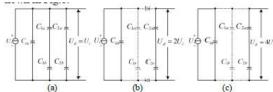

inside the proposed converter, the low-recurrence manage throb is changed over into the voltage throb on DC interface proportional capacitor Cd, which fills in as fractional decoupling capacitor and can be determined out as in step with Fig.3, to such an volume that the voltage over the information capacitor Cin is stored everyday as could be allowed and its capacitance can be reduced to a normally littler nicely really worth. it's miles anticipated that capacitors C1a ~ C2a have a similar capacitance C, the equal decoupling capacitor at various hobby modes for exchanged capacitor module is seemed in Fig.8.

Fig.8 Equivalent decoupling capacitor: (a) $C_{dec}$ =  $C_{in}$ +C. (b)  $C_{dec}$ = 0.5C. (c)  $C_{dec}$ = 0.5C.

A Peer Revieved Open Access International Journal

www.ijiemr.org

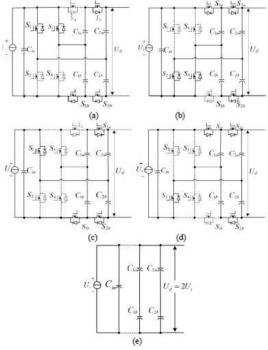

on every occasion Ud=Ui, the DC connect same capacitor Cd may be considered as capacitors C1 and C2connected in parallel, and Cd=C. for this reason, at this specific, the decoupling capacitor Cdecis equal to Cin+C, as regarded in Fig. 8(a). In Fig. 8(b), the charging contemporary is hindered with the aid of the switch diodes of S2a and S2b, in this way Cd is similar to C2a and C2b related association. and Cd=Cdec=zero.5C. every time Ud=4Ui, Cd is proportional to C2a and C2bconnected in affiliation, and Cdec= 0.5C additionally. thinking about various levels at diverse modes, as appeared in Fig.7, the DC interface capacitor will ingest manage from records aspect even as Ud ventures into 2Ui from Ui, but keep manipulate from reversal aspect while Ud ventures into 2Ui from 4Ui. accordingly, if a manner is given precisely

when the energy streams again, the electricity decoupling capacity may be advanced. In mild of increasing equal DC interface capacitance, an progressed control technique is proposed, as seemed in Fig.nine. As needs be, the modes II and IV are progressed as Fig.10(a), Fig.10(b), Fig.10(c) and Fig.10(d), in my opinion. below the progressed manage method, switches S2a and S2b are stored on at the same time as Ud=2Ui. With the improved manipulate technique, changing misfortunes is exceedingly faded, and capacitance estimation of Cd will increment because of capacitors spans (join 1 with C1a, C1a and scaffold 2 with C2a, C2b) associated in parallel. consequently, Cdec=C, as seemed in Fig.10(e).

Fig. 9 Improved control strategy of the proposed converter.

A Peer Revieved Open Access International Journal

www.ijiemr.org

Fig. 10 Operation modes under improved control: (a) Sub-circuit 1 at Mode II. (b) Sub-circuit 2 at Mode II. (c) Sub-circuit 1 at Mode IV. (d) Sub-circuit 2 at Mode IV. (e) Equivalent decoupling capacitor: $C_{dec} = C$ , when  $U_d = 2U_i$ .

The discussion of power decoupling operation results in the following effects:

1. For a micro-inverter with a given power rating and line frequency, the size of the required decoupling capacitance is determined by the DC voltage maximum allowable voltage ripple. As the capacitor voltage U<sub>Cd</sub> is much higher than the input voltage Ui, energy transferring would occur when the voltage fluctuation on C<sub>d</sub> is increased. The DC input energy is stored in equivalent DC link capacitor C<sub>d</sub> and the output energy is supplied from the same capacitor. Consequently, the lowfrequency power pulsation caused by the inversion modular is transferred into capacitor C<sub>d</sub>, and the voltage on input capacitor Cin, which is same as that of DG module, is kept constant. Therefore, capacitance value of Cin can be minimized without increasing the ripple voltage on DC

input and a large electrolytic capacitor can be substituted with a film capacitor.

### IV.SIMULATION ANDEXPERIMENTAL RESULTS

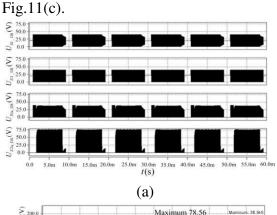

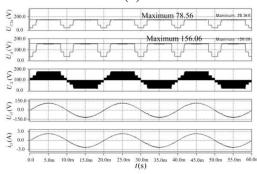

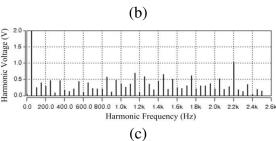

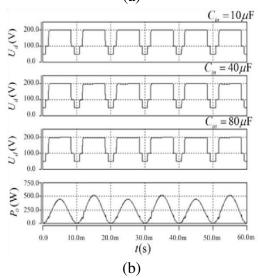

reenactment parameters consistent with the subsequent: input voltage Ui=40V, changing recurrence DC-AC fs=15kHz for transformation secluded and fs=50kHz for DC-DC change specific, line recurrence capacitors fl=50Hz, C1a=C1b=C2a=C2b=40µF, tweak record M=zero.8, yield load Ro=50ω, channel inductor Lf=2.5mH, channel capacitor Cf=three.threeµF. it's far seen that replacing recurrence fs will increment to 50KHz all through mode development to defeat the triumphing spike. within the mean time, because of competition dispersed in wire, ON-switches, capacitor and circulate/stray inductance, the prevailing spike could be confined in some diploma. The run of the mill activity results are appeared in Fig.11. The voltage fear of switches US1\_DS,US3\_DS, US1a\_DS and US2a DS are regarded in Fig.11(a), it's miles some thing but tough to presume that the voltage worry of switches S1-S4, S1a and S1b equivalents to Ui, and the voltage fear of switches S2a and S2b equivalents to 2Ui. The voltages crosswise over capacitor C2a and the yield of exchanged capacitor module are appeared in Fig.11(b), wherein the 3 voltage ranges (Ui, 2Ui, 4Ui) are gotten for Ud. Likewise, the yield voltage of reversal module UX, yield voltage Uo and yield cutting-edge Io of the inverter via the LC channel are regarded in Fig.eleven(b). At ultimate, the range of yield voltage Uo with absolutely the consonant mutilation (THD) of 3.40 three% is regarded in

A Peer Revieved Open Access International Journal

www.ijiemr.org

Fig.11 Simulation waveforms of seven-level inverter.(a)  $U_{s1\_DS}$ ,  $U_{s3\_DS}$ ,  $U_{s1a\_DS}$  and  $U_{s2a\_DS}$ . (b)  $U_{C2a}$ ,  $U_d$ ,  $U_X$ ,  $U_o$  and  $i_o$ . (c) Spectrum of  $U_o$ .

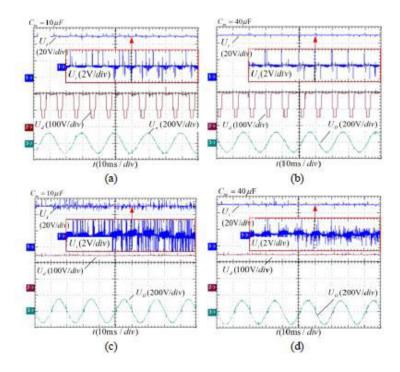

Fig.11 Simulation waveforms of sevendegree inverter.(a) Us1\_DS, Us3\_DS, Us1a\_DS and Us2a\_DS. (b) UC2a, Ud, UX, Uo and io. (c) Spectrum of Uo. To test the upgraded exhibition of depth decoupling for the proposed converter, a normal control technique dependent on a similar version is utilized to approve in replica and exam. in this manner, it without a doubt works with a comparable maximum incentive for parameters however input voltage ascends to 50V for a persuading confirmation. beneath this system, exchanged capacitor measured is labored as mode III to get multiple times voltage gain and ordinary

unipolar recurrence multiplying SPWM manipulate method is applied for reversal precise. Fig.12(a) and Fig.12(b) display the information voltage Ui and the yield voltage exchanged capacitor underneath proposed manage methodology, individually. For examination, Fig.12(c) and Fig.12 (d) deliver out the info voltage Ui and the exchanged capacitor yield voltage Ud under conventional manage method. bigger statistics capacitance properly well worth must enhance the power decoupling capability underneath proposed manipulate technique clearly as normal control device. Be that as it can, absolutely the voltage swell could be stifled below the proposed manage technique contrasted and traditional manage technique.

A Peer Revieved Open Access International Journal

www.ijiemr.org

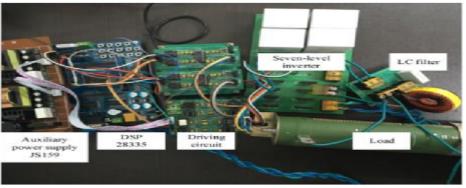

Fig.12 Simulation correlation of intensity decoupling potential at numerous Cin.under proposed manage method:(a)Ui and Po. (b)Ud and Po.below standard control approach:(c) Ui and Po. (d) Ud and Po. same because the reenactment parameters, a seven-level inverter model is labored in Fig.13. IRFP260N and IXTK62N25 are carried out for switches S1-S4, S1a-S2b and

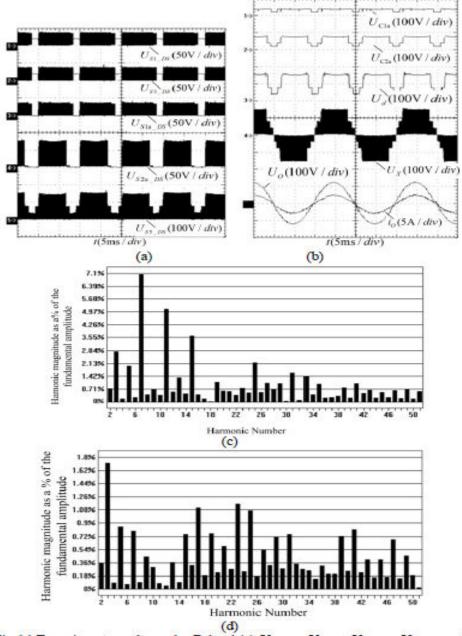

switches S5-S8, personally. SHB-500-forty is used as capacitors. The exploratory effects underneath resistive burden are appeared in Fig.14. The voltage fear of the switches is seemed in Fig.14(a), which is of the same opinion well with the theoretic investigation and the reenactment results. additionally, Fig.14(b) plots the voltage crosswise over capacitors C1a and C2a, the yield voltage of exchanged capacitor module Ud, the yield voltage of reversal module UX, and the inverter yield voltage/contemporary-day Uo/io. Fig.14(b), UC1a has two levels of 20V and 40V, and UC2a possesses 3 tiers of 20V, 40V and 80V. The yield voltage Ud pairs UC2a with three degrees of 40V, 80V and 160V, this is as constant with the theoretic examination consequences. UX, at the channel the front-give up, gets seven voltage ranges of ±160V, ±80V, ±40V and 0V thru reversal hobby. The levels of yield voltage at channel the front-give up UX and lower again-give up Uo are appeared in Fig.14(c) and Fig.14(d), one after the opposite. The THD of UXamounts to 11.207% and Uo is ready three.865% after LC sifting. Given LC parameter advancement, the lower THD can be completed overU<sub>0</sub>.

Fig.13 Prototype of the proposed converter

A Peer Revieved Open Access International Journal

www.ijiemr.org

Fig.14 Experiment results under R-load.(a)  $U_{s1\_DS}$ ,  $U_{s3\_DS}$ ,  $U_{S1a\_DS}$ ,  $U_{s2a\_DS}$  and  $U_{s5\_DS}$ .(b)  $U_{C1a}$ ,  $U_{C2a}$ ,  $U_d$ ,  $U_X$ ,  $U_o$  and  $i_O$ . (c) Spectrum of  $U_X$ . (d) Spectrum of  $U_o$ .

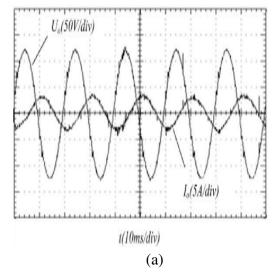

The take a look at waveforms beneath RL-load with resistor of  $50\omega$  and inductor of 20mH is regarded in Fig.15. it's far seen that the THD of yield voltage is about three.614%, drawing nearer to the THD underneath R-load. therefore, the proposed inverter may additionally need to artwork basically at RL-load, which makes it capability in impartial or matrix related applications.

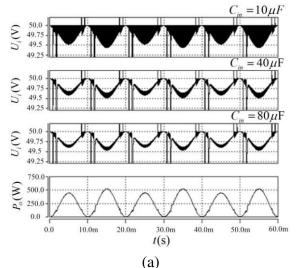

The test waveforms of Ui, Ud and Uo with various Cin to approve strength decoupling functionality are seemed in Fig.sixteen. it's miles seen that the information voltage is prolonged to 50V from 40V. The consequences advise that the voltage swell crosswise over facts deliver might be altogether faded with Cin of 10µF without a doubt as fortyµF even as the proposed converter is labored below proposed control device. Henceforth, the give up that

A Peer Revieved Open Access International Journal

www.ijiemr.org

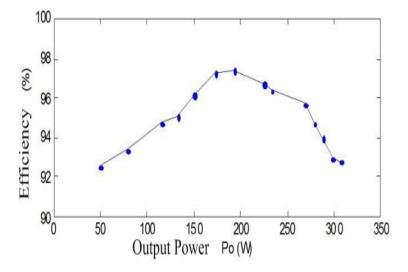

converter is certified proposed upgraded power decoupling capacity can be inferred.maintaining parameters same to reenactment, the converter works with converting burden R (163ω to twenty-fiveω) to accumulate numerous yield electricity degree (50W to 310W) below open circle manage. The expertise bend is predicted depending on energy Analyzer PA310, as plotted in Fig.17. It indicates excessive effectiveness of over 90 % at complete-load variety and top proficiency is going as a good deal as ninety seven.6% for the converter.The proposed exhaustive correlation with extraordinary awesome topologies has been made and regarded in table II, in which N is an uncommon quantity speaking to yield voltage tiers. each one of the converters certain in [19][20][21] and proposed converter have power transformation stages: switchedcapacitor assist converter for DC-DC and H-join inverter for DC-AC. Converters in [19] and [20] share a comparable topology with numerous balance strategies. Being higher than the converters in [19][20][21], the proposed converter possesses benefit in decreasing twice-line-recurrence Contrasted and converters in [19][20], the proposed converter broadens its yield ranges advantageously via the use of increasing exchanged capacitor measured. in the mean time, it highlights better talent even at decrease changing recurrence of 15KHz (reversal measured), lower THD of yield voltage at channel front-give up and better voltage growth under a comparable yield stages. All things taken into consideration, the THD of yield voltage at channel lower lower back-quit will be decreased further via advancement of channel shape parameters, so that you can be pointed out in future work. In [21], even that the converter could develop its yield degrees

due to the fact the proposed converter too, its gift manner reports more electricity device bringing approximately moreover changing and conduction misfortune, which has been well-known by the report of top effectiveness underneath a similar have an effect on rating of 300W. better voltage advantage at identical yield ranges is a few different extensive favored position for the proposed converter additionally contrasted with the converter in [21]. As far as stability technique, UFD-SPWM indicates rate of effective most single transporter prerequisite, which diminishes manipulate multifaceted nature. principally, super with the located converters, the proposed converter might be controlled autonomously for two falling additives, figuring out better soundness unwavering first-class. Be that as it may, the proposed converter need to make use of more than one regularly dynamic switches beneath event of low yield stages. at the thing while N is going as plenty as eleven, the usage range of dynamic switches in proposed converter remains more than converter in [21] but now not as a terrific deal as converter in [19][20]. In truth, if thinking about diode necessity, converter in [21] takes up the maximum system some of the looked at converters.

A Peer Revieved Open Access International Journal

(b)

www.ijiemr.org

Fig.15 Experiment waveforms under R-L load:  $R_o$ =50 $\Omega$ ,  $L_o$ =20mH.(a)  $U_o$  and  $i_O$ .(b) Spectrum of  $U_o$ .

Fig.16 Experiment waveforms of  $U_i$ ,  $U_d$  and  $U_o$  with different  $C_{in}$ . Under proposed control strategy:(a) with  $C_{in}$  of  $10\mu F$ . (b) with  $C_{in}$  of  $40\mu F$ . Under compared control strategy:(c) with  $C_{in}$  of  $10\mu F$ . (d) with  $C_{in}$  of  $40\mu F$ .

Fig.17 Measured efficiency curve.

A Peer Revieved Open Access International Journal

www.ijiemr.org

| COMPRESIE                                    | [19]                                       | WEEN THE PROPOSED CON<br>[20]              | [21]                                      | Prototype                      |

|----------------------------------------------|--------------------------------------------|--------------------------------------------|-------------------------------------------|--------------------------------|

| Topology                                     | DC-DC-AC                                   | DC-DC-AC                                   | DC-DC-AC                                  | DC-DC-AC                       |

| Modulation method                            | Multicarrier<br>LS/LPS-SPWM                | Multicarrier<br>LS-SPWM                    | Multicarrier<br>LS-SPWM/SHE               | Optimized UFD-SPWM             |

| Independent control                          | No                                         | No                                         | No                                        | Yes                            |

| Rated power(W)                               | 3.13/3.27                                  | 5.76                                       | 300                                       | 300                            |

| Input voltage(V)                             | 8                                          | 8                                          | 36                                        | 20                             |

| Switching frequency(KHz)                     | 40/20                                      | 40                                         | 40                                        | 15                             |

| Line frequency(KHz)                          | 0.05                                       | 1                                          | 0.4                                       | 0.05                           |

| PK: peak efficiency                          | 94.9%/95.4                                 | 84.9%                                      | 89.2%/91.6%                               | 97.6%                          |

| Power factor                                 | R-load                                     | R-load                                     | R-load                                    | R-load                         |

| THD of output vol.<br>at filter back-end     | 1.7%/1.4%                                  |                                            | Without LC filter                         | 3.865%                         |

| THD of output vol.<br>at filter front-end    | 11.7%/5.13%                                | 19.5%                                      | 5                                         | 11.2%                          |

| Twice-line-frequency<br>variations reduction | *                                          | *                                          | <b>8</b> 2                                | Yes                            |

| Levels                                       | 7/N                                        | 7/N                                        | 11/7/N                                    | 7/N                            |

| Num. of device                               | 10/0.5*(3N-1) switches<br>4/0.5*(N-1) Cap. | 10/0.5*(3N-1) switches<br>4/0.5*(N-1) Cap. | 9/7/0.5*(N+7)Switches<br>8 /4/(N-3)Diodes | 12/N+5 Switches<br>4 /N-3 Cap. |

|                                              |                                            |                                            |                                           |                                |

3/0.5\*(N-1)

6/N-1

TABLEII

#### **V.CONCLUSION**

Vol. gain Num. of carrier

A platform envisioned traded capacitorprimarily based amazed inverter with slicing vicinity UFD-SPWM manage method is proposed in the paper. The traded capacitorbased absolutely level can comfy immoderate change overall performance and various voltage ranges. Then, it fills in as a running essentialness pad, overhauling the strength decoupling limit and conducing to reduce the complete length of the two timesline imperativeness buffering capacitance. also, voltage lurched in DC-interface decreases the shopping for and selling lack of inversion arrange in moderate of the truth that turn-off voltage stress of switches adjustments with time of yield voltage instead of reliably encounters one with the useful resource of and large high DC voltage. especially, the manipulate device for UFD-SPWM, duplicating same witching repeat, is used inside the inversion type out for a bewildering yield waveform with diminished consonant. moreover, advanced voltage degree degree expands the key component in yield voltage pulses to decrease consonant flip round as might be normal in light of the modern-day-day scenario. Hereafter, the full shape capability

3/0.5\*(N-1)

has been raised and as a great deal as top estimation of 90 seven.6%. ultimately, alternate levels are managed openly for propelling trustworthiness and decreasing multifaceted nature. In future paintings, bare vital mishap communicate, tallying theoretic figuring and endorsement of adversity breakdown, is probably presented.

4/N-3

4 /2/0.5\*(N-3)capacitors

5/3/0.5\*(N-1)

#### REFERENCE

- 1. M. Jun, "every other unique circle predisposition mapping degree mindset PWM with dynamic voltage balance capacity for secluded staggered converter," IEEE Trans. Ind. Electron., vol. sixty one, no. 2, pp. 798-807, Feb.

- 1. **2. 2014.**N. Mehdi, and G. Moschopoulos, "A novel single-stage multilevel type full-bridge converter," IEEE Trans. Ind. Electron., vol. 60, no. 1, pp.

- 2. 2. 31-forty two, Jan. 2013.

- 3. three. E. Ehsan and N. B. Mariun, "check consequences of forty seven-degree switchladder staggered inverter," IEEE Trans. Ind. Electron., vol. 60, no. eleven, pp. 4960-4967, Nov. 2013.

- 4. 4. J. Lai, "power molding circuit topologies," IEEE Trans. Ind. Electron., vol. 3, no. 2, pp. 24-34, Jun. 2009.

A Peer Revieved Open Access International Journal

www.ijiemr.org

- 5. five. L. He, C. Cheng, "Flying-Capacitor-Clamped five-degree Inverter based on Switched-Capacitor Topology," IEEE Trans. Ind. Electron., vol. sixty three, no.12, pp. 7814-7822, Sep. 2016.

- 6. k.Zou, M J.Scott, J.Wang, "Exchanged capacitor cellular based absolutely voltage multipliers and dc-air con inverters," IEEE Trans. Ind. Appl.,vol. forty eight, no. 5, pp. 1598-1609, Sept. /Oct. 2012

- 7. H.S.Chung, A.Ioinovici and W. L. Cheung, "Summed up structure of bidirectional exchanged capacitor dc/dc converters," IEEE Trans. Circuits Syst. I, Fundam. speculation Appl., vol. 50, no. 6, pp. 743-753, Jun. 2003.

- 8. X.solar,B.Wang,Y.Zhou, "A unmarried DC source Cascaded Seven degree Inverter Integrating Switched Capacitor techniques." IEEE Trans. Ind. Electron., vol. sixty three, no. eleven, pp. 7184-7194, Nov. 2016.

- 9. W. Li, X. He, "Audit of nonisolated excessive-reinforce up DC/DC converters in photovoltaic lattice associated programs," IEEE Trans. Ind. Electron., vol. fifty eight, no.four, pp. 1239-1250, may additionally moreover. 2010.

- 10. J.Anderson,F.Z.Peng, "a category of semi Z-source inverters," in Proc.IEEE Ind. Appl. Soc. Conf., Oct. 2008, pp.1-7

,