A Peer Revieved Open Access International Journal

www.ijiemr.org

#### **COPY RIGHT**

2019IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 4<sup>th</sup> Sept 2019. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-08&issue=ISSUE-09

Title MICRO GRID APPLICATIONS USING SOFT SWITCHED INTERLEAVED DC/DC CONVERTER AS FRONT-END OF MULTI INVERTER STRUCTURE

Volume 08, Issue 09, Pages: 241-257.

**Paper Authors**

#### V PRAVALIKA, P RUCHITHA, N ROSHINI

Anu Bose Institute of Technology K.S.P Road, New paloncha, Bhadradri Kothagudem, Telangana, India

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic

Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

# MICRO GRID APPLICATIONS USING SOFT SWITCHED INTERLEAVED DC/DC CONVERTER AS FRONT-END OF MULTI INVERTER STRUCTURE

V PRAVALIKA<sup>1</sup>, P RUCHITHA<sup>2</sup>, N ROSHINI<sup>3</sup>

<sup>1,2,3</sup>UG Students, Dept. of Electrical and Electronics Engineering

Anu Bose Institute of Technology K.S.P Road, New paloncha, BhadradriKothagudem, Telangana,

India.

vtrmohanrao1971@gmail.com<sup>1</sup>, polinaruchitha1@gmail.com<sup>2</sup>

Abstract:-An isolated four channels DC/ DC converter with zero voltage switching (ZVS) is proposed as front-end of multiple inverter structures to integrate renewable and other low voltage energy sources to micro grid. Interleaving technique is adopted to connect each module of proposed converter to a common dc source. This dc source can be a fuel cell stack, PV panels, battery or any other low voltage dc source. All four channels are interleaved and phase shift of 90° is provided between the gate signals of each channel which reduces the input current ripple. Output port of the proposed converter provides four isolated and regulated dc voltages. These isolated dc sources can be connected in series or parallel or series-parallel manner to obtain required dc link voltage of various inverter structure. Issues like capacitor voltage balancing of diode clamped multilevel inverters can overcome through proposed converter. By incorporating coupled inductor for isolation and energy storage along with voltage multiplier circuit, proposed converter can achieve higher voltage step up with lower turns ratio and lower voltage stress at moderate duty ratio. Hence MOSFETs of low voltage rating (low R<sub>DS</sub>(ON)) can be utilized to reduce conduction loss. A 2kW prototype of proposed interleaved DC/DC converter is developed and tested with diode clamped three level inverter, five level inverter and three phase two level inverter to verify the design.

# **Index Terms:-**DC-DC Converter, Zero voltage switching, Active clamp, Interleaving, Coupled inductor, High voltage gain.

#### I. INTRODUCTION

RAPID industrialization and globalization leads to the exploitation of nonrenewable fossil fuels. Fossil fuels are thus at verge of exhaustion. Moreover, these fuels cause carbon emission, global warming, climate changes and atmospheric pollution. Increasing day by day demand for electric energy of growing population is a major concern for power sector. Aforementioned facts leads to the development of clean and renewable energy sources like solar

photovoltaic (PV), fuel cells, wind energy, tidal energy etc. For efficient extraction of energy from these intermitted sources, power electronics converters are required [1], [2]. Output voltage of single PVmodule and fuel cells are very low and required to step up before connecting to the utility. Dc link voltage of 380V400V is required for a single phase grid connected inverter system [3]. In case of grid connected three phase full bridge inverter or diode clamped

A Peer Revieved Open Access International Journal

www.ijiemr.org

multilevel inverters, dc link voltage of 760V or more is preferred [3].In centralized PV systems, number of PV panels is connected in series to form a string to obtain high dc voltage. Multiple strings of PV then connected in parallel to realize required power. However, this PV architecture suffers from losses due to partial shading, panel mismatches, poor efficiency of maximum power tracking and hot spot effects [4]–[6]. To overcome these issues, parallel connected PV structure, multi string structure and modular PV systems are introduced in [7]-[10]. However, these PV structures produce low voltage dc output which needs to be step up efficiently. Hence efficient high voltage gain dc/dc converters are an essential requirement. To overcome the drawbacks of basic boost converter for high voltage step up applications, numerous high voltage gain dc/dc converters are presented in [9], [11]-[18]. Converters in [11] incorporate voltage multiplier circuit in basic boost converter structure to achieve high voltage step up with lower stress. Here, further enhancements of voltage gain require addition of more number of basic voltage multiplier circuits which increases component count and cost. Use of coupled inductor for high step applications is a good solution [9], [12], [13]. However, care should be taken to deal with leakage inductance and associated voltage spike on switches. Converters in [14], [15] make use of boost integration technique where a boost converter is integrated with a flyback converter to achieve step up voltage. Here boost converter acts as a lossless clamping circuit which recycles the leakage energy of flyback transformer. To enhance the voltage step up gain further, coupled inductor in association with switched capacitor voltage multiplier cells are presented in [16]. These converters are easily able to achieve high

voltage conversion gain without extreme duty ratio and voltage stress. Soft switching techniques are incorporated to coupled inductor converters in [17], [18] to enhance efficiency and power density. All these converters are found to be good choice in medium power level. However all these converters are nonisolated and do not meet the requirement of galvanic isolations laid regulating down by authorities and industries.In isolated converters, transformer turns ratio can be adjusted to obtain high voltage step up gain. However, voltage fed converters require large turns ratio which increases the size as well as leakage inductance of the transformer. Higher voltage stress on output diodes of voltage fed converters force to use high voltage rated diodes or external voltage clamping circuits which increases the cost. Modular converter scheme is proposed for high voltage gain application in [19]. Here three or more converters are connected in parallel at input side and in series at output side. Series connection of output terminals of the converter enhances the overall voltage gain. Similarly input series and output parallel modular dc/dc converter structure and its control is presented in [20]. Flyback converter which is derived from the buck boost converter is widely used for PV micro inverters in lower power levels [21], [22]. Flyback transformer transfer energy to output during only one switching state.

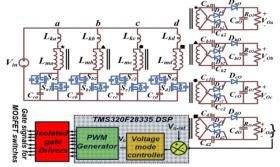

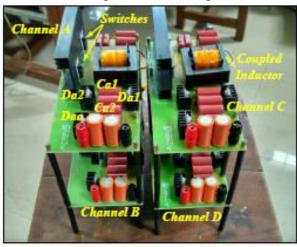

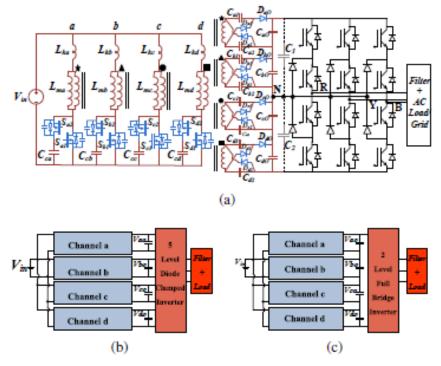

Fig. 1. Proposed Interleaved DC/DC Converter.

A Peer Revieved Open Access International Journal

www.ijiemr.org

Hence for high voltage step up, large magnetic core is required which increases the volume and weight. Isolated coupled inductor and voltage multiplier circuits are incorporated in [23] for high voltage gain. The converter in [23] makes use of dual voltage doubler circuit which reduce voltage stress on output diodes. Passive lossless clamp circuits which consist of a capacitor, two power diodes and an additional inductor is used to alleviate voltage stress on switches and recycle the leakage energy. Input current ripple is very high in this converter. In addition to this switches are hard switched in [23]. Need of an efficient dc/dc converter system having low input current ripple, high voltage gain, good power density, modularity and flexibility to use as a front end of multiple inverter structure to interface low voltage energy sources is in demand. This paper proposes an isolated four channel high step up DC/DC converter with soft switching for low output voltage dc sources. Proposed converter can easily interface with commonly used inverter structures such as single phase inverter, three phase inverter, diode clamped three level and five level inverters etc. Proposed converter produces four isolated and regulated dc voltages. Each of this dc output can be connected in parallel, series or series parallel combination to realize required dc link voltage of aforementioned inverter structure. At the input side of the converter, all four channels are connected in parallel and interleaving of converters is adapted to minimize the input current ripple.

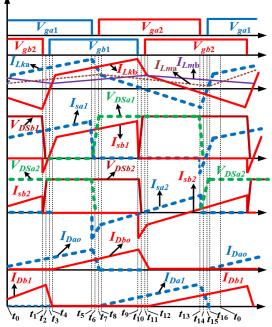

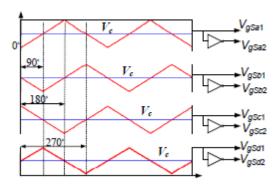

Fig. 2. Key waveforms of the converter.

Capacitor voltage balancing of diode clamped inverters is a well-known issue. Isolated dc sources can be used as front end active balancing circuit in diode clamped inverters [24] to overcome the voltage balancing problems. Proposed converter provides four isolated and regulated output which act as the front end of three and five level diode clamped inverters and overcome the capacitor voltage balancing problems. Proposed converter makes use of isolate coupled inductor along with dual voltage multiplier circuits to realize high voltage step up with lower voltage stress. Instead of passive clamp circuit of [23] which requires inductor and external more passive components, proposed converter incorporate active clamp circuits to alleviate the voltage stress due to leakage inductance. The active clamp circuit is originally proposed by Harada [25]. This clamp circuit is widely used to alleviate voltage spike on MOSFET switches of both forward and flyback converters [26]-[28]. Apart from voltage spike alleviation of switches, active clamp circuit can provide zero voltage turn-on of MOSFETs to reduces the switching losses.

A Peer Revieved Open Access International Journal

www.ijiemr.org

Hence high frequency operation is possible which reduces the size of magnetic components and filter capacitor.

# II. CIRCUIT DESCRIPTION AND OPERATION OF PROPOSEDCONVERTER

Proposed four channel interleaved converter is shown in Fig. 1. Basic module of each channel (a, b, c and d) are represented by its equivalent circuit model. Coupled inductor of each channel is represented by its

magnetizing inductance ( $L_{ma}$ , $L_{mb}$ , $L_{mc}$ , and  $L_{md}$ ) and leakage inductance ( $L_{ka}$ , $L_{kb}$ , $L_{kc}$ , and  $L_{kd}$ ) respectively. Switches  $S_{a1}$ , $S_{b1}$ , $S_{c1}$ and  $S_{d1}$  are the main switches of each channel. Switches  $S_{a2}$ , $S_{b2}$ , $S_{c2}$ , $S_{d2}$ and capacitors  $C_{ca}$ , $C_{cb}$ , $C_{cc}$ , $C_{cd}$ form active clamp circuit of each channel respectively. Couplingreferences for each channel are represented by symbols "F, N, •, ".

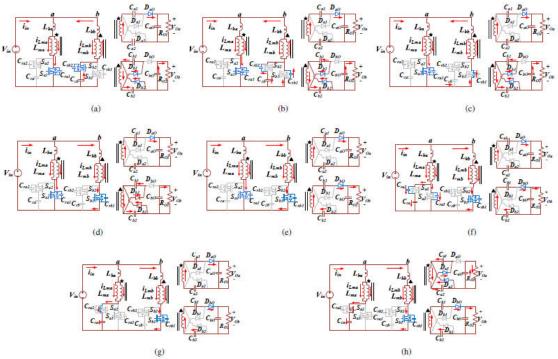

Fig. 3. Different modes of operation of the converter. (a) Mode 1  $(t_o - t_1)$ . (b) Mode 2  $(t_1 - t_2)$ . (c) Mode 3  $(t_2 - t_3)$ . (d) Mode 4  $(t_3 - t_4)$ . (e) Mode 5  $(t_4 - t_5)$ . (f) Mode 6  $(t_5 - t_6)$ . (g) Mode 7  $(t_6 - t_7)$ . (h) Mode 8  $(t_7 - t_8)$ .

For channel-a, voltage multiplier circuit of secondary side consisting of diodes and switched capacitors which are represented by D<sub>a1</sub>,D<sub>a2</sub>, C<sub>a1</sub>,C<sub>a2</sub> respectively. Similar notation is used for other channels also. Diodes D<sub>ao</sub>,D<sub>bo</sub>,D<sub>co</sub>and D<sub>do</sub>are the output diode of each channel. Main and clamp switch of all channels are operating at same frequency. However, gate signals for each channel are phase shifted by 90° between one another. Each converters output voltage is regulated to its the nominal value (200V)

for input voltage and output power variations by voltage mode controller. Due to the symmetry of converter structure, operational principle of converter is explained by considering two channels only. Key waveforms of operations are given in Fig. 2. Operating state of converter during each modes are shown in Fig. 3.

**Mode 1 (t<sub>o</sub> - t<sub>1</sub>):** During this mode, main switch  $S_{a1}$  of phase a and clamp switch  $S_{b2}$  of phase b are in conduction. At secondary side of phase a, energy of secondary

A Peer Revieved Open Access International Journal

www.ijiemr.org

winding and the capacitors  $C_{a1}$  and  $C_{a2}$  are transferred to the load through diode  $D_{ao}$ . In case of phase b, diode  $D_{bo}$  is reverse biased. Secondary winding of phase b, transfer its ensrgy to capacitor  $C_{b1}$  and  $C_{b2}$  through diodes  $D_{b1}$  and  $D_{b2}$ .

**Mode 2 (t<sub>1</sub> - t<sub>2</sub>):** At  $t_1$ , gate signal for clamp switch  $S_{b2}$  is withdrawn. Now primary current of phase b charge the output capacitor ( $C_{rb2}$ ) of  $S_{b2}$  and discharge  $C_{rb1}$  of  $S_{b1}$ .

**Mode 3 (t<sub>2</sub> - t<sub>3</sub>):** At t<sub>2</sub>, output capacitor  $C_{rb1}$  of switch  $S_{b1}$  completely discharged. Now primary current of phase b start conducting through the body diode of switch  $S_{b1}$ . The clamp switch  $S_{b2}$  is in off state. Operation of phase a is same as that of mode 1.

**Mode 4 (t<sub>3</sub> - t<sub>4</sub>):** While body diode of  $S_{b1}$  is conducting, gate signal to  $S_{b1}$  is applied at  $t = t_3$ . Hence main MOSFET ( $S_{b1}$ ) of phase b turn on with soft switching (Zero voltage switching). The primary current of phase b is starting to increase linearly.

**Mode 5** ( $\mathbf{t_4} - \mathbf{t_5}$ ): At  $\mathbf{t_4}$ , polarity of secondary winding of phase b reverse biases the diodes  $D_{b1}$ ,  $D_{b2}$  and forward bias output diode  $D_{b0}$ . Now reflected voltage at the secondary winding of phase b and stored energy of capacitors  $C_{b1}$  and  $C_{b2}$  transfer their energy to load in series.

**Mode 6 (t<sub>5</sub> - t<sub>6</sub>):** At t<sub>5</sub>, gate signal for the main switch  $S_{a1}$  of phase a is withdrawn. Now primary current of phase a charges the output capacitor ( $C_{ra1}$ ) of  $S_{a1}$  and discharge the output capacitor ( $C_{ra2}$ ) of  $S_{a2}$ . At secondary side, both phase a and phase b are transferring energy to their respective loads.

**Mode 7** ( $t_6$  -  $t_7$ ): The output capacitor ( $C_{ra2}$ ) of Switch  $S_{a2}$  is discharged to zero at  $t_6$ . Now body diode of clamp switch  $S_{a2}$  is conducting the primary current of phase a where main switch  $S_{a1}$  is in off state.

**Mode 8 (t<sub>7</sub> - t<sub>8</sub>):** At t<sub>7</sub>, gate signal to clamp switch  $S_{a2}$  is applied. Clamp switch  $S_{a2}$  turn

on with zero voltage switching (ZVS). The output diode ( $D_{ao}$ ) of phase a is reverse biased. Now secondary winding of phase a charges the capacitors  $C_{a1}$  and  $C_{a2}$  through diodes  $D_{a1}$  and  $D_{a2}$  respectively. Secondary winding of phase b continue to transfer its energy to the load trough diode  $D_{bo}$ . There are 16 modes of operation for the converter. However, due to the symmetry of converter, remaining 8 modes are very similar to that of aforementioned modes and hence not discussed in detail.

#### III. MATHEMATICAL ANALYSIS AND DESIGN OFPROPOSED CONVERTER

Steady state analysis of the converter is done with following assumptions: (a) Leakage inductance and its effect are not considered for this analysis. (2) Only average voltage across the capacitors are considered (ripple components are neglected),(3) All semiconductor devices are considered to be ideal, (4) Modes having very small time intervals are neglected including the dead time interval between the MOSFETs. (5) Only one phase (Phase a) is considered due to symmetry.

# A. Voltage conversion ratio (M) of the converter

When the main switch  $S_{a1}$  of phase a is ON, Voltage across the magnetizing inductance is given by

A Peer Revieved Open Access International Journal

www.ijiemr.org

$$V_{L_{ma}}^{ON} = V_{in}$$

(1)

$$V_{Oa} = V_{Ca1} + V_{Ca2} + V_{sec-a}^{ON}$$

(2)

$$V_{sec-a}^{ON} = NV_{in} \tag{3}$$

Let

$$V_{Ca_1} = V_{Ca_2} = V_{Ca} (4)$$

$$V_{Ca_1} = V_{Ca_2} = V_{Ca}$$

(4)

$V_{Ca} = \frac{V_{Oa} - NV_{in}}{2}$  (5)

When main switch  $S_{a1}$  is turned off

(6)

$$V_{sec-a}^{OFF} = -V_{Ca2} = -V_{Ca}$$

(7)

$V_{Lma}^{OFF} = \frac{-V_{Ca}}{N}$  (8)

$$V_{Lma} = \frac{1}{N} \tag{8}$$

Over one switching period, applying volt-second balance of magnteizing Inductance we yield,

$$DV_{in} + (1 - D)\frac{-V_{Ca}}{N} = 0$$

(9)

From (1) to (9), Ideal voltage conversion gain (M) of proposed converter is obtained as

$$M_{(ideal)} = \frac{V_{oa}}{V_{in}} = \frac{N(1+D)}{1-D}$$

(10)

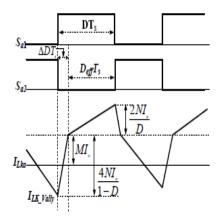

Here N stands for the turn ratio and D is the duty ratio. The leakage inductance of the converter cause duty cycle loss and thus reduces the voltage conversion gain. The duty cycle loss due to the leakage inductance can be obtained from idealized leakage inductance current as shown in Fig. 4.

$$D_{eff} = D - \Delta D \tag{11}$$

Fig. 4. Idealized current waveform to calculate effective duty cycle due to leakage inductance effect

Fig. 4. Idealized current waveform to calculate effective duty cycle due to leakage inductance effect

Expression for the voltage across the leakage inductance is given by

$$V_{Lk} = L_k \frac{dI_{Lk}}{dt} \tag{12}$$

Hence expression for duty cycle loss is obtained as

$$\Delta D = \frac{k.4N^2(1+D)}{(1-D)} \tag{13}$$

Where  $k=\frac{L_k f_s}{R_o}$ . From (10), (11) and (13), voltage gain of the converter by considering the leakage inductance effect is

$$M_{(leakage)} = \frac{V_{oa}}{V_{in}} = \frac{N(1 + D_{eff})}{(1 - D_{eff})}$$

(14)

B. Voltage across various elements

From (4) and (5), voltage across the capacitors  $C_{a1}$  and  $C_{a2}$ is obtained as

$$V_{Ca1} = V_{Ca2} = \frac{NDV_{in}}{1 - D} = \frac{DV_{oa}}{1 + D}$$

(15)

Voltage stress across the main switch  $S_{a1}$  and clamp switch  $S_{a2}$  is obtained by

$$V_{DSa1} = V_{DSa2} = V_{in} - V_{Lma}^{OFF} = V_{in} + \frac{V_{Ca}}{N}$$

(16)

Hence voltage stress across the MOSFETs switches of proposed converter is given by

$$V_{DSa1} = V_{DSa2} = \frac{V_{in}}{1 - D} \tag{17}$$

Voltage stress on the output diode  $D_{ao}$ , voltage multiplier diodes  $D_{a1}$  and  $D_{a2}$  is obtained as

$$V_{Da1} = V_{Da2} = V_{Dao} = \frac{V_o}{1 + D}$$

(18)

#### **C.Design of coupled Inductor**

The peak ripple current of magnetizing inductance is given as

$$\Delta i_{Lma} = \frac{V_{Lma}D}{L_m f_s} \tag{19}$$

Proposed converter is designed to operate in continuous conduction mode (CCM). At boundary between continuous and discontinuous conduction mode (BCM), average value of the converter's input current is half of the peak magnetizing current. Therefore,

A Peer Revieved Open Access International Journal

www.ijiemr.org

$$I_{in} = \frac{\Delta i_{Lma}}{2} \tag{20}$$

At steady state, assuming no losses,

$$\frac{V_{oa}}{V_{in}} = \frac{I_{ina}}{I_{oa}} = M \tag{21}$$

Hence.

$$\frac{I_{oa}N(1+D)}{1-D} = \frac{V_{in}D}{2L_{ma}f_s}$$

(22)

Therefore, Magnetizing inductance of coupled inductor required to operate the converter in CCM is derived as

$$L_{ma} > \frac{R_{O_{BCM}}D(1-D)^2}{2f_sN^2(1+D)^2}$$

(23)

D. Selection of switched capacitors  $C_{a1}$  and  $C_{a2}$ Switched capacitors  $C_{a1}$  and  $C_{a2}$  are selected as follows,

$$C_{a1} = C_{a2} \ge \frac{2P_{max}}{V_{Ca}^2 f_s} \tag{24}$$

Where  $P_{max}$  is the maximum power that can be delivered to load by individual converter.

#### E. Selection of clamp capacitor C<sub>ca</sub>

Value of clam capacitor is calculated based on resonant period between clamp capacitor  $C_{ca}$  and leakage inductance  $L_{ka}$  and is obtained as

$$C_{ca} \ge \frac{(1 - D_{min})^2}{\pi^2 L_{ka} f_s^2}$$

(25)

#### F. Selection of output capacitor

The output voltage of the converter should be ripple free (Ideally pure DC voltage). The output capacitor of proposed converter need to reduce the output voltage ripple as minimum as possible. Hence main criteria for the section of output capacitor is output voltage ripple ( $\Delta V_O$ ). When main switch of the proposed converter is in off state, the load is supported by the stored energy of output capacitor. Hence the change in output voltage is expressed as

$$\Delta V_O = \frac{Q}{C_o} = \frac{I_o(1-D)T_s}{C_o} \tag{26}$$

Where Q is the stored energy in the output capacitor. The expression for output capacitance of proposed converter is obtained as

$$C_o \ge \frac{I_o(1 - D_{min})}{\Delta V_o f_s} \tag{27}$$

In proposed converter, output voltage ripple is taken as 0.1% of the output voltage  $(\Delta V_0 = 0.2V)$ . The output capacitor value is calculated for minimum duty cycle and obtained as 98.75µF. To reduce the ESR of output capacitor, higher value of capacitance (200µF) is selected. Two 100µF, electrolytic capacitors are connected parallel to reduce the **ESR** converter effect.Proposed topology derived from flyback converter. However, the transformer polarities are similar to forward type converter. The coupled inductor of conventional active clamp circuit transfer energy to output only at one switching instant. Thus conventional flyback converter requires large magnetic core. In proposed converter, coupled inductor transfer its energy to secondary side during both switch on and off instant and thus have better magnetic utilization compared to the flyback topology. Another two switch converter commonly used is half bridge converter with center tap output rectifier. For high voltage step application, half bridge converter need large turns ratio. This will increase the required core size of the isolation transformer. In addition to this, large turn ratio increases the leakage inductance the isolation of transformer. Leakage inductance cause voltage stress on the MOSFETs and thus snubber circuits are required to alleviate voltage stress on the switches. Comparison of active clamp and centre tap half bridge converter with proposed soft converter is shown in Table I. For high step up applications, voltage stress on output diode of both flyback and half bridge converter is much higher than the output voltage. Thus diodes of high voltage rating are needed in half bridge and flyback converters when used for voltage step-up applications. High voltage rated diodes

A Peer Revieved Open Access International Journal

www.ijiemr.org

adversely affect the switching performance and thus high frequency operation is not preferable. The leakage inductance of the transformer forms a resonance with parasitic capacitance of the output rectifier diodes. This resonance causes voltage ringing across the diodes. Hence lossy RCD snubber or external active snubbers are required to protect the output diodes from voltage excursion. However, inproposed converter, output diode voltage stress in lower than the output voltage. Hence no additional snubber is required to protect the diodes. In addition to this, maximum duty cycle operation of half bridge converter is restricted to be 0.5 which limits the operation for a wide input voltage variation. Both the switches of half bridge converters are hard switched and cause switching losses. Soft switching of half bridge obtain introducing converter can by resonant tank circuits. However, requires additional inductor and capacitors to be added and also face the voltage regulation problem light load. Compared to half bridge and flyback converter, proposed topology have advantages like high voltage gain, low voltage stress on output diodes, soft switching of all MOSFET switches, require lower turns ratio for voltage step-up, no need of additional snubber for output diode protection etc. Thus for high voltage step up applications, proposed converter scheme is more suitable than the voltage fed half bridge, flyback and full topologies.

# IV. EXPERIMENTAL VALIDATION OF PROPOSEDCONVERTER

An experimental prototype of proposed 2kW, 4-channel interleaved converter is fabricated in laboratory. Each individual channels are of 500W.

TABLE I

COMPARISON BETWEEN THE ACTIVE CLAMP FLYBACK CONVERTER,

CENTER TAP HALF BRIDGE CONVERTER AND PROPOSED SOFT SWITCHED

CONVERTER

| Parameter                         | Active<br>clamp<br>flyback<br>Converter | center tap<br>half bridge<br>converter | proposed soft<br>switch<br>converter |

|-----------------------------------|-----------------------------------------|----------------------------------------|--------------------------------------|

| MOSFETs                           | 2                                       | 2                                      | 2                                    |

| Diodes                            | 1                                       | 2                                      | 3                                    |

| Magnetic<br>component             | 1                                       | 2                                      | 1                                    |

| Voltage gain                      | $\frac{ND}{1-D}$                        | ND                                     | $\frac{N(1+D)}{1-D}$                 |

| Voltage stress on<br>MOSFET       | $\frac{V_o}{ND}$                        | $\frac{V_o}{ND}$                       | $\frac{V_o}{N(1+D)}$                 |

| Voltage stress on<br>output diode | $\frac{V_o}{D}$                         | $\frac{V_o}{D}$                        | $\frac{V_o}{1+D}$                    |

| Soft switching of<br>MOSFETs      | ZVS                                     | hard switch                            | ZVS                                  |

TABLE II

SPECIFICATIONS OF THE THE HARDWARE PROTOTYPE

| Components                     | Specifications                                 |  |

|--------------------------------|------------------------------------------------|--|

| Output Power                   | 2kW                                            |  |

| Number of channels             | 4                                              |  |

| Each channel's output power    | 500W                                           |  |

| Input range                    | 45V-65V                                        |  |

| Output voltage of each channel | 200V                                           |  |

| MOSFETs                        | IRFP4227pbf                                    |  |

| Diodes                         | BYC10D600                                      |  |

| Switching frequency            | 100KHz                                         |  |

| Turns ratio                    | 1:2                                            |  |

| Switched Capacitors            | $20\mu F ((2 \times 10\mu F \text{ of } 250V)$ |  |

| Output capacitor               | $200\mu F$                                     |  |

| Magnetizing Inductance         | 113μH                                          |  |

| Clamp capacitor                | $9.4\mu$ F ((2 × 4.7 $\mu$ F)                  |  |

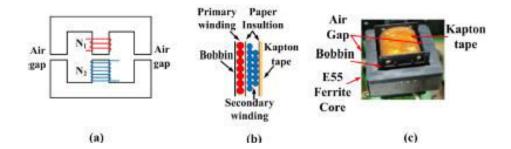

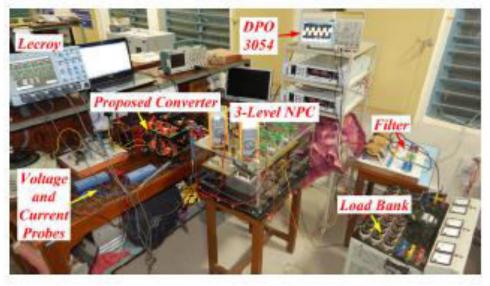

Photograph of the prototype is shown in Fig. 5. Details of hardware prototypes are given in Table II. E55 core is used for coupled inductor. Structure of the coupled inductor is given in Fig. 6. Primary and secondary winding are wound on the bobbin which is placed on the middle limb. Litz wires are used to wound the primary and secondary in order to reduce the skin effect. After wounding the primary, masking tapes (insulating paper) is used to separate primary and secondary winding. winding structure is shown in Fig. 6(b). Finally polymide film tape (Kapton) is wrapped around the windings. Polymide tapes have high thermal stability. Primary and secondary winding can be wound in interleaved manner to reduce the leakage inductance. However, in proposed

A Peer Revieved Open Access International Journal

www.ijiemr.org

converter, leakage inductance is a blessing in disguise to maintain ZVS of main MOSFETs for wide load variations. Hence, primary and secondary are wound separately and provided insulation in between. Proposed converter have high DC

bias current. This DC current will saturate the ferrite core. To alleviate the core saturation, air gap is provided in the magnetic path. Panasonic make metalized Polyester film Capacitors are selected for clamp and switched capacitors.

Fig. 5. Photograph of proposed 2kW interleaved converter

Fig. 6. Structure of coupled inductor (a) Schematic representation (b) Winding structure (c) Actual picture.

MOSFETIRFP4227pbF having low  $R_{DS(ON)}$  (21m $\Omega$ ) is used for main and clamp switch of each converter. Floating point digital controller (TMS320F28335) is used to control the proposed converter. Voltage mode controller is adopted to control the output voltage of the converter. Since all the converters are identical and constructed with same specification, authors are adopted a single voltage feedback from one channel and used this information to control the output voltage of other channels as shown in Fig. 1. The coupled inductor of each

converter is constructed for same turn ratio, magnetizing inductance and leakage inductance. However, even all the cares are taken to make the coupled inductor identical to each other, it is very difficult to obtain the leakage inductance of all the four coupled inductor identical. Thus leakage inductance of coupled inductor is slightly different for each channel. From (13), the duty cycle loss and thus output voltage variation due to leakage inductance can be obtained. The coupled inductor of proposed converter is wound in manner to get close values of

A Peer Revieved Open Access International Journal

www.ijiemr.org

leakage inductance between each channel. In experimental prototype, the measured leakage inductances of each channel are  $L_{ka}$ = 1.53 $\mu$ H,  $L_{kb}$ = 1.51 $\mu$ H,  $L_{kc}$ = 1.495 $\mu$ H and  $L_{kd}$ = 1.503 $\mu$ H respectively. maximum variation in output voltage between the channels due to leakage inductance effect is below 0.4%. However, during experimentation, other non-idealities and variation due to temperatures are presented. At full load, for minimum input voltage, the maximum output voltage variations between the channels-a and channel-c is 1.8V. This is acceptable for the application point of view where converter is feeding to the dc link capacitors of various inverters. Since magnetizing and leakage inductance of all the four channels are almost identical. the current problem is not severe in proposed converter structure.

Fig. 7. Schematic of generating 90° phase shifted gate signals for the converter

This can be seen from the experimental result of input current waveforms where all current peaks are nearly same and uniform. Since the output voltage variation of proposed converter is very small between four output channels, authors implemented simple voltage mode control strategy. Here output voltage of channel-d (whose leakage inductance is very close to the desired designed value of 1.5µH) is sensed through voltage sensor and feed to TMS20F28335

controller. The voltage controller output signal (V<sub>c</sub>) is then feed to the digital PWM modulator (ePWM module in **DSP** controller) which perform the duty of comparator. To generate phase shift of 90° between each channel, dedicated phase shift registers (TBPHS) are available in ePWM modules of C2000 controllers. Required phase shift value is written in this register. The first epwm module is acting as a MASTER and remaining three PWM modules are SLAVES. The slave PWM modules are synchronized with MASTER units and generate the carrier signals of same frequency of master with required phase shift. Master unit generate the synchronisation signal for the first slave with the time delay of 90°. The first slave generates synchronisation signal for the second slave after a delay of 90° and so on. Thus the carrier triangular signals are phase shifted by 90° each other. The compare registers of master and slave pwm modules are feed with digital equivalent value of control voltage (Vc). Hence master and slaves produces the pwm signals of same frequency and duty ratio but phase shifted by 90° each other. The basic operation of generating phase shift of 90° for each channel is depicted in Fig. 7.

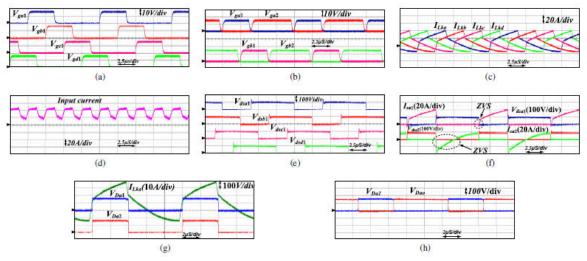

Gate signals for main and clamp switches of all channels are of same frequency. In Fig. 8 (a), gate signals for the main switches of all four channels are shown. Gate signals of clamp switches are complementary to the main switches of each channels. In Fig. 8 (b), gate signal for main and clamp switches of channel a and channel b are depicted. Proposed converter is tested for full load condition. Input currents of individual channels at full load for source voltage of 55V ( $V_{in} = 55V$ ) is shown in Fig. 8 (c). In Fig. 8 (d), resultant input current drawn from the input source by interleaving

A Peer Revieved Open Access International Journal

www.ijiemr.org

operation of all the four channels is shown. It is clear that resultant input current due to the interleaving operation have less ripple compared to the input currents of individual converters. Drain to source voltage (voltage stress) of main MOSFET of all channels is shown in Fig. 8 (e). Clamp circuit successfully alleviated the high voltage spike due to leakage inductance and clamps the voltage stress near to 100V. Hence low voltagerated MOSFETs which have lower R<sub>ds(on)</sub> can be selected for main and clamp switches which reduces the conduction loss. **MOSFETs** switches proposed of converter turn on with zero voltage switching (ZVS). In Fig. 8 (f), ZVS turn on of main and clamp switches of channel-a is shown. ZVS turn on region is highlighted in Fig. 8 (f). The switch currents and input currents of all channels are measured with AP015 current probe. Voltage stress on diodes (D<sub>a1</sub>,D<sub>a2</sub>) of voltage multiplier circuits of channel-a is shown in Fig. 8 (g) along with input current of same channel. In Fig. 8 (h), voltage stress on output diode (Dao) and the diode Da1 of channel-a is depicted. From these results, it is evident that voltage stress on all diodes is well below the output voltage of converter. In addition to this, there is no voltage spike or ringing across the diodes. Therefore over voltage protection for diodes are not required in proposed converter.ZVS of main switch (Sa1) is load depended and the ZVS characteristic will loss at light load condition. ZVS of main switch mainly depends on the stored energy of leakage inductance. However, for clamp switch (S<sub>a2</sub>), maintaining ZVS at light load is possible due to the stored energy of both leakage and magnetizing inductance. Hence irrespective of load condition, clamp switch

can maintain ZVS for wide load range. To achieve ZVS of main switch  $S_{a1}$ , the energy stored in the leakage inductance ( $L_{ka}$ ) at time instant  $t_{13}$  of Fig. 2 should be sufficiently high to discharge the parasitic capacitance of switch  $S_{a1}$  and charge the parasitic capacitance of switch  $S_{a2}$ . Thus the condition for ZVS of main switch  $S_{a1}$  is obtained as

$$\frac{1}{2}L_{ka}I_{Lk(t_{13})}^{2} \ge \frac{1}{2}C_{r_{(eff)}}V_{Dsa}^{2}$$

(28)

Here  $C_{reff}$  is the effective parasitic capacitance of  $S_{a1}$  and  $S_{a2}$ , which can be obtained from the data sheet of MOSFETs. The above relationship can be expressed as

$$L_{ka} \left[ \frac{4N}{1-D} \right]^2 I_o^2 \ge C_{r_{(eff)}} V_{Dsa}^2$$

(29)

The minimum load condition at which ZVS of the main switch is maintained is thus obtained as

$$I_{o-min} = \sqrt{\frac{C_{r_{(eff)}}}{L_{ka}}} \frac{V_{Dsa}}{\left[\frac{4N}{1-D} - M\right]}$$

(30)

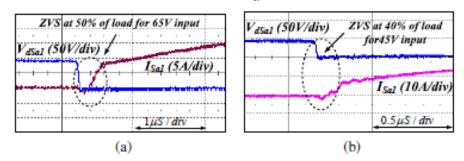

From above relationship, for an input voltage of 65V, it is found that the ZVS of the main switch can theoretically obtained up to 12% of the full load condition. However, in actual practice, ZVS of the main switch is maintained only up to 28% of the full load. This reduction in ZVS range is due to the PCB track capacitance, large capacitance of transformer winding etc. In Fig. 9(a), zero voltage turn-on of main switch of channel-a at 50% of the full load is shown. In Fig. 9(b), ZVS turn-on of the main switch at 40% of the full load is given when the input voltage is 45V.Isolated output port of proposed converter can be connected in series, parallel or combination of series-parallel to obtain required dc link voltage for various inverter structures.

A Peer Revieved Open Access International Journal

www.ijiemr.org

Fig. 8. Experimental results at full load for  $V_{in}$  = 55V, (a) Gate signals for main switches of all four channels which are phase shifted by 90° (b) Gate signals for main and clamp switches of channel-a and channel-b. (c) Input current drawn by individual channels at full load (d) Resultant input current drawn from the input source at full load by interleaving operation of all four channels (e) Voltage stress across the main switches of all four channels at full load (f) Soft turn on (ZVS) of main and clamp switches of channel-a, ZVS turn on region is highlighted (g) Voltage stress across the voltage multiplier diodes  $D_{a1}$  and  $D_{a2}$  of channel-a along with input current of same channel (h) Voltage stress across the output diode  $D_{a0}$  of channel-a along with voltage stress of diode  $D_{a1}$ .

Fig. 9. Experimental results: (a) ZVS turn-on of main switch at 50% of full load for an input voltage of 65V. (b) ZVS turn-on of main switch at 40% of full load for an input voltage of 45V.

To validate this, proposed converter is tested with three phase, 3 level neutral point clamped (NPC) inverter, 2 level inverter, 5 level inverter etc. and results are provided. In Fig. 10 (a), schematic of proposed converter feeding a three level NPC inverter is shown. Output ports of all the channels are connected in series to obtain dc link voltage of 800V (More than 750V dc voltage is preferred incase of grid connected applications). Neutral point of inverter is connected between the channel b and C. Hence with respect to neutral point, dc voltage across the capacitors C<sub>1</sub> (V<sub>C1</sub>) and  $C_2(V_{C2})$  are +400V and -400V respectively. Capacitor balancing problem is predominant

in 5 level diode clamped inverters. In [24], capacitor voltage balancing of 5 level diode clamped inverter using a three level dc/dc converter is proposed. In [24], two inner dc link capacitors of five level diode clamped inverter is balanced by the regulated output voltage of three level dc/dc converter. However, for remaining two capacitors, additional balancing circuit is required. In [24], balancing circuit of each outer capacitors consist of additional external inductor, MOSFETs, diodes. voltage sensing circuits and additional control circuits. This makes the system more complex and difficult to control.

A Peer Revieved Open Access International Journal

www.ijiemr.org

Fig. 10. Schematic of proposed converter feeding to different inverter structures: (a) Proposed converter feeding to a three phase 3-level NPC inverter (b) Proposed converter connected to a 5-level diode clamped Inverter (c) Proposed converter feeding a three phase 2-level inverter structure.

In proposed converter, each isolated output channels can connected to 5-level diode clamped inverter as shown in Fig. 10 (b). Each output channels provides regulated dc output voltage and thus balance the capacitor voltage of 5level NPC without external balancing circuits. In Fig. 10 (c), schematic of proposed converter feeding a three phase 2-level inverter is given.

Feasibility of proposed converter to act as a front end for various inverter structure is experimentally verified. Experimental setup of proposed converter feeding a three phase 3level NPC inverter is shown in Fig. 12. For experimentation, SEMIKRON made 3-level inverter which is available in the laboratory is used.

Fig. 11. Experimental set of proposed converter feeding energy to three phase three level NPC inverter

A Peer Revieved Open Access International Journal

www.ijiemr.org

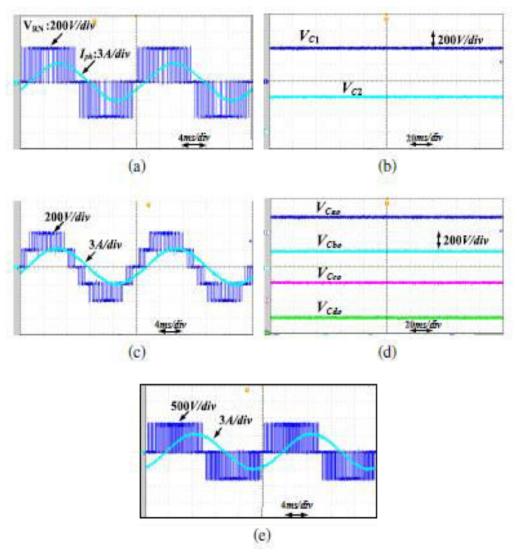

Fig. 12. Experimental results: (a) Phase voltage and current of three level inverter feeding R-L load of 0.85 power factor (b) Regulated and balanced dc link voltage of 3 level diode clamped inverter (c) Phase voltage and current of 5 level diode clamped inverter feeding to R-L load of 0.85 power factor (d) Balanced DC link voltage of five level diode clamped inverterwhich is regulated by proposed converter (e) Line voltage and current of 2 level full bridge inverter feeding R-L load of 0.85 power Factor.

Capacitors  $C_1$  and  $C_2$  are inbuilt in SEMIKRON inverter. However, by designing the output capacitors  $C_{ao}$  to  $C_{do}$ , according to the required power level and voltage ripple, capacitors  $C_1$  and  $C_2$  can be eliminated. Inverter control is done with TMS320F28377d DSP. In Fig. 12 (a), phase voltage and current of three level inverter feeding R-L load of 0.85 power factor is shown. Loads are star connected. Input capacitor voltages  $V_{C1}$  and  $V_{C2}$  of three level NPC inverter is constituted by output voltage of proposed converter as mentioned

earlier. Balanced dc link voltages  $V_{C1}$  and  $V_{C2}$  of three levels NPC inverter is given in Fig. 12 (b). Proposed converter is also tested with 5-level diode clamped inverter and two level inverter structures. Experimental setup is made according to schematic given in Fig. 10 (b) and Fig. 10 (c) and results are provided for the same load condition of three level set up. Phase voltage and load current of five level diode clamped inverter is given in Fig. 12 (c).

A Peer Revieved Open Access International Journal

www.ijiemr.org

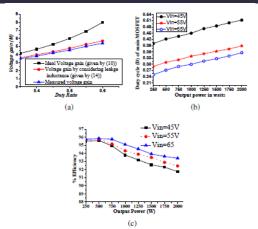

Fig. 13. (a) Steady state curves on theoretical and measured voltage conversion gain of single converter (channel-a). (b) Output power versus duty cycle of the converter. (c) Efficiency plot of proposed converter for input voltages of 45V, 55V and 65V.

Balanced dc link voltages of five level inverter, which is constituted by the regulated and isolated output voltages of proposed converter is shown in Fig. 12 (d). As evident from these results, proposed regulated converter's output voltages overcome the capacitor voltage balancing issues of diode clamped inverters. Line voltage and current of three phase 2-level inverter is shown in Fig. 12 (e). During all conditions, proposed these converter structure was able to provide balanced and regulated voltages for different inverter structures.

Steady state curve for theoretical and measured voltage conversion gain of the converter (channel-a) is depicted in Fig. 13 (a). Here ideal voltage conversion gain of the converter is obtained from the equation (10) and plotted for duty ratio ranging from 0.35 to 0.6. The leakage inductance of coupled inductor reduces the effective duty cycle of the converter. This duty cycle loss reduces the voltage gain of the converter compared to the ideal one. The voltage gain of the converter considering the effect of leakage inductance is obtained by the equation (14). Experimentally measured voltage gain of the converter is still less than that of the voltage gain due to the leakage inductance effect. This is due to the voltage drop across the parasitic elements like resistance of coupled inductor, voltage drop across the diodes and MOSFETs etc.

In Fig. 13 (b), steady state output power versus duty cycle of the proposed converter is given. Here all the four converters are connected in interleaved manner to the common input source. The output voltage of all converters is regulated to 200V through voltage mode controller. The output ports of each converter are connected in series to form 800V dc bus and then feed to the resistive load bank. The output power versus duty cycle is plotted for an input voltage of 45V, 55V and 65V.

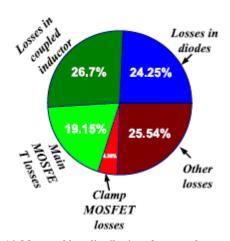

Fig. 14. Measured loss distribution of proposed converter at full load for 45V input.

Here duty cycle D represents the duty cycle of main MOSFET switches of each channels  $(S_{a1}, S_{b1}, S_{c1} \text{ and } S_{d1})$ . All the four channels are operating at same switching frequency and duty ratio. However, gate pulses are phase shifted by  $90^{0}$  to reduce the input current ripple. Efficiency of proposed converter is measured for different load and input voltages. Designed input voltage range of proposed converter is 45V to 65V. Efficiency of the converter is measured for designed maximum input voltage (65V), minimum input voltage (45V) and an

A Peer Revieved Open Access International Journal

www.ijiemr.org

intermediate input voltage (55V). Efficiency curve for above conditions are shown in Fig. 13 (c). Highest efficiency of proposed converter is obtained as 95.83% for the designed maximum input voltage of the converter. Measured lowest efficiency is found to be 91.75% at full load condition where the input voltage is at designed minimum value (45V). From efficiency plot, it is clear that proposed converter can operate with fairly good efficiency over a wide range of load conditions. Apart from the designed lowest input voltage, efficiency of proposed converter is found to be above 93% for all load conditions. The loss analysis is done for full load condition and designed low input voltage(45V). The breakup of various losses is shown in Fig. 14. Due to the high RMS input current, losses of coupled inductor constitute 26.7% of total loss of the converter. To reduce the conduction losses in switches, low voltage having low rated MOSFET resistance is selected. The conduction loss of main and clamp switches are 19.15% and 4.36% of total power loss of the converter. The other losses are calculated based on the difference between the measured efficiency of the converter and measured losses of main components. This include, turnoff switching losses of the MOSFETs, losses due to the ESR of switched capacitors, output capacitors, input filter capacitors, losses in driver circuit and auxiliary power supply for the driver circuitry.

#### V. CONCLUSION

An isolated 4-channel interleaved dc/dc converter with soft switching and high voltage step up gain is proposed as a front end of multiple inverter structures. Proposed converter makes use of isolated coupled inductor and dual voltage multiplier circuit to achieve voltage step up with lower voltage stress on devices. Active clamp

circuit is used to clamp the voltage spike on MOSFETs and also to provide soft turn on MOSFET switches. Interleaved for operation enhanced the power output and reduces the input current ripple. Modularity proposed converter is an added advantage. Four isolated output port of proposed converter can be connected in series, parallel or series-parallel combination to obtain required dc link voltages of multiple commonly used inverter structures like three phase two level inverter, three level NPC and five level NPC inverter structures. Proposed converter can overcome the capacitor voltage balancing issues of five level and three level NPC inverters without any additional voltage balancing circuits. Feasibility of same is experimentally verified and results are shown. By using MOSFETs of low on state resistance, conduction losses are reduced in proposed converter. A 2kW prototype of proposed converter is build and results are verified. Maximum efficiency of proposed converter is found to be 95.83%.

#### REFERENCES

- 1) F. Blaabjerg, Z. Chen, and S. B. Kjaer, "Power electronics as efficient interface in dispersed power generation systems," IEEE Trans. Power Electron., vol. 19, no. 5, pp. 1184–1194, Sept 2004.

- 2) M. Liserre, T. Sauter, and J. Y. Hung, "Future energy systems: Integrating renewable energy sources into the smart power grid through industrial electronics," IEEE Ind. Electron. Mag., vol. 4, no. 1, pp. 18–37, March 2010.

- 3) Y. Zhao, X. Xiang, W. Li, X. He, and C. Xia, "Advanced symmetrical voltage quadrupler rectifiers for high step-up and high output-voltage converters," IEEE Trans. Power Electron, vol. 28, no. 4, pp. 1622–1631, 2013.

A Peer Revieved Open Access International Journal

www.ijiemr.org

- 4) C. S. Solanki, Solar photovoltaics: fundamentals, technologies and applications. PHI Learning Pvt. Ltd., 2011.

- 5) P. Sharma and V. Agarwal, "Exact maximum power point tracking of grid-connected partially shaded pv source using current compensation concept," IEEE Trans. Power Electron., vol. 29, no. 9, pp. 4684–4692, Sept 2014.

- 6) B. I. Rani, G. S. Ilango, and C. Nagamani, "Enhanced power generation from pv array under partial shading conditions by shade dispersion using su do ku configuration," IEEE Trans. Sustain. Energy, vol. 4, no. 3, pp. 594–601, July 2013.

- 7) L. Gao, R. A. Dougal, S. Liu, and A. P. Iotova, "Parallel-connected solar pv system to address partial and rapidly fluctuating shadow conditions," IEEE Trans. Ind. Electron., vol. 56, no. 5, pp. 1548–1556, May 2009.

- 8) A. D. Grasso, S. Pennisi, M. Ragusa, G. M. Tina, and C. Ventura, "Performance evaluation of a multistring photovoltaic module with distributed dc/dc converters," IET Renewable Power Generation, vol. 9, no. 8, pp. 935–942, 2015.

- 9) Q. Zhao and F. C. Lee, "Highefficiency, high step-up dc-dc converters," IEEE Trans. Power Electron, vol. 18, no. 1, pp. 65–73, 2003.

- 10) L. Zhang, K. Sun, Y. Xing, L. Feng, and H. Ge, "A modular gridconnected photovoltaic generation system based on dc bus," IEEE Trans.

- 11) Power Electron., vol. 26, no. 2, pp. 523–531, Feb 2011.