A Peer Revieved Open Access International Journal

www.ijiemr.org

#### **COPY RIGHT**

2019IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 4<sup>th</sup> Sept 2019. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-08&issue=ISSUE-09

Title H-BRIDGE CONVERTERFOR HVDC APPLICATION

Volume 08, Issue 09, Pages: 192-218.

**Paper Authors**

#### G SURYATEJA, K NANDHAKUMAR, K OM SAISHANKAR

Anu Bose Institute of Technology K.S.P Road, New paloncha, Bhadradri Kothagudem, Telangana, India

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic

Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

#### H-BRIDGE CONVERTERFOR HVDC APPLICATION

G SURYATEJA<sup>1</sup>, K NANDHAKUMAR<sup>2</sup>, K OM SAISHANKAR<sup>3</sup>

1,2,3 UG Students, Dept. of Electrical and Electronics Engineering Anu Bose Institute of Technology K.S.P Road, New paloncha, BhadradriKothagudem, Telangana, India. gandepallisuryateja@gmail.com<sup>1</sup>, nanda14340@gmail.com<sup>2</sup>, koppulaomsai@gmail.com<sup>3</sup>

Theoretical:- A H-companion cream indifferent converter (HBHMC) is proposed for HVDC bundles. It utilizes a wave-encircling circuit (WSC) in regards to way of development related full-interface sub modules (FBSMs) on the yield of the most significant H-buddy converter (MHBC). For a 3-mastermind gadget, three HBHMCs are related either in (amusement plan HBHMC) orin (parallel-HBHMC) over the dc-interface. The running methodologies for HBHMC, novel adjustment frameworks for voltage changing over of FBSMs, and controlof HBHMC put together HVDC structures are appeared with respect to this paper. A point by perspective association among HBHMC and exact cross breed topologies is cultivated relying upon required amount of switches and capacitors. The HBHMC has the skills of dc helpless factor blocking usefulness, lower affect shape and extra recognition of threat for sub modules capacitor voltage evolving. The adequacy of the HBHMC principally based totally HVDC device forthree-orchestrate adjusted and lopsided machine circumstances and its concern tolerant ability are upheld the utilization of PSCAD excitement mulls over. so also, the proposed converterunder average, and dc insufficiency circumstances, and of the proposed capacitor voltage oversee plan are certified no doubt by methods for utilizing a threeestablishment shape related HBHMC inquire about notoriety model. The impacts demonstrate the plentifulness of the proposed HBHMCtopology, oversee procedures, and engaging reactions of the HBHMC fundamentally based HVDC shape.

**IndexedTerms**: Dc insufficiency tolerant, H-join half of breed exact converter (HBHMC), HVDC structures, and estimated stunned converter.

#### I. INTRODUCTION

confined amazed converter is fast getting the hazard to be one of the most supported topologies for **VSC HVDC** based transmission structures [1]-[4]. largely a right away end result of its focal like points anticipated high-quality, adaptability, low conduction disasters, low consonant channel want, and low dv/dt, which permits using transformer with low insurance crucial. anyways, MMC has requirements, for example, the vital of a extraordinary variety of devices and

capacitors, weak point/beyond what many may want to do not forget possible deficiency go with the flow if there want to be an prevalence of a dc side ailment without the use of a dc electric transfer, and the proximity of coursing streams in every degree leg of the MMC [5]-[10]. The coursing cutting-edge basically impacts the tests of the converter portions, capacitors voltage swells and feature an effect on mishaps. A surrounding current manage is critical to reduce such affects [11]-[13].

A Peer Revieved Open Access International Journal

www.ijiemr.org

Plus, at some point of a dc aspect trouble, excessive hassle current-day travels via freewheeling diodes related over each IGBTs inside the MMC [5]-[17]. one of the techniques to control deal with this problem is to apply a dc electric powered switch starting overdue proposed in [14]-[17]. in the consequent tool, in preference to the HBSM, every different SM with the capability to deliver the alternative furthest issue voltage is used that squares/limits the insufficiency modern-day degree if there need to be an occasion of dc aspect inadequacy [18]-[22]. inthe third manner, theconverter plan itselfis modified and with the aid of manner of using the FBSMs, the blemish cutting-edge impediment practiced. This collecting of convertersis known as because the HMCs [23]-[34]. HMCs includes for the most segment territories, a DS and a WSC. DSsarethe course of development seeking of through interfacing bunches of FBSMs in plan. a large portion of the HMCs, the HCMC has de inadequacy tolerant limit, measure of SMs in WSC and quarter the measure of SM capacitors to that during MMC, which enacts more noteworthy humble impact and decrease occurrences [23]-[26], [30]. regardless, it has better afflictions inside the DSs because of hard purchasing and selling and it requires low name for consonant channels to relieve low hugeness spikes in perspective on missynchronization of DSs and WSC [24]. moreover, for changing of SMs capacitor voltages both well ordered scope of SMs are required or the DSs are required to switch at higher rehash, which turns on higher accidents [24], [25], [31]. The AAMMC, proposed in [27]-[29], has capacities like, dc issue tolerant ability, a huge piece of the amount of SMs to that inside the MMC and reduction afflictions. In any case, for the

smooth current compensation among top and lower arms and for the capacitor voltage changing in WSC, a brisk term spread length is needed [31]. It makes an extreme inrush present day in the fingers and a fittingly foreseen arm inductor is required for covering this inrush present day. The parallel mixture MMC is some other promising topology for HVDC applications on account of diminishing part check and touchy exchanging of DSs [33], [34]. In any case, its favored limits are that it can't rectangular/limit dc trouble present day and it has lower name for tune on the dc-friend. in light of the ones sounds the dc voltage can't be figured out how to a continuing on with well worth, which gives the quality control [34]. beginning past due, each other HMC is proposed which utilizes the WSC over the store [35]. The DSs of this topology are worked aslant even as the yield voltage is propped to dc-interface voltage respect, in this manner permitting the vitality trade some of the dc-connection and FBSMs. This timespan is very stacks nothing and if there should be an occurrence of over the top exact power need the converter is expected to take centrality from dc-interface inside that little length, which can likewise reason intemperate inrush present day-day. in the long run, it requires a dc angle inductor and drifting contraption to limitation the inrush present day. additionally, this converter does now not have dc flaw tolerant limit. This paper proposes H-accomplice crossbreed foreseen converter (HBHMC) topology, which watches out for part of the issues of the current HMC topologies as refered to already. The HBHMC topology has dc bother tolerant capacity, little influence shape, intemperate dc-interface use, an extra level of risk for SM capacitor voltage changing, and it may be connected with

A Peer Revieved Open Access International Journal

www.ijiemr.org

unreasonable voltage-low blessing or low voltage-extreme present day bundles. in this paper, the single degree and 3 area HBHMC structures, strategies for movement of HBHMC, the WSC capacitor voltage changing arrangement with the guide of fittingly picking filling and detachment modes, and individual capacitor voltage altering plan of WSC SMs of HBHMC are demonstrated. The abundancy of the proposed voltage control plans, equality and control of HBHMC and dc flaw tolerant capability of the converter are supported the utilization of every reenactment investigate considers. The thing by methods method for segment innovation assessments of a HBHMC based absolutely unquestionably HVDC machine for various contrasting working conditions are done the utilization of PSCAD/EMTDC. underlying assessments are played out the utilization of a 3-set up structure related HBHMC gear model. likewise, a near record is completed the different proposed and the contrary blessing blend converter topologies.

# II.H-BRIDGE HYBRID MODULAR CONVERTER

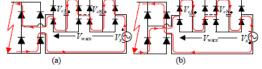

A. unmarried-degree format

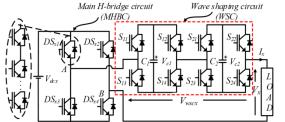

The proposed single-set up HBHMC is affirmed up in Fig. 1. Like different HMCs alluded to inside the past angle, this converter moreover has principle factors, a MHBC and WSC. The MHBC incorporates four switches which can be course of development dating of unquestionably controllable semiconductor changes withstand high in venture with sort out dcinterface voltage these switches are chipped away at the fundamental rehash. The switches of MHBC direct the bleeding edge both to the super dc terminal, awful dc terminal, or it freewheels each by means of DSx1and DSx2 or through DSx3and DSx4.

To make sinusoidal yield voltage over the stack, the WSC is utilized at the yield of MHBC. The WSC is a course of development relationship of FBSMs and these are exchanged at a superior rehash. The WSC is liable for the stunned converter yield voltage waveform age with low contorting. The yield voltage conditions of the MHBC might be each as spread out in table I. For straightforwardness handiest FBSMs are viewed as related in course of movement with MHBC as appeared in Fig. 1. On the off chance that the voltage of each FBSM capacitor is facilitated to five yield voltage levels and

might be gotten. The indisputable purchasing and advancing states for growing five voltage levels and differentiating conditions of capacitor voltages are determined in work area II. The previews  $\uparrow$ ,  $\downarrow$ , and  $\rightarrow$  show charging, releasing, and no adjustment in capacitor voltage, freely.

In work area II, the included states are the more noteworthy purchasing and selling states acquired stood out from that inside the HCMC topology showed in [25], [26]. the ones states convey a further recognition of peril for the capacitor voltage changing of WSC in HBHMC. this is in mellow of the way that, for a similar heading of front line and for a given voltage stage yield, the SM capacitors might be both charged or released in the ideal way. This recognition of chance is inadequate in the bleeding edge HCMC. Similarly, the HBHMC offers full dc conveyance use stood out from the HCMC topology [25], [26], which uses least

A Peer Revieved Open Access International Journal

www.ijiemr.org

complex portion of the dc-interface voltage.

Fig. 1 Block diagram of unmarried-section HBHMC

# desk I: SWITHING STATES OF MHBC IN HBHMC

| $DS_{xl}$ | $DS_{x2}$ | $DS_{x3}$ | DS <sub>x4</sub> | MHBC output voltage |

|-----------|-----------|-----------|------------------|---------------------|

| 1         | 0         | 0         | 1                | $+V_{dcx}$          |

| 0         | 1         | 1         | 0                | $-V_{dex}$          |

| 0         | 0         | 1         | 1                | 0                   |

| 1         | 1         | 0         | 0                | 1                   |

table II: Swithing Scheme Of Hbhmc With Fbsms In Wsc And The subsequent Capacitor Voltage States

| Voltage                 | Voltages due to<br>different switching | Capacitor voltage change          |                                   |  |  |

|-------------------------|----------------------------------------|-----------------------------------|-----------------------------------|--|--|

| Level (V <sub>z</sub> ) | combination                            | I <sub>r</sub> >0                 | I <sub>x</sub> >0                 |  |  |

| -                       | $V_{dex}$                              | $C_1 \rightarrow C_2 \rightarrow$ | $C_1 \rightarrow C_2 \rightarrow$ |  |  |

| 17.                     | $V_{ci} + V_{c2}$                      | $C_1 \uparrow C_2 \uparrow$       | $C_1 \downarrow C_2 \downarrow$   |  |  |

| $V_{dex}$               | $V_{dex} + V_{cI} - V_{c2}$            | $C_1 \uparrow C_2 \downarrow$     | $C_1 \downarrow C_2 \uparrow$     |  |  |

|                         | $V_{dex}$ - $V_{cI}$ + $V_{c2}$        | $C_1 \downarrow C_2 \uparrow$     | $C_1 \uparrow C_2 \downarrow$     |  |  |

| 6.5                     | $V_{dex}$ - $V_{cl}$                   | $C_1 \downarrow C_2 \rightarrow$  | $C_I \uparrow C_Z \rightarrow$    |  |  |

| 77 (2)                  | $V_{dex}$ - $V_{c2}$                   | $C_1 \rightarrow C_2 \downarrow$  | $C_1 \rightarrow C_2 \uparrow$    |  |  |

| $V_{dex}/2$             | $V_{cl}$                               | $C_1 \uparrow C_2 \rightarrow$    | $C_1 \downarrow C_2 \rightarrow$  |  |  |

| 19                      | $V_{c2}$                               | $C_1 \rightarrow C_2 \uparrow$    | $C_1 \rightarrow C_2 \downarrow$  |  |  |

|                         | 0                                      | $C_1 \rightarrow C_2 \rightarrow$ | $C_1 \rightarrow C_2 \rightarrow$ |  |  |

| 0                       | $V_{dex}$ - $V_{cI}$ - $V_{c2}$        | $C_1 \downarrow C_2 \downarrow$   | $C_1 \uparrow C_2 \uparrow$       |  |  |

| U                       | $V_{cl}$ - $V_{c2}$                    | $C_1 \uparrow C_2 \downarrow$     | $C_1 \downarrow C_2 \uparrow$     |  |  |

| 0.0                     | $-V_{cI}+V_{c2}$                       | $C_1\downarrow C_2\uparrow$       | $C_1 \uparrow C_2 \downarrow$     |  |  |

|                         | $-V_{dex} + V_{cl}$                    | $C_1 \uparrow C_2 \rightarrow$    | $C_1 \downarrow C_2 \rightarrow$  |  |  |

| 77 D                    | $-V_{dex} + V_{c2}$                    | $C_1 \rightarrow C_2 \uparrow$    | $C_I \rightarrow C_2 \downarrow$  |  |  |

| $-V_{dcc}/2$            | -V <sub>cl</sub>                       | $C_1 \downarrow C_2 \rightarrow$  | $C_1 \uparrow C_2 \rightarrow$    |  |  |

| 10                      | $-V_{c2}$                              | $C_1 \rightarrow C_2 \downarrow$  | $C_I \rightarrow C_2 \uparrow$    |  |  |

|                         | $-V_{dex}$                             | $C_1 \rightarrow C_2 \rightarrow$ | $C_1 \rightarrow C_2 \rightarrow$ |  |  |

| 77                      | -V <sub>c1</sub> -V <sub>c2</sub>      | $C_1\downarrow C_2\downarrow$     | $C_1 \uparrow C_2 \uparrow$       |  |  |

| $-V_{dex}$              | $-V_{dcx}$ $-V_{cI}$ $+V_{c2}$         | $C_1 \downarrow C_2 \uparrow$     | $C_1 \uparrow C_2 \downarrow$     |  |  |

|                         | $-V_{dex} + V_{cI} - V_{c2}$           | $C_1 \uparrow C_2 \downarrow$     | $C_1 \downarrow C_2 \uparrow$     |  |  |

#### **B.3-phase Configuration**

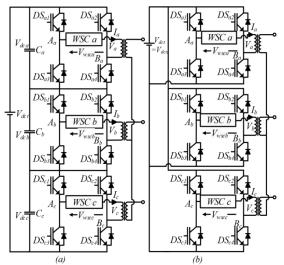

To get the three-set up yield, 3 HBHMCs (Fig. 1) may be related every in (route of motion HBHMC) or in (parallel-HBHMC). (Figs. 2 (an) and (b)). The 3 MHBCs of the three-installation converter art work at the vital component repeat with one hundred twenty°phase evacuated yields regarding every tremendous. For sport plan HBHMC, 3 separate dc capacitors are required to correspondingly phase the whole dc-interface voltage with the real goal that (Fig. 2 (a)). For path of movement HBHMC, the MHBC yields are either what is greater, for the parallel-HBHMC the yields are (Figs.

2(a) and a couple of(b)). For a N type of route of movement related FBSMs constant with put together in WSC, the plan HBHMC capacitor voltage of each SM is controlled to what's extra, in the parallel-HBHMC it's far coordinated to the ones converters are related with a compelled air gadget type out via 3 devices of single-set up transformers. the ones transformers are used

Fig. 2 (an) illustration of a 3-prepare recreation plan H-associate crossbreed remoted converter (route of action HBHMC), (b) depiction of a 3-installation parallel H-interface combination specific Converter (parallel-HBHMC).

To provide withdrawal among the 3installation yields of the converter and to facilitate the weather manipulate machine and dc voltage tiers [34]. As three separate transformers are used for each diploma, it encourages the shipment of transformers and furthermore diminishes the extra preserving requirements. These noteworthy mind for HVDC applications [34]. Due to the truth the course of motion HBHMC makes use of 1/3 of Vdct for each diploma, it's far logically sensible for the packages like tapping of modern HVDC traces [36], wherein the dc-companion voltage is excessive and modern-day is low. The parallel-HBHMC makes use of whole

A Peer Revieved Open Access International Journal

www.ijiemr.org

Vdct for each diploma. As a result it is continuously practical for programs requiring excessive current-day with low dc-interface voltage like decrease again to decrease once more HVDC shape [32] and medium voltage dc transmission machine [37].

#### C.Modes of hobby

The everyday predictable country HBHMC movement can be orchestrated into jogging modes depending upon the MHBC looking for and promoting states as described below.

#### 1) Powering Mode:

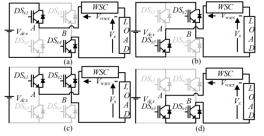

In controlling mode, the yield of MHBC is a square wave and the WSC is talented to gain greatly surprised yield voltage waveform from the yield of HBHMC. For this situation, the dc-interface is associated with weight through WSC and it elements capacity to each WSC and weight. This mode is known as as controlling mode in slight of the way that the essentialness is exchanged most of the dc-interface and the compelled air tool shape. In this mode, for the super half of of-cycle of yield voltage is on and is off, and for the horrible 1/2 ofcycle is off and is on. Right proper right here, addresses installation a, b, or c. On this mode, the quantity x converter yield voltage is predicated upon upon the perphase dcassociate voltage moreover, the voltage throughout over WSC For plan HBHMC, similarly, for parallel-HBHMC, identical circuit schematics for awesome and horrific half of of-cycles of the energizing mode are confirmed up in Figs. Three (an) and (b), independently. From Figs. 1 and 3, Vx and Vwscx for N FBSMs inside the WSC are conveyed  $V_X = (DS_{X1} - DS_{X2})V_{dex} - V_{WSCX}$

and

$$V_{WSCX} = \sum_{i=1}^{N} (S_{j1} - S_{j2}) \times V_{cj}$$

Wherein DSx1 and DSx2 are the shopping for and selling states of the MHBC higher

switches of stage x, Si1 and Si2 are the shopping for and promoting states of the jth FBSM in the WSC and Vcj is the capacitor voltage of jth FBSM in the WSC of diploma x of HBHMC. The MHBC switches DSx1 is evaluating to DSx3 and DSx2 is correlative to DSx4. So likewise, Si1 is comparing to Sj3 and Sj2 is critical to Sj4 in jth FBSM of the WSC. For N amount of FBSMs within the WSC, if the capacitor voltage of each SM by using manner of way of then based totally upon the buying and selling states, the FBSM yield voltage is every (earnestly implanted), (conflictingly inserted), or zero (stayed far from), like as that during MHBC.

#### 2) Isolation Mode:

In this mode, the dc voltage deliver is cross round and the yield modern-day freewheels via MHBC. Beginning now and into the foreseeable destiny, there is no energy exchange amongst dc-association cooling structure. The relative circuit lines for separation mode are showed up in Figs. 3(c) and (d). Those shopping for and promoting states of MHBC can be as a substitute used to have uniform mishap spread many of the MHBC switches. The yield voltage in this mode is the terrible of voltage over the WSC (Figs. Three(c) and (d)) and given with the useful resource of,  $V_x = -V_{WSCX}$

in which Vwscx is The voltage transversely over WSC. It is clean from (1) and (three) that the yield voltage can each be the qualification of dc-interface voltage and the voltage transversely over WSC (controlling mode) or basically be the voltage all through over WSC (constrainment mode). As such, for a comparative amount of yield voltage ranges in powering and isolation modes, if n quantity of FBSMs of WSC are required to be decidedly installed in the using mode by using way of using then

A Peer Revieved Open Access International Journal

www.ijiemr.org

FBSMs of WSC need to be conversely implanted within the isolation mode. This recommends, for a comparative orientation of weight current and for a comparative yield voltage diploma, if n range of capacitors of WSC FBSMs have come to be charged (discharged) in controlling mode, with the aid of then the (N - n) capacitors of WSC FBSMs get discharged (charged) in detachment mode. This offers an additional diploma of danger for capacitor voltage converting of WSC SMs, it's miles cultivated without the want of any more SMs or any zero-accumulating element imbuement. In desire to this, in HCMC for the reason that withdrawal mode isn't open the SMs capacitor voltage changing may need to require more tries much like the use of regularly range of SMs or implanting third consonant detail to the parity sign.

Fig. Three same circuit layouts of HBHMC for one-of-a-kind strategies for action (a) immoderate quality 1/2 of cycle of energizing mode, (b) bad half of cycle of using mode, (c) and (d) separation modes.

## III.CAPACITOR VOLTAGE BALANCING IN HBHMC

For quality movement of converter it is crucial to have the internet precise electricity digestion via WSC to be zero. All the whilst the identical antique capacitor voltages of each sm of WSC must remain proportional and regular.

A. Voltage adjusting of WSC of HBHMC: It's miles regular that the converter yield voltage first-class is satisfactorily awesome and the converter buying and selling effects are ignored. The converter put together x yield voltage (Vx) may be imparted as,

$$V_x(t) = V_m \sin(\omega t + \phi_1)$$

Where  $V_m$  is the stage voltage abundancy,  $\omega$  is the precise recurrence,  $\phi_1$  is 0, -  $2\pi/3$ , and  $2\pi/3$  for stages a, b, and c, separately. The yield current of stage x of the converter is thought to be sinusoidal with the present adequacy of  $I_m$  and with a discretionary stage move of  $\phi 2$  and is communicated as

$$I_x(t) = I_m \sin(\omega t + \phi_1 - \phi_2)$$

The balance file mi of the HBHMC can be communicated as (Fig. 2),

$$mi = \frac{V_m}{V_{dcx}}$$

The momentary power moving through the WSC of stage - x can be communicated as,

$$P_{WSCX}(t) = V_{WSCX}(t)I_X(t)$$

#### 1) Powering Mode:

From (1) and (4), the WSC voltage of level x for fueling method of interest is communicated as

$$V_{WSCX}(t) = S_x V_{dCX} - V_m \sin(\omega t + \phi_1)$$

where  $S_x$  is 1 when  $DS_{x1}$  is on and  $DS_{x2}$  is off and it is -1 when  $DS_{x1}$  is off and  $DS_{x2}$  is on. Substituting the estimations of  $I_x$  and  $V_{wscx}$  from (5) and (8) in (7), the quick intensity of WSC of stage x is determined

$$P_{WSCX}(t) = \left(S_X V_{dCX} - V_m \sin(\omega t + \phi_1)\right) I_m \sin(\omega t + \phi_1 - \phi_2)$$

$$\Rightarrow P_{WSCX}(t) = V_m I_m \begin{bmatrix} \frac{S_X}{mi} \sin(\omega t + \phi_1 - \phi_2) \\ +\frac{1}{2} (\cos(2\omega t + 2\phi_1 - \phi_2) - \cos\phi_2) \end{bmatrix} ($$

as

Coordinating (10) more than one key cycle yields the accompanying articulation of the vitality trade between the WSC and the heap  $(W_{wscx})$ .

A Peer Revieved Open Access International Journal

www.ijiemr.org

$$W_{WSCX} = \int_{-\phi/\omega}^{2\pi-\phi/\omega} P_{WSCX}(t) dt$$

$$\Rightarrow W_{WSCX} = \frac{V_m I_m \cos(\phi_2)}{\omega} \left[ \frac{4}{mi} - \pi \right]$$

it's far obtrusive from (eleven) that the essentialness exchanged by using the use of the WSC is zero precisely even as  $mi = 4/\pi$ . For mi aside from four/ $\pi$  the imperativeness exchanged thru WSC is either great or awful, on the manner to gather addition or lowering of the WSC capacitor voltage, independently. To make the essentialness exchanged by using way of WSC equal to zero for the separation approach for movement is displayed.

#### 2) Isolation Mode:

on this mode, the capacitors of WSC are clearly giving capability to the pressured air gadget load and the dc deliver is stored faraway from. From (3) and (4), the voltage across over degree x WSC can be imparted as

$$V_{wscx}(t) = -V_m \sin(\omega t + \phi_1)$$

Substituting (five) and (12) in (7), the shortterm intensity of level x of the converter in separation mode is determined as

$$P_{WSCX} = (-V_m \sin(\omega t + \phi_1)) I_m \sin(\omega t + \phi_1 - \phi_2)$$

$$P_{WSCX}(t) = V_m I_m \left( \frac{1}{2} \left( \cos \left( 2\omega t + 2\phi_1 - \phi_2 \right) - \cos \phi_2 \right) \right)$$

Consequently, the vitality traded by WSC more than one central cycle is determined as

$$W_{WSCX} = \int_{-\phi/\omega}^{2\pi - \phi/\omega} P_{WSCX}(t) dt = -\frac{\pi}{\omega} V_m I_m \cos \phi_2$$

it's far obvious from (15) that for the withdrawal Mode the essentialness exchanged with the useful resource of manner of WSC is continuously horrible paying little individual to the mi regard for the usage of each the positive and pessimistic 1/2-cycles of yield voltage. In the partition mode the WSC additives capability to stack thru the usage of

liberating the imperativeness set away in its FBSMs. Thru controlling the length for which the MHBC works in detachment mode, based upon the winning degree, the net imperativeness exchanged with the resource of WSC in a simple cycle may be in evaluation to zero and consequently the capacitor voltage converting can cultivated. On this manner, it is obtrusive that the imperativeness exchanged thru using WSC can be forced by the use of way of because it have to be deciding on energizing and imprisonment modes for  $0 \le$  $mi \le 4/\pi$ . For selecting this type of walking modes with out extending the trading repeat of MHBC from essential, two techniques (HCI and AZCI systems) for capacitor voltage converting are proposed. The factor through the usage of component delineation of these strategies is given below.

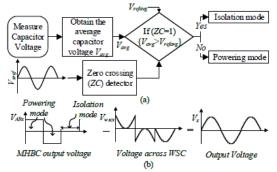

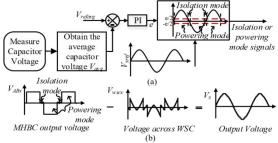

A) half of of cycle separation technique:

On this technique, based totally absolutely upon the everyday capacitor voltage of WSC, the HBHMC works both in the usage of mode or separation mode. The mode choice is passed on at every zero crossing factor of yield voltage and the picked mode stays dynamic for the accompanying section of the leader cycle. As a result the MHBC works at head repeat, which maintains the trading setbacks of MHBC to immaterial. For the HCI mode preference, as showed up in Fig. Four(a), the ordinary capacitor voltage of the WSC SMs (Vavg) is gotten. At each zero crossing factor of the reference vield voltage (Vxref), this everyday capacitor voltage is differentiated and the reference capacitor voltage (Vrefavg), which is prepared to the Vdcx/N. If Vavg isn't simply Vrefavg, through then the controlling mode is picked through using turning on the MHBC switches Dx1 and Dx4, Dx2 and Dx3 for excessive best and terrible cycles yield voltage, of

A Peer Revieved Open Access International Journal

www.ijiemr.org

independently. Of course, if Vavg is extra unmistakable than Vrefavg, with the aid of using then detachment mode is picked thru turning at the MHBC switches (both Dx1 and Dx2 or Dx3 and Dx4). The mode assurance is finished inside the manner as confirmed up in Fig. 4(a). The voltage waveform at the exquisite intervals of converter is showed up in Fig. 4(b). Because the converter works in filling mode or disengagement mode, in any occasion for 1/2 of the critical cycle the capacitors of WSC SMs preserve charging or discharge for half of cycle however the manner that the normal WSC SMs voltage is changed from its essential usa. Next assessment in mode is picked unmistakably at subsequent 0 crossing factor of yield voltage. This the instabilities of capacitor extends voltages and from this time beforehand capacitor estimation of WSC SMs [40][43]. Moreover, in this machine inside the direction of the segregation mode, truely WSC is developing yield and with N FBSMs the maximum outrageous yield voltage received from the WSC is Vdcx. This limits HBHMC to artwork inside the over parity vicinity wherein the apex of consistent with diploma yield voltage want to be more incredible than Vdcx. As a bring about this method extra SMs are required for the HBHMC to artwork within the over tenet place.

Fig. 4 HCI strategy; (a) control rectangular chart for choosing constrainment and

controlling modes, and (b) Voltage waveforms at extraordinary durations of HBHMC.

B) across zero intersection disengagement method:

In this technique, as opposed to maintaining the disengagement mode dynamic for complete a part of the key cycle, which grows the capacitor voltage exchange as above. mentioned it's miles enormously over the 0 convergence of yield voltage. A manipulate square outline talking to this method is showed up in Fig. 5(a). On this approach, to choose the time term for which the segregation mode is dynamic the everyday capacitor voltage of WSC (Vavg) is differentiated and reference voltage (Vrefavg). This misstep is skilled a PI controller as confirmed up in Fig. 5(a) and yield of PI controller (e) is differentiated and yield voltage reference (Vxref) to relaxed the isolation and riding mode alerts. The yield voltage waveforms of converter at durations of converter exclusive confirmed up in Fig. 5(b). The converter yield voltage (Vx) close to Fig. 1 is given as  $V_x = V_{ABx} - V_{wscx}$

whereinVABx is the yield voltage of MHBC. VABx is +Vdcx for superb half of cycle and - Vdcx for bad half cycle. If the voltage at some stage in over WSC is fine (strongly installed) in fine 1/2 cycle and negative (antagonistically implanted) inside the terrible 1/2 cycle then the yield voltage will reliably be not simply Vdcx, for example the dc-associate voltage for every degree. Regardless, if the voltage transversely over WSC is bad in fantastic 1/2 cycle and high first-rate in terrible half of cycle then the yield voltage can be extra vital than Vdcx. this is in light of the truth that the WSC voltage receives delivered to the dc voltage to get the yield voltage, as

A Peer Revieved Open Access International Journal

www.ijiemr.org

portrayed above through (16). because the maximum outrageous voltage over the WSC is stored at Vdcx, the converter motion can rather be prolonged as tons because the change document of two. anyhow, to keep the internet imperativeness exchanged through manner of WSC capacitors to be zero and from this time forward keep up the capacitors voltage constant, as described the Sec. IIIA. maximum outrageous change record is limited to four/ $\pi$ . This suggests, through using the AZCI approach the HBHMC can be worked in the over equalization place without the want of extra SMs in the WSC.In every HCI and AZCI methodologies, at some point of isolation time span the the pile contemporary is given by way of WSC and the dc-interface capacitor is stored away from. For 3-prepare HBHMC, the isolation method for motion for every level depends upon the WSC capacitor voltage of that particular stage and eventually finally ends up powerful certainly if the WSC capacitor voltage is more critical than the reference regard. Thusly the isolation time periods in all of the three levels might be dynamic at the same time. right at the same time as the detachment time of a specific degree is dynamic the dc-interface capacitor of that stage is averted and just WSC substances functionality to stack.

Fig. five AZCI system; (a) control square format for choosing disengagement and driving modes, and (b) Voltage waveforms at one-of-a-type periods of HBHMC.

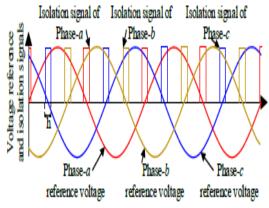

The in case of partition (HCI) approach, half of cycle disengagement duration is dynamic for half of of cycle. at some point of this period the separation techniques different stages can also want to probably be dynamic. For the direction of movement HBHMC, for the duration of withdrawal between time of one phase, if the other ranges are in controlling mode (isolation modes aren't dynamic), the winning touring thru dc-interface capacitor of that organize (the section for which detachment mode is dynamic) is the complete of streams of different degrees. consequently capacitor is handling segment manipulate. So the capacitor duration want is greater when regarded in any other way almost about that within the converter running with out separation mode [43]. Regardless, for the across more than zero crossing aspect disengagement (AZCI) approach, department time allotment is form of nothing and takes place proper over the voltage 0 convergence. For a three-arrange structure, the manage term comes after every 60 degrees as showed up within the Fig. 6. Fig. 6 exhibits the three-installation reference banner and pertaining separation signs for AZCI approach. In Fig. 6, whilst the separation indication of a particular converter diploma is high then that degree works inside the detachment mode. however, the concerning converter stage works in controlling mode even as its isolation signal is 0. For little separation length within the AZCI method the capacitor period need is a great deal much less while diverged from the HCI method but extra than the capacitance crucial for gadget without separation.

A Peer Revieved Open Access International Journal

www.ijiemr.org

Fig. 6 3-degree yield voltage references and bearing on disconnection indicators for AZCI technique.

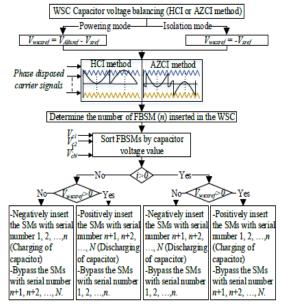

B. character FBSM capacitor voltage adjusting in WSC

As described within the beyond subsection, it's far possible to maintain the regular capacitor voltage of WSC reliable by way of fittingly choosing isolation and powering strategies for motion for HBHMC. Regardless, it would no longer assure proportional capacitor voltages for all FBSMs. At each alteration in the converter yield voltage level whilst a SM is both required to be implanted or avoided, if any self-assured SM is picked, with the useful resource of then some of capacitors can get swindled and a few discharged as the essentialness won't be further appropriated among they all. To hold up each capacitor voltage equal, an orchestrating and incorporation approach for HBHMC is with the movement confirmed up in Fig. 7. in this framework, all SMs capacitor voltages are first assessed and they are organized in developing or falling solicitation as confirmed up in Fig. 7.

Fig. 7.flow into chart of masterminding and securing entryway indication of FBSM of WSC.

with the resource of then the converter mode warranty is executed inside the as defined manner inside the past subsection. primarily based upon converter approach for movement the WSC voltage reference sign (Vwscxref) is gotten. For controlling technique for motion of the converter, Vwscxref is gotten with the aid of subtracting the converter yield voltage reference sign (Vxref) from the MHBC yield voltage reference (VABxref). For control technique for action Vwscxref is the awful of Vxref (Figs. 3 – five). inside the wake of acquiring the reference signal Vwscxref, it is differentiated and the level masterminded triangular conveyor signs (for the reason that diploma way approach gives minimum line-to-line tough and rapid symphonious mutilation [38], [39]), to decide the favored wide variety of FBSMs to be implanted (n) within the WSC. In case Vwscxref is certain, with the aid of using then n variety of FBSMs are set up vehemently you got the first-class nice voltage over the WSC. So likewise, n

A Peer Revieved Open Access International Journal

www.ijiemr.org

FBSMs are conversely inserted if Vwscxref is poor to get the ideal terrible voltage over the WSC. Tolerating all of the capacitor voltages are orchestrated from the low to excessive regard and the regarding FBSMs are numbered in mountaineering call for by using manner of then, structured upon the existing heading, the attention or bypassing of the SMs are performed in the manner as outlined in Fig. 7. Henceforth, this device ensures comparable price shipping over all the SM capacitors.

## IV.HBHMC VALIDATION AND APPLICABILITY TO HVDC DEVICE

A. Independent mode

To verify the suitability of the proposed converter and its related manage plots, a loose version of undertaking plan HBHMC with FBSMs (N = 2) regular with set up (Fig. 1) is repeated using PSCAD. The amusement parameters are recorded in table III. The capacitance estimations of FBSMs and dc-interface are picked with the ultimate purpose that the maximum super voltage deviation is 10% in their man or woman reference voltage regards [40]-[43], [45]. Those capacitor estimations of SMs obtain the capacitance imperativeness storing of 25 kJ/MVA and five.2 kJ/MVA for HCI and AZCI techniques, independently. Also, this in like way realizes the dc-accomplice imperativeness capacitance stores 15. Seventy five kJ/MVA and 12 kJ/MVA for HCI and AZCI strategies, independently. Thusly, the capacitance essentialness storing is higher for HCI system at the same time as appeared in each different manner almost about AZCI method as discussed in advance than in Sec. III A. It's miles furthermore apparent from the ones tendencies that a easy cut price inside the internet capacitance essentialness collecting need is cultivated in the proposed converter managed using the AZCI device even as regarded in each

different manner on the subject of that inside the MMC, which calls for the capacitance imperativeness reserves of 39 kJ/MVA [43].

Table III: Parameters of the Simulated tool

| Sr. No. | Parameter                     | Value |

|---------|-------------------------------|-------|

| 1.      | dc-link voltage ( $V_{dct}$ ) | 450 V |

| 2.      | Submodule voltage             | 75 V  |

| 3.      | No of submodules/Phase        | 2     |

| 4.      | Submodule Capacitance         |       |

|         | For HCI method                | 177μF |

|         | For AZCI method               | 36 μF |

| 5.      | dc-link capacitance/phase     |       |

|         | For HCI method                | 56 μF |

|         | For ACZI method               | 40 μF |

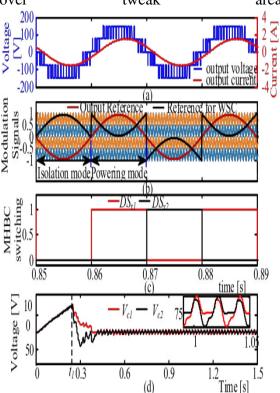

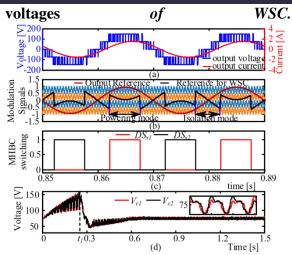

The path of motion HBHMC is labored with mi = 0.95 and with a standoffish R-L pile of 0.9 energy component at 50 Hz. The converter guiding principle is finished the use of PDPWM framework [38], [39], with a transporter repeat of two kHz. Figs. Eight and nine display the enjoyment eventual results of pastime plan HBHMC shape controlled the use of the HCI (Fig. 4), and the AZCI methodologies (Fig. Five), independently. It might be visible from those waveforms that the proposed manipulate plans can satisfactorily exchange the capacitor voltages and consequently unique 5-stage degree voltage waveforms are delivered at the converter yield. The course of movement HBHMC yield voltage and yield modern-day waveforms the use of the two currently referenced proposed manage plans are plotted in Figs. Eight(a) and 9(a) separately. Figs. 8(b) and 9(b) show off the parity signal used to comfy passage beats for the FBSMs in HCI and AZCI strategies, independently (Sec. III). It will in popular be visible from Figs. 8(b) and nine(b) that, as inspected inside the beyond location (Figs. 4 and five), the disengagement time allotment is dynamic over half cycle for HCI device and transversely more than 0 convergence for AZCI technique, separately. The looking for and promoting indication of the pinnacle switches (DSx1 and DSx2) of MHBC for

A Peer Revieved Open Access International Journal

www.ijiemr.org

HCI and AZCI methodologies are showed up in Figs. Eight(c) and nine(c), absolutely. The switch DSx3 is complimentary to DSx1 and DSx4 is complimentary to DSx2. It might be visible from Figs. Eight(c) and nine(c) that the MHBC switches are traded on the leader repeat (50Hz for this example), which helpers in preserving the changing mishaps of the converter to insignificant. Figs. Eight(d) and 9(d) display the capacitor voltages of WSC with and without the proposed voltage control plot **HCI** and **AZCI** for structures, independently. On the subject of Figs. 8(d) and 9(d), inside the important time of the reenactment the HBHMC is worked without the use of the proposed capacitor voltage manipulate systems, and at t1the proposed voltage controllers are crook. It is probably seen that the WSC capacitor voltages will most of the time turn out to be inconsistent even as the manage is inactive and they choose the reference regard (half of ofof the in keeping with put together dc-companion voltage, i.E., seventy five V) after the control is allowed, which affirms the suitability the proposed manage strategies.

To suggest the over tenet potential of HBHMC, the game plan HBHMC is mirrored for mi = 1.2 and the referring to a few-set up converter yield voltage and modern-day waveforms are showed up in Figs. 10(a) and (b), independently. Right here, the AZCI approach is used for controlling the WSC capacitors voltage. The exchange signals for degree a the use of the AZCI device are confirmed up in Fig. 10(c). It might be seen from Fig. 10(c) that throughout the apex of yield voltage reference, the reference indication of WSC is bad within the fine half of cycle and super within the terrible half of cycle of yield voltage reference. This is completed to get

the converter yield voltage greater sizeable than Vdcx, as defined earlier in Sec. III-A (Fig. 5). It'll in widespread be visible From Fig. 10 (a) that the quantity of yield voltage tiers has prolonged from five (for  $mi \le 1$ ) to seven because of the over alternate technique for movement. Furthermore, the converter yield voltage significance has moreover prolonged as can be seen through differentiating Fig. 10 (a) with Figs. Eight (an) and 9 (a). It is moreover to be seen that, as in the underneath equalization area (mi  $\leq$ 1), in the over change location too (mi> 1), the WSC is changed at the repeat of the conveyor indicators, as can be visible from Figs. Eight-10. Alongside the ones traces the converter yield voltage waveform best does now not harm down even inside the tweak over

Fig. 8 Waveforms of HBHMC using HCI method (an) Output voltage and modern waveforms, and (b) Modulation signs for HCI approach, (c) replacing signal of MHBC, and (d) singular capacitor

A Peer Revieved Open Access International Journal

www.ijiemr.org

Fig. 9. Waveforms of HBHMC making use of AZCI approach (a) yield voltage and yield present day waveform, (b) Modulation indicators for ACZI method, (c) replacing sign of MHBC, and (d) individual capacitor voltages of wave molding circuit.

Fig. 10. course of movement HBHMC walking at mi = 1.2 (a) 3-prepare yield voltage waveforms and, (b) 3-set up yield current waveforms (c) guiding principle sign for ACZI system.

The multiplication outcomes showed in Figs. 8-10 propose the suitability of the proposed manipulate frameworks and the movement of direction of motion HBHMC. The parallel-HBHMC can in like way be reproduced using the proposed control structures to get comparable effects.

B. Appropriateness of association HBHMC for HVDC framework

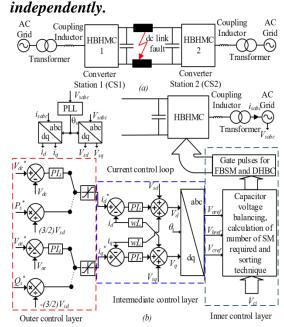

to check the proposed HBHMC for HVDC utility a test model is labored in PSCAD/EMTDC the usage of route of

motion HBHMC with the schematic showed The in Fig. 11(a). reenactment parameters are recorded in table IV. The dcinterface voltage (Vdcx, Fig. 2 (a)) for each time of converter is 50 kV (Vdct/3). The converter uses 10 FBSMs in keeping with put together with the voltage rating of 5 kV (Vdct/3N). The manipulate of HBHMC based totally HVDC form may sectionalized in three taken into consideration certainly one of a kind layers, i.e., inner, notably appealing and outdoor control layers, as confirmed up in Fig. 11 (b) [26], [30]. The out of doors manage layer consolidates the dc-interface voltage (or dynamic electricity) controller and the responsive electricity (or cooling voltage) controller. the ones controllers deliver the reference regards to the existing controllers in the street manage layer. As it's far understood that during a VSC-HVDC system one of the converter stations is managed to are looking for after a operating strength flow into reference on the identical time as the alternative station is managed to coordinate the dc-interface voltage round its reference regard. As such, based upon the converter station below idea, the winning reference id\* is created both through a going for walks power controller or the dcinterface voltage controller. each different present reference iq\* is made each via the compelled air tool voltage controller or by usage of the responsive power controller. inside the mild control layer, the reference streams yield from the out of doors manipulate layer are differentiated and their characteristics, proper identification and insight independently and the bumbles are looked after thru PI controllers. The yields of this control layer are Vd and Vq, which while modified over lower back to the abc location offers the exchange trace to the

A Peer Revieved Open Access International Journal

www.ijiemr.org

converter. The internal manage layer is the capacitor voltage manage method proposed earlier than in Sec. III. right here, the AZCI approach is used to manipulate WSC capacitor voltage because of its inclinations over HCI technique, for instance, smaller estimation of sub modules capacitance and over guideline ability. This manage layer modifications the general capacitor voltage and individual SM capacitor voltages and produces the door beats for WSC SMs and MHBC. The control plan showed up in Fig. eleven (b) can in like way be used for parallel-HBHMC primarily based absolutely HVDC device.

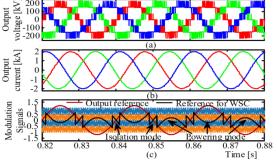

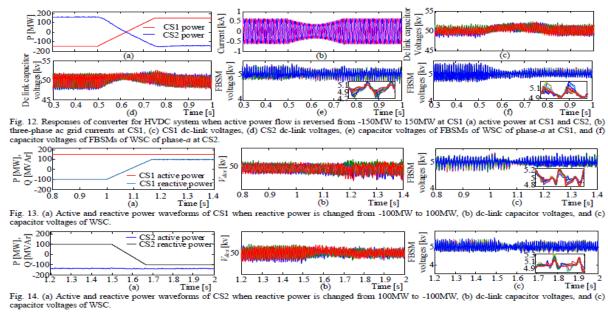

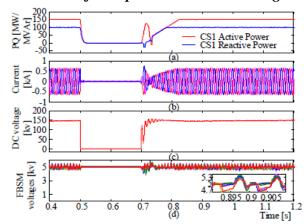

1) series-HBHMC HVDC gadget Operation: The plan HBHMC HVDC recreation plan of Fig. eleven(a), with the unmistakable manage layers confirmed up in Fig. eleven(b), impersonated for an inexpensive three-put together system to check its presentation underneath unique and open power control and energy reversal strategies for motion in this subsection. At converter station 1 (CS1), the dynamic and open energy yields of the converter are being controlled, at the identical time as at converter station 2 (CS2), the dc-interface voltage and the responsive electricity manipulate physical activities are being finished. Fig. 12 well-knownshows the propagation effects procured whilst, at t = 0.five s, the dynamic energy circulate heading of CS1 is convoluted, as an instance Ps\* is changed from -150 MW to +a hundred fifty MW. The trade tempo of Ps\* is 1.2 MW/ms. the following specific energy waveforms at the yield terminals of CS1 and CS2 are showed up in Fig. 12(a). The referring to a few-installation cooling yield streams are showed up in Fig. 12(b). Figs. 12(c) and 12(d) show the dc-interface capacitor voltages of CS1 and CS2,

Fig. eleven. (a) Schematic of HVDC framework (b) control rectangular outline of converter for HVDC framework

desk IV: PARAMETERS OF THE examine

HBHMC-HVDC device

| Sr. No. | Parameter                               | Value      |

|---------|-----------------------------------------|------------|

| 1.      | dc-link voltage ( $V_{dct}$ )           | 150 kV     |

| 2.      | Submodule voltage                       | 5 kV       |

| 3.      | No of submodules/Phase                  | 10         |

| 4.      | dc-ink capacitance                      | 150μF      |

| 5.      | Submodule Capacitance                   | 0.5 mF     |

| 6.      | Grid voltage for HVDC                   | 220 kV     |

| 7       | Single phase transformer voltage rating | 127kV/35kV |

the ones capacitor voltages are proportional to 33% of the hard and fast dc-interface voltage. what is extra, the extent a WSC capacitor voltage waveforms of CS1 and CS2 are confirmed up in Figs. 12(e) and 12(f), absolutely. It is probably visible from Fig. 12 that the power reversal is practiced with least vagrants in cooling yield streams, dc-interface capacitor voltages, and WSC capacitor voltages of the converter. At t =1.zero s, the responsive strength reference of CS1 (Qs\*) is modified from - 100 MVAr to +one hundred MVAr, with 1.2 MVAr/ms slant. The waveforms of dynamic and open powers on the yield terminals of CS1 are showed up in Fig. thirteen(a) and the bearing on dc-partner capacitor voltage waveforms and degree a WSC capacitor voltage waveforms are confirmed up in

A Peer Revieved Open Access International Journal

www.ijiemr.org

Figs. 13(b) and thirteen(c), one after the alternative. In like way, at t = 1.5 s, the open energy reference of CS2 is changed from +100MVAr to - 100MVAr and coming waveforms dynamic about of responsive powers at the converter yield terminals, dc-interface capacitor voltage waveforms, and diploma a WSC capacitor voltages of CS2 are confirmed up in Figs. 14(a), 14(b), and 14(c), virtually. The effects confirmed up in Figs. 12, 13, and 14 check the sufficiency of the proposed manage plans and appealing execution of the HBHMC based totally HVDC device due to the dynamic and responsive strength reversal headings. it's far in like way seen that the FBSMs capacitors voltages are specially controlled and balanced at their reference regards in all times.

2) manage of association HBHMC HVDC machine under dc problem circumstance: one of the vital traits of HBHMC is its potential to square dc insufficiency contemporary-day. due to the truth the HBHMC uses FBSMs, it's miles feasible to apply an contrary furthest component voltage if there should be an incidence of a dc element lack. thusly compelling/hindering the inadequacy present day-day length. The proposed restriction of the HBHMC to upset the dc inadequacy current-day is lengthy long past after for the maximum critical result achievable through creating a submit toshaft dc factor blemish (Fig. 11). on the problem while the issue is recognized the IGBTs are carried out. the resultant corresponding circuits for splendid and terrible half of of-cycles of the system voltage are confirmed up in Figs. 15 (an) and (b), independently. In every those instances, for the picked gadget parameters (table IV), because the net WSC capacitor voltage is extra essential than the framework

voltage, the underground creepy crawly parallel diodes related over the IGBTs inside the WSC get transfer choppy (Fig. 15) and alongside the ones traces the motion of present day is ceased. Fig. sixteen indicates the results while the form is offered to the put as much as-shaft dc trouble (Fig. eleven(a)). earlier than the prone point occasion the game plan of Fig. eleven(a) is in struggling us of a circumstance and is managed to paintings with Ps\* = a hundred and fifty MW and Qs\* = one hundred MVAr at CS1 (Fig.eleven (b)). it will in well-known be seen from Fig. sixteen(a) that the concerning CS1 power references are being pursued in advance than 0.5 s within the leisure run. At t = zero.five s, a dc side positioned as an awful lot as-shaft short out lack is made, which continues for 2 hundred ms. Following the blemish event, it's going to in trendy be seen from Fig. 16 (a) that the dynamic and responsive powers trade a number of the converter and cooling bypass section decreases to 0. that may be a right away end result of executing of maximum of the converter switches, which in this way authorizes the converter natural dc lack blockading functionality as can be seen from the following almost same circuit showed up in Fig. 15. it can further be visible from Fig. sixteen (b), in which the converter three-arrange modern-day waveforms are plotted, that the converter level streams are dwindled to highly a motivating pressure in a few unspecified time inside the future of the blemish state of affairs. This confirms the ampleness of the proposed converter in impeding the dc trouble contemporary. Fig. sixteen (c) indicates the converter dc factor voltage, which expectedly folds to zero at some stage in the problem term. Fig. 16 (d) indicates the capacitor voltages of FBSMs

A Peer Revieved Open Access International Journal

www.ijiemr.org

in stage a, which have inconsequential swell and continue to be enduring in mild of the way that the present day-day is blocked. After the issue is cleared at t = zero.7 s, the gating indication of switches of each the converter stations are de-blocked and the reference manage settings (Ps\*,s\*, Fig. eleven (b)) are increment a tiny bit at a time from zero to the pre-inadequacy regards. This lets in the converter dynamic and responsive powers trade with the shape to be increment a touch bit at a time from zero to their pre-lack regards as may be seen from Fig. sixteen (a). It might be seen from Fig. 16 (b) that the converter reports inrush streams for a quick time period at the equal time as the converter is de-blocked. This modestly better estimation of modern-day streams due to the charging of dccompanion capacitors after the inadequacy is cleared. it is able to similarly be visible from Fig. 16 that the pre-infection running conditions are restored the use of the control movement (Fig. 11 (b)) after the inadequacy is cleared. It might be finished up from over that regardless of the way that the take a look at machine is provided to the most true shape of dc hassle, the forced air tool lattice duty to the dc element imperfection cuttingedge is irritated with the useful resource of the converter manipulate movement and the hazard of converter dissatisfaction because of excessive cutting-edge-day tensions is diminished.

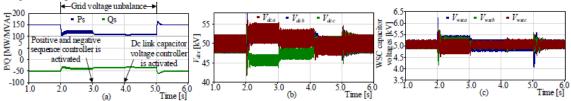

3) control of arrangement HBHMC HVDC gadget underneath matrix voltage unbalance situation:

in the beyond fragments, the reenactments of HBHMC have been established through using tolerating balanced 3-set up gadget situations. near the course of motion HBHMC circuit (Fig. 2 (a)), the three dc capacitor voltages (Vdca, Vdcb, Vdcc) of the 3 individual ranges, might depend on the brilliant tiers of force moved to the device.

inside the beyond fragments, the reenactments of HBHMC have been proven by using tolerating balanced three-set up machine conditions. close to the course of movement HBHMC circuit (Fig. 2 (a)), the 3 dc capacitor voltages (Vdca, Vdcb, Vdcc) of the three man or woman tiers, might depend upon the outstanding tiers of force moved to the gadget.

A Peer Revieved Open Access International Journal

www.ijiemr.org

Fig. 15.HBHMC during dc deficiency, (a) single-degree proportional chart of HBHMC for fantastic lattice voltage, (b) unmarried-degree equal outline of HBHMC for poor matrix voltage.

Fig. 16. Responses of CS1 even as dc imperfection takes place at some stage in 0.five to zero.7 sec (a) running and open power at the length of dc aspect inadequacy, (b) cooling waft all through dc facet hassle, (c) dc-interface voltage during dc weak point, and (d) FBSM capacitor voltages of degree a.

For an cheaper three-prepare form the strength moved by using every degree is same and similar to 33% of the great electricity moved. Hereafter, capacitors ought to have a comparative common steadfast kingdom voltage regards. despite the fact that, in specific situations, the device voltage can be disproportionate. In such cases the manipulate plan showed in [46]-[47] can be related for the HBHMC. inside the propagation test presented right here, to manipulate the WSC capacitor voltages the AZCI tool, as described in advance in phase III, is used, to research the response transient of the dc-interface voltages of capacitor the sport plan HBHMC beneath unbalance pass phase

voltage, the level a framework voltage is lessened to 33% of its apparent impetus at t = 2.zero s and it maintains for 3 s.Figs. 17 and 18 display off the quick lead of the form inside the route of the grid voltage unbalance. Fig. 17 (an) exhibits the threeprepare installation voltages following the occasion of event of unbalance at t = 2.0 s. right on the same time because the HBHMC is offered to the grid voltage unbalance and no put up-unbalance manage is started out (i.e., from t = 2.zero to three.0 s), the forced air gadget facet streams (Fig. 17(b)) and dc capacitor voltages (Fig. 18(b)) of the sport plan HBHMC end up disproportionate in advance than t = 3.0 s. that may be a cease result of the closeness of nonzero negative improvement modern-day-day alongside those traces, in the proposed form related activity plan HBHBMC, there are manipulate desires to be polished with a purpose to cope with this difficulty. The primary purpose is to make the converter yield contemporary balanced and the second is to attempt to out the dc capacitor voltages of every diploma. The converter 5bf1289bdb38b4a57d54c435c7e4aa1c may be balanced through displaying a bad accumulating current controller, as depicted in [47] for the segregated amazed converter. An equal manipulate plan has been accomplished within the furnished artwork for a similar aim and it'll in preferred be seen from Fig. 17(b) that after the stated controller is associated at t = 3.zero s inside the proliferation run, the converter streams gather balanced situation. proper on the same time as the submit unbalance manage is dynamic, the horrific collecting cuttingedgemodern fragments are reduced to zero and the pressured air tool aspect progressions of Fig. 17(b) are balanced. it's going to in modern-day be visible from Figs. 17(b) and 18(b) that no matter the

A Peer Revieved Open Access International Journal

www.ijiemr.org

manner that the weather control device aspect streams live balanced through the decency of a horrible progression current controller, the dc-interface capacitor voltages are to this point inconsistent (i.e., from t = three.0 to four 0 s). Relative problem of inconsistent dc capacitor

voltages for parallel creamer converter turn out to be inspected in [46] and a third consonant combination based totally manipulate plan have turn out to be used for enhancing the dc capacitor voltages underneath near choppy grid situations.

Fig. 17. (a) Unbalance in grid voltage at t = 2.0 s, (b) grid currents when positive and negative current control is activated at t = 3.0 s, and (c) grid currents when dc capacitor voltage control is activated at t = 4.0 s.

Fig. 18. Response of the series-HBHMC to ac side unbalance voltage: (a) active and reactive power, (b) dc-link capacitor voltages, and (c) average values of WSC capacitor voltages.

As such, that permits you to modify the ones dc capacitor voltages of the proposed plan HBHMC a manage technique much like the only stated in [46] is used. It is probably seen from Fig. 18(b) that once the stated controller is incited at t = 4.0 s inside the enjoyment run, the capacitor voltages are balanced. Fig. 17(c) in like way suggests that the converter cutting-edge-day-day live balanced after the order of each the greater controllers. finally, each the manipulate desires were fulfilled. Fig. 18(c) wellknown the everyday estimations of three-set up WSC capacitor voltages, which helps the ampleness of the proposed voltage control method method) even (AZCI below unbalance grid conditions. Fig. 18(a) exhibits the dynamic and responsive power moved via using the HBHMC to set up. The responsive powers dynamic and diminished in mild of the manner that the present references are compelled to steer clear of over modern-day-day in the converter.

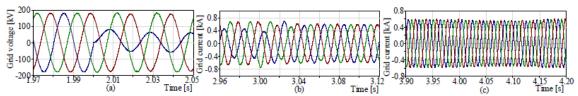

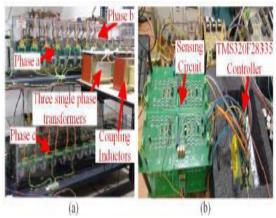

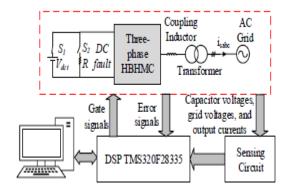

#### V.EXPERIMENTAL VALIDATION

This detail shows the test consequences for section framework associated the HBHMC model herbal the lab with FBSMs in step with arrange within the WSC. Fig. 19 reveals the HBHMC converter lab version. The vital initial parameters are recorded in desk V. The converter is balanced the use of PDPWM technique with the service repeat of two.0 kHz and the skip section repeat is 50 Hz. The manipulate and change method are finished TMS320F28335 DSP microcontroller. The rectangular outline of the achieved shape machine affiliation is showed up in Fig. 20. The midway and inner manipulate layers showed before in Fig. eleven (b) are in addition used for the initial considers. the prevailing references (id\* and ) are set thru the device chairman. The AZCI technique (Fig.5) is used to govern the WSC capacitor voltage and the present control circle (transitional control layer, Fig. eleven (b)) is used to cope with the dynamic and open current factors. Figs. 21 and 22 display off

A Peer Revieved Open Access International Journal

www.ijiemr.org

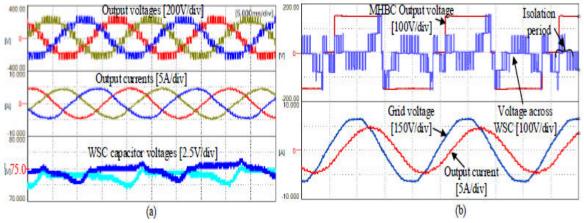

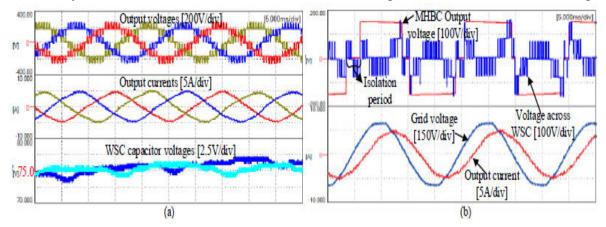

the suffering united states take a look at eventual effects of balanced three-put together device related path of motion **HBHMC** parallel-HBHMC, and independently, while the converters are controlled to artwork in the over guiding principle mode. The converters are managed to supply capability to the three-installation device at a loosen energy detail. It might be visible from Figs. 21(a) and 22(a) that the outright capacitor voltage of the WSC (in diploma an) is stored up at 100 and fifty V and the man or woman capacitor voltages are saved up at 75 V every for each course of movement and parallel plans the use of the proposed manage technique.

Fig. 19.photograph of take a look at model (an) a 3-stage HBHMC with two FBSMs consistent with level inside the WSC, and (b) detecting circuits and DSP controller.

Fig. 20.layout of manipulate framework usage for the HBHMC

# desk-V: EXPERIMENTAL PARAMETERS OF HBHMC

| Parameters Parameters                | Values |  |  |

|--------------------------------------|--------|--|--|

| Power rating                         | 2KVA   |  |  |

| dc-link voltage                      |        |  |  |

| Series-HBHMC                         | 450V   |  |  |

| Parallel-HBHMC                       | 150V   |  |  |

| No. of FBSMs per phase               | 2      |  |  |

| FBSM voltage                         | 75V    |  |  |

| FBSM capacitance                     | 2.0 mF |  |  |

| Single-phase transformer turns ratio | 1:1.3  |  |  |

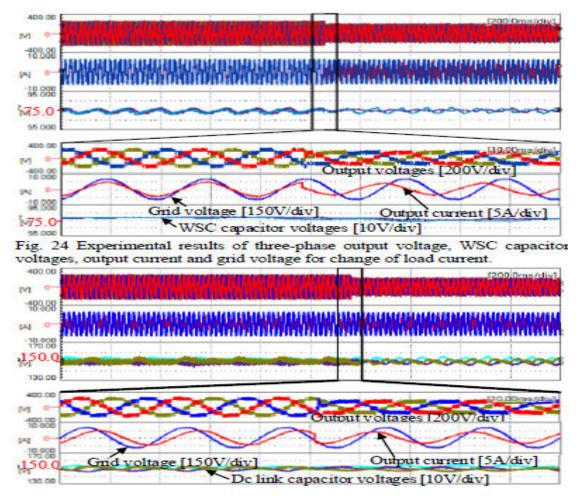

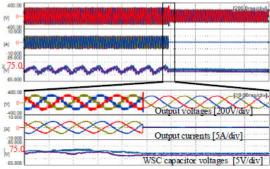

Figs. 21(a) and 22(a) in like way show the predictable usa 3-set up converter yield voltage and current waveforms seriesHBHMC and parallel-HBHMC, independently. The converter produces seven diploma voltage waveforms, which reconfirms its reasonability in working inside the overmodulation mode, as in like manner located in the multiplication research analyzed before in Sec. IV (Fig. 10). it can in like manner be seen from Figs. 21(a) and 22(a) that the FBSMs capacitor voltages are practically proportional and saved up enduring at seventy five V, which affirms the proposed voltage control and orchestrating methodologies displayed earlier than in Sec. III. The works elegantly and without a huge short for waveforms of MHBC yield voltage, voltage transversely over WSC, a sizable extent of walking situations. The references are pursued converter yield contemporary, and the system voltage of diploma a for quite efficiently notwithstanding even as a alternate in reference direction of motion and parallel HBHMC using the AZCI machine are tested size/set up is related. in Figs. 21(b) and 22(b), completely. It might be seen from Fig. 24 suggests the waveforms of 3-organize converter yield the waveform of voltage across over WSC that the separation mode is voltages, yield modern-day, grid voltage of level an, and WSC dynamic directly over the 0 crossing

A Peer Revieved Open Access International Journal

www.ijiemr.org

factor of yield voltage, as capacitor voltages (set up a) while each the size and anticipated for the AZCI approach. Time of the reference current are changed on the equal time. Fig. 23 exhibits the dynamic execution of the game plan this modification in modern-day references done a lessened estimation of HBHMC for yield modern trade. Fig. 23(a) famous the consequences mi, which ultimately modified the converter movement from of yield current, machine voltage, capacitor voltages of WSC for over

parity to below guiding precept mode. It is probably seen from step trade in modernday duration at cohesion energy issue. Fig. 24 that the quantity of yield voltage degrees have reduced further, Figs. 23(b), (c), and (d) display the effects for challenge from seven (for mi> 1) to 5 by extraordinary feature of the beneath guiding principle present day exchange from team spirit to loosen electricity issue, team spirit to (for  $mi \le 1$ ) technique for movement. In like way, Fig. 25 suggests the

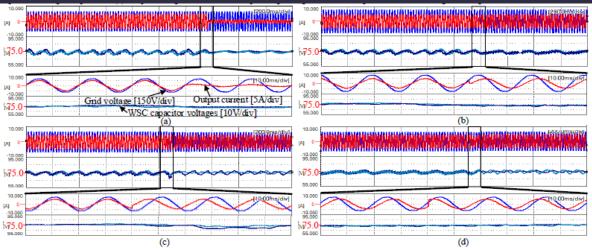

Fig. 21. Experimental constant kingdom output waveforms of series-HBHMC with AZCI approach, (a) 3-phase output voltages, output currents, and FBSM capacitor voltages of section-a, (b) Output voltage of MHBC, corresponding voltage across WSC, section-a modern-day, and grid voltage.

Fig. 22. Exploratory consistent state yield waveforms of parallel-HBHMC with AZCI technique, (a) three-stage yield voltages, yield flows and two FBSM capacitor voltages of stage a, (b) Output voltage of MHBC, comparing voltage crosswise over WSC, stage a current, and framework voltage.

A Peer Revieved Open Access International Journal

www.ijiemr.org

Fig. 23 Experimental waveforms of yield modern-day-day, community voltage, and capacitor voltages of FBSM of WSC of association HBHMC for (a) development alternate in contemporary greatness at concord strength element, (b) step change of contemporary from team spirit to slacking pressure detail, (c) step alternate of present day from cohesion to using pressure aspect, and (d) step change of present day from slacking to driving stress issue

Fig. 25 Experimental consequences of 3-degree yield voltage, dc-connect capacitor voltages, yield modern and network voltage for alternate of burden present day.

A Peer Revieved Open Access International Journal

www.ijiemr.org

It very well may be seen from Figs. 24 and 25 that the WSC and dclink capacitors voltages stay all around controlled regardless of the mode and number of yield voltage levels change. This further affirms agreeable activity and viability of the capacitor voltage control conspire for both overmodulation just as undermodulation method of HBHMC activity.

Fig. 26 shows the converter execution when a dc post to-shaft flaw is made in the arrangement HBHMC model (Fig. 20). Before the deficiency event the arrangement HBHMC is worked in modifying mode, providing capacity to air conditioning matrix (S1 is closed and S2 is open (Fig. 20)). The dc hassle is replicated by using remaining transfer S2 and starting switch S1 and through embeddings a deterrent R in the issue modern-day approach to reveal the blemish present day inner limits. The entryway pulses to the converter switches are deterred while the blemish is made. This makes the FBSMs capacitors come within the method for the ensuing contemporaryday within the way portrayed above close to Fig. 15. for this reason the pressured air machine streams quick abatement to nearly 0 virtually sincerely well worth. it is able to in like manner be seen from Fig. 26 that for the motive that blemish contemporary-day significance is quite a fantastic deal no longer some thing, the FBSMs capacitor voltages in like way do not revel in any disrupting impact and fairly remain at their prefault values. The results in Fig. 26 reconfirm the sufficiency of the proposed converter in blocking off dc aspect issues.

#### VI.LOSS EVALUATION

rightright here, the incident appraisal examinations of the HBHMC are completed. For straightforwardness, the in advance voltage drops of the secured gateway bipolar transistor (IGBT) and of the

freewheeling diode are believed to be vague and self-governing of the estimation of modern coursing via them.

Fig. 26. Trial aftereffects of HBHMC against the shaft to-post cut off: stage yield voltage and current, and WSC capacitor voltages of stage a This improvement fundamentally diminishes the estimation multifaceted nature [48]. Here the conduction misfortune is determined as [48],

$$P_{cond} = \frac{1}{2\pi} \int_{0}^{2\pi} NV_{fd} |i_{l}| d(\omega t)$$

where  $P_{cond}$  is the conduction loss of one stage leg, N is the quantity of switches in the conduction way,  $V_{fd}$  is the forward voltage drop of the semiconductor switch, and it is the present coursing through the converter stage leg. From (17), the complete conduction misfortunes for the HBHMC ( $Pc_{HBHMC}$ ) can be communicated as

$$P_{cHBHMC} = P_{cMHBC} + P_{cWSC} = \frac{1}{2\pi} \int_{0}^{2\pi} \left( \frac{N_{cMHBC} V_{fd} \left| I_{x}\left(t\right) \right|}{+N_{cWSC} V_{fd} \left| I_{x}\left(t\right) \right|} \right) d\left(\omega t\right)$$

in which PcMHBC and PcWSC are the conduction hardships inside the MHBC and WSC of HBHMC, in a steady progression, and NcMHBC and NcWSC are the amount of switches of MHBC and WSC inside the conduction way, as I would see it. The changing hardships of each framework are the blend of solidarity dispersal at each evolving event, which can be in respect to the common stage. For lodging, the standard front line well worth is mulled over at each changing snapshot of each machine. With

A Peer Revieved Open Access International Journal

www.ijiemr.org

this advanced the power dispersal inside the between time of flip-on and viewpoint road of every framework is anticipated from the datasheet of the machine. moreover, for the antiparallel diode, the turn-on and flip-off quality dispersal is considered as equivalent to that of IGBT move. the measure of changing events in an unmarried cycle copied with the essentialness dispersal at each such occasion yields the changing loss of each system [49]-[50], it's given by,

$$P_{swi} = f_{sw} \left( E_{on} + E_{off} \right) N_{sw}$$

where  $P_{swi}$  is the exchanging loss of the converter,  $f_{sw}$  is the exchanging recurrence,  $E_{on}$  and  $E_{off}$  are the vitality disseminations at turn-on and turn-off of the gadget, individually, and  $N_{sw}$  are the quantity of exchanging gadgets. Age and  $E_{off}$  are gotten from the datasheet relying upon the normal estimation of current. As in (18), the all out exchanging misfortune (PsHBHMC) of the HBHMC is the whole of exchanging misfortunes in MHBC and WSC and given as

$$P_{\mathit{zHBHMC}} = P_{\mathit{zMHBC}} + P_{\mathit{zWSC}} = \begin{pmatrix} f_{\mathit{zMHBC}} \left( E_{\mathit{on}} + E_{\mathit{off}} \right) N_{\mathit{zMHBC}} \\ + f_{\mathit{zWSC}} \left( E_{\mathit{on}} + E_{\mathit{off}} \right) N_{\mathit{zWSC}} \end{pmatrix} \,.$$

where  $P_{swi}$  is the exchanging loss of the converter,  $f_{sw}$  is the exchanging recurrence, Eon and  $E_{off}$  are the vitality dispersals at turn-on and turn-off of the gadget, separately, and  $N_{sw}$  are the quantity of exchanging gadgets. Age and  $E_{off}$  are gotten from the datasheet relying upon the normal estimation of current. As in (18), the all out exchanging misfortune ( $P_{sHBHMC}$ ) of the HBHMC is the aggregate of exchanging misfortunes in MHBC and WSC and given

$$P_{loss} = P_{cHBHMC} + P_{sHBHMC}$$

With the these days referenced suppositions the shortage of HBHMC is resolved and stood out and the MMC from HBSMs [1]-

[4], [48] and MMC with FBSMs [20]. To have a practical and particular mishap evaluation of the proposed HBHMC with numerous converters, it's miles crucial to assess their failures for the same circuit parameters and devices. consequently, a similar shape is used for mishap estimation proposed **HBHMC** and different converter systems. As a trouble take a look at version, the gadget with 150 MVA at 0.eight effect hassle is considered. the alternative shape conclusions considered for the adversity exams are: dc-interface voltage Vdct = three hundred kV, submodule capacitor voltage Vc = 2.5 kV. The Infineon (FZ1200R33KL2C) IGBT tool traits is taken into consideration for the problem test [51]. moreover, the going with novel cases are considered for disaster figurings:

- 1) The converters with comparable cooling component streams

- 2) The converters with comparable cooling power

At crew spirit change listing, the zenith of yield arrange voltage of conventional MMC is Vdct/2. anyhow, the apex of yield arrange voltages of activity plan HBHMC and parallel-HBHMC are

Vdct/3 and Vdct, independently. As needs be, in first case, the electricity surpassed on may be unmistakable for the topologies underneath concept. For this circumstance, the climate manage device present day degree of the big large fashion of converters below idea is seen as identical as that in the regular MMC paying little regard to cooling voltage size. In 2d case, due to the fact the proportional cooling energy is moved from cooling side to dc component, the path of motion HBHMC desires to pass on higher contemporary-day (1.5)activities) parallel-HBHMC wants to bypass decrease modern-day (zero.five sports) than

A Peer Revieved Open Access International Journal

www.ijiemr.org

the usual MMC installation contemporary. ultimately, for a comparative dc-interface the required quantity voltage, semiconductor gadgets is lesser for sport plan HBHMC and higher for parallel-HBHMC than the normal MMC. The conduction adversities, buying and selling mishaps and whole setbacks of the one-of-atype converters are confirmed up in Fig. 27. It might be seen from Fig. 27 that the hardships of the proposed direction of motion HBHMC topology, if there need to emerge an occasion of a comparative cooling impact, are more essential than the ones of the MMC with HBSMs but not without a doubt the ones of the MMC with FBSMs. Regardless, even as seemed in any other case close to MMC with HBSMs, the path of motion HBHMC has a few more abilities like dc issue tolerant capability, little effect shape, excessive dc-interface utilization, and an extra degree of chance for SM capacitor voltage converting, as an alternative, the parallel HBHMC has decrease setbacks even as regarded in a oneof-a-type manner on the subject of MMC with HBSMs.that is in slight of the truth that solitary a part of the climate manage device contemporary is needed to transport same cooling strength while seemed in some different way near MMC with HBSMs. Regardless, the quantity of SMs are better in case of parallel-HBHMC

Fig. 27.Conduction, buying and promoting and general incidents of MMC with HBSM

[1]-[4], [48], MMC with FBSM [20], and proposed HBHMC.

what is extra, the sport plan HBHMC adversities are decrease and parallelHBHMC incidents are better than the disasters of MMC with HBSMs and MMC with FBSMs in case of a comparative cooling current. The ordered evaluation of the proposed HBHMC topology with the opposite important VSC HVDC converter topologies to the extent the favored amount of semiconductor gadgets is given in the accompanying area.

# VII.COMPARISON OF HBHMC WITH GIFT TOPOLOGIES

A connection of the proposed HBHMC topology with the opportunity predominant VSC HVDC converter topologies is finished the quantity that the specified extensive kind of semiconductor devices and capacitors for a comparable dc-interface voltage. The MMC topology with HBSMs is taken into consideration due to the fact the benchmark topology for this assessment have a look at. For assessment N = Vdct/Vsw is described, where Vsw is the assessed voltage of 1 SM, Vdct is the difficult and speedy dclink voltage and N addresses the overall scale SM comprise required in every arm of MMC. furthermore, for taking a gander on the possible range of converter yield voltage the non-interleaved balance technique is considered for MMC [44]. the amount of feasible yield voltage levels for all topologies is settled for the alternate rundown of one.table VI traces evaluation of the proposed seriesHBHMC and parallel-HBHMC topologies with the opposite predominant

HVDC converter topologies, for instance, MMC with HBSMs [1][4], MMC with all FBSMs [20], Hybrid MMC (50percentHBSMs and 50p.cFBSMs) [22], HCMC [23]-[26], AAMMC [27]-[29],

A Peer Revieved Open Access International Journal

www.ijiemr.org

parallel bypass breed MMC [33], [34], and CTFB-HMC [35]. it is clean from desk VI that amounts of switches and capacitors required for the route of movement HBHMC are much less whilst seemed differently almost about the ones in various topologies. what is more, the quantity of switches inside the conduction direction for the route of motion HBHMC is lesser than the precise converter topologies. moreover, since the MHBC of the proposed plan works at the key repeat, the sport plan HBHMC isexpected to have decrease mishaps. Regardless, for the same dc-interface voltage in all topologies, the great cooling vield voltage received from the path of movement HBHMC is decrease, which manufactures the prevailing score want of converter switches for a comparative energy. The parallel-HBHMC regardless of the manner that calls for frequently range of devices for a similar dc-interface voltage, yet it gives high utilization of the dc delivery. consequently the seriesHBHMC topology can be step by step sensible for the packages with excessive dc-interface voltage and reduce contemporary requirements, while the parallel-HBHMC can be continuously becoming for the programs with lower dc-accomplice voltage and higher cutting-edge requirements.

it is also to be seen that during region of the MMC, the difference is compelled in HBHMC to the diploma the MHBC a few part of the converter is involved. Regardless, the WSC a few little little bit of