A Peer Revieved Open Access International Journal

www.ijiemr.org

### COPY RIGHT

2019IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 6<sup>th</sup> Aug 2019. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-08&issue=ISSUE-08

Title COMBINED AND AUGMENTED ARCHITECTURE FOR LUT AND MUX BASED LOGIC DESIGNS

Volume 08, Issue 08, Pages: 267–272.

Paper Authors

### L.ANUSHA, Mr.J.LINGAIAH

ARJUN COLLEGE OF TECHNOLOGY & SCIENCE, BATASINGARAMI, TS, INDIA, 501512

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

### COMBINED AND AUGMENTED ARCHITECTURE FOR LUT AND MUX BASED LOGIC DESIGNS

<sup>1</sup>L.ANUSHA, <sup>2</sup>Mr.J.LINGAIAH

<sup>1</sup>M.TECH VLSISD, DEPT OF E.C.E, ARJUN COLLEGE OF TECHNOLOGY & SCIENCE, BATASINGARAMI, TS, INDIA, 501512

<sup>2</sup>ASSOCIATE PROFESSOR, ARJUN COLLEGE OF TECHNOLOGY & SCIENCE, BATASINGARAMI, TS, INDIA, 501512

#### ABSTRACT:

Amending the performance and reducing the location in the racing circuits, an amalgamation of appearance up tables with multiplexer method is together implemented. Implementing this type of structure an incipient MUX: LUT anatomical structure is designed, which matches predicated on the parent of comparators and logical racing circuit's .Extra congruous for this implementation both accounting for involutes common sense block and routing vicinity whilst maintaining mapping intensity. The interconnections an increasing number of the ascendant allele subscriber to postpone, area and electricity losing disorder in Complementary Metal-Oxide Semiconductor (CMOS) digital circuits. Hybrid configurable logic block architectures for field-programmable gate arrays that contain a aggregate of LUT have and hardened multiplexers which are evaluated closer to the purpose of higher good judgment density and reduced area. Technology mapping optimizations that target the proposed architectures are also perform inside Xilinx software program. Both for complicated logic block and routing location at the same time as keeping mapping depth, the nominated structure of this paper examine the common sense length, location and electricity intake the use of Xilinx.

**Keywords:** FPGA, Multiplexer logic element, Complex logic block, mapping technologies.

#### **1. INTRODUCTION**

A field-programmable gate array (FPGA) is a block of programmable common sense that may enforce multi-stage logic features. FPGAs are maximum normally used as separate commodity chips that can be programmed to implement massive functions. However, small blocks of FPGA logic can be useful additives on-chip to allow the person of the chip to personalize part of the chip's logical characteristic. An FPGA block must put in force both combinational common sense functions and interconnect so as to construct multi-level

good judgment functions. There are several one of a kind technology for programming FPGAs, however maximum common sense techniques are not going to implement anti fuses or similar difficult programming technologies. Throughout the records of area-programmable gate arrays (FPGAs), research tables (LUTs) had been the number one good judgment element (LE) used to realize combinational good judgment. A Kenter LUT is normal and very bendy capable of enforce any K-input Boolean characteristic. The use of LUTs simplifies

A Peer Revieved Open Access International Journal

www.ijiemr.org

technology mapping because the problem is reduced to a graph protecting problem. However, an exponential location charge is paid as large LUTs are taken into consideration. The fee of K between four and 6 is usually visible in industry and academia, and this variety has been established to offer a great region/overall performance compromise. Recently, number of different works have explored alternative FPGA LE architectures for performance development to shut the massive hole among FPGAs and alertnessparticular included circuits (ASICs). We gift a six-enter LE predicated on 1 / 4-to-one MUX, MUX4, that can understand a subset of six-input Boolean logical machine social feature, and an incipient hybrid involutes common sense block (CLB) that includes a coalescence of MUX4s and six-LUTs. A Proposed MUX4s are minute compared with a 6-LUT (15% of 6-LUT place), and may successfully map all 2, 3-enter capabilities and some four, five, 6-enter capabilities. This advisement, we explore factorability of LEs-the facility to cut up the LEs into a couple of more minuscule elements-in both LUTs and MUX4s to increment common sense awareness. A ratio of LEs that have to be LUTs versus MUX4s is moreover explored closer to optimizing common sense denseness for each non fracturable and fracturable FPGA architectures. Facilitate the structure geographic expedition, we evolved a CAD menstruation for mapping into the proposed hybrid CLBs, engendered using ABC and VPR, and describe era mapping techniques that embolden the cull of common sense capabilities that may be embedded into the MUX4 factors.

#### 2. RELATED STUDY

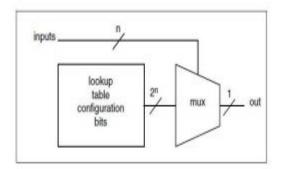

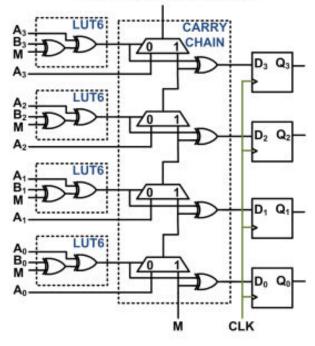

The fundamental approach used to fabricate a combinational motive square (CLB) additionally referred to as a cause aspect in a SRAM-based totally FPGA is the query table (LUT). According to the beneath Fig, the question table is a Static Random Access Memory and is utilized to execute a truth desk. Each address in the SRAM speaks to combinational contributions to the intent aspect. The esteem placed away within the cope with speaks to the estimation of the ability for that facts combo. An n-input work calls for a SRAM with areas. Because a simple SRAM isn't always clocked, the lookup table logic detail operates lots as any other common sense gate as its inputs changes, its output changes after a few put off.

#### Fig.2.1. Lookup Tables.

A usual good judgment element has four inputs. The delay through the research table is unbiased of the bits saved inside the SRAM, so the postpone via the logic element is the same for all features. This manner that, as an example, a lookup deskprimarily based good judgment element will exhibit the identical put off for a four-enter XOR and a four-input NAND. In contrast, a four-enter XOR constructed with static CMOS common sense is appreciably slower than a four-enter NAND. Of course, the static common sense gate is normally quicker than the common sense detail. Logic elements commonly comprise

A Peer Revieved Open Access International Journal

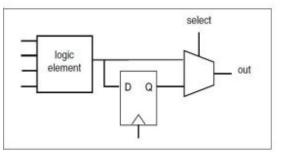

registers turn-flops and latches as well as combinational good judgment. A turn-flop or latch is small compared to the combinational logic element (in sharp comparison to the scenario in custom VLSI), so it makes feel to add it to the combinational common sense element. Using a separate mobile for the memory element might honestly take in routing sources. The reminiscence detail is hooked up to the output; whether it shops a given fee is controlled through its clock and permit inputs.

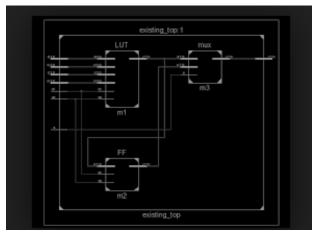

#### Fig.2.2. Programming A Lookup Table.

A cause thing has four assets of info. The postponement in the query table is freed from the bits placed away in the SRAM, so the deferral thru the rationale aspect is the identical for all capacities. Significance of that is, for example, a question table based totally purpose issue will display a similar postponement for a four-enter XOR and a 4enter NAND. In difference, a 4-enter XOR worked with static CMOS cause is a good deal slower than a four-enter NAND. Obviously, the static purpose entryway is typically rapid than the reason aspect. Rationale additives contain registers, turnand locks and slumps additionally combinational rationale. A flip-tumble or is little with hook contrasted the combinational purpose aspect, so it has significance to add it to the combinational intent issue. Utilizing an alternate cell for the reminiscence component might basically

take up directing belongings. The reminiscence issue is attached to the yield; regardless of whether or not it shops a given esteem is managed through its clock and empower inputs.

### 3. AN OVERVIEW OF PROPOSED SYSTEM

The MUX4 LE seemed in Figure. Three 4-to-1 MUX contains of with а discretionary reversal on its information resources that allow the acknowledgment of any 2,three-enter work, a few 4,5- input capacities, and one 6-input work a 4-to-1 MUX itself with discretionary reversal on the information inputs. A four-to-1 MUX matches the records stick tally of a 6-LUT, taking into account affordable examinations community regarding the and intra Any organization directing. two-input Boolean ability can be successfully performed in the MUX4: the 2 capability facts resources may be attached to the pick out lines and truth table esteems (motive 0or rationale may be directed to the data inputs as wishes be. For three-enter capacities; take into account that Shannon decay around one variable produces cofactors with at maximum elements. A second disintegration of the co-factors round one in every of their notable factors produces cofactors with at maximum one variable. Such single variable cofactors can be bolstered to the data inputs (the discretionary reversal might be required), with the disintegration factors encouraging the select sources of information. Moreover, elements of more than four assets of info can be performed in the MUX4 so long as Shannon deterioration regarding any two information sources produces cofactors with at maximum one statistics. A. Without fracturable LEs and B. With fracturable LEs. Latest association, the fracturable LEs

A Peer Revieved Open Access International Journal

#### www.ijiemr.org

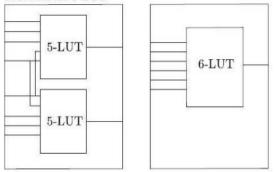

check with an architectural detail on which one or more machine of good judgment capabilities can be optionally mapped. The Nonfracturable LEs consult with an architectural element on which only one logic characteristic is mapped. Favored nonfracturable architectures, the MUX4 shown detail in Fig. A is utilized collectively with nonfracturable 6-LUTs. The detail percentage the identical variety of inputs as a 6-LUT lending for truthful comparison with reverence to the enter connectivity. Being the fracturable architecture, we don't forget an 8-enter LE, proximately matched with the adaptive common sense module in latest Altera Stratix FPGA families. The 6-LUT that can be fractured into two five-LUTs utilising eight inputs.

#### Fig.3.1. Model of LUT.

Then the Two 5-enter features may be mapped into this LE if two inputs are shared among the 2 capabilities. In case that no inputs are shared, four-input capabilities may be mapped to every 5-LUT. Since the MUX4 variant, Dual MUX4, we utilize two MUX4s within a one eight-input LE. Latest Contour, shown in Fig. The two MUX4s are stressed out to have devoted cull inputs and shared statistics inputs.

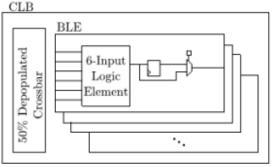

A variety of different architectures have been taken into consideration the first being a nonfracturable architecture. In the nonfracturable architecture, the CLB has forty inputs and ten fundamental LEs (BLEs), with every BLE having six inputs and one output. Fig.5 shows this nonfracturable CLB structure with BLEs that contain an optional register. We vary the ratio of MUX4s to LUTs in the ten elements CLB from 1:9 to five:5 MUX4s:6-LUTs. The MUX4 element is proposed to paintings along with 6-LUTs, growing a hybrid CLB with a combination of 6-LUTs and MUX4s (or MUX4 variants).

Fig.3.2. Hybrid CLB with a 50% depopulated intra-CLB.

INPUT TO NEXT CARRY CHAIN

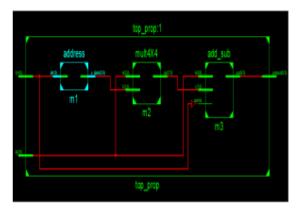

# Fig.3.3. Original pipelined adder subtractor design.

In spite of the fact that determining the territory of a MUX4 element in recognize to

A Peer Revieved Open Access International Journal

www.ijiemr.org

a 6- LUT is important, we must likewise international **FPGA** analyze variety considering the amount of CLB tiles, sector overheads inside the CLB and guidance location per CLB. All through this paper, international FPGA location became assessed accepting that, according to tile, half of the vicinity is bury bunch and intra group steerage, 30% of the variety is utilized for LUTs, and 20% for registers and exceptional various intent, following Anderson and Wang and a non-public correspondence. Note that this 50%-30%-20% model is a gauge in view of a standard complete FPGA plan wherein-by the guidance and inward CLB crossbars are improved closer to 6-LUTs. Creation of an advanced FPGA the use of our new MUX4 additives would truely trade said display. Be that as it is able to, advancing the complete steering engineering towards our MUX4 variations, measuring the directing design, and closing the circle by means of making a more particular version is out of the extent of these paintings. Utilizing this version, we are able to point out a few goal facts approximately the half of and half of CLB engineering.

Fig.3.4. Simulation block diagram.

We have proposed a brand new hybrid CLB structure containing MUX4 hard MUX factors for efficient are and mapping to those architectures. Weighting of MUX4embeddable features with our Mux Map technique combined with a pick out mapping approach provided aid to circuits with low herbal MUX4- embeddable ratios. In extension work the anti symmetric product coding (APC) and strange-a couple of garage (OMS) techniques for lookuptable (LUT) design for memory-based totally multipliers to be used in virtual signal processing programs. Each of these strategies results in the reduction of the LUT length by way of a thing of. In this quick, we present a extraordinary form of APC and a changed OMS scheme, so that it will integrate them for green memory-based multiplication.

Fig.3.5. RTL schematic model.

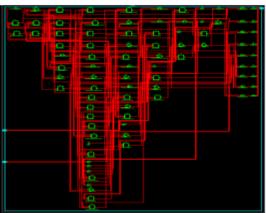

Fig.3.6. Technology Schematic.

A Peer Revieved Open Access International Journal

www.ijiemr.org

Fig.3.7. Xilinx Design. 4. CONCLUSION

The Propose incipient hybrid CLB structure containing MUX and logical factors and show the strategies for effectively mapping to those architectures. Operation of LUT payoff more power maintaining and area preserving nature with economic value benefits. A coalescence of MUX: LUT engenders prosperous power intake and length discounts schemas in single unit. Proposed scheme ensures the size and nature of the LUT MUX in more efficient way, however in future this work is elongated to interconnect many features, which are more and more the ascendant contributor to postpone, location and strength consumption in CMOS digital circuits. The implementation surmounts several inhibitions located in precedent implementations posted to this point, along with the desideratum for unique capabilities within the CMOS technique or mogulhungry present mode cells.

### REFERENCES

[1] Y. Hara, H. Tomiyama, S. Honda, and H. Takada, "Proposal and quantitative analysis of the CHStone benchmark program suite for practical C-based highlevel synthesis," J. Inf. Process., vol. 17,pp. 242–254, Oct. 2009.

[2] A. Canis et al., "LegUp: High-level synthesis for FPGA-based processor/accelerator systems," in Proc. ACM/SIGDA FPGA, 2011, pp. 33–36.

[3] E. Ahmed and J. Rose, "The effect of LUT and cluster size on deep submicron FPGA performance and density," IEEE Trans. Very Large Scale Integr. (VLSI), vol. 12, no. 3, pp. 288–298, Mar. 2004.

[4] J. Rose, R. Francis, D. Lewis, and P. Chow, "Architecture of field programmable gate arrays: The effect of logic block functionality on area efficiency," IEEE J. Solid-State Circuits, vol. 25, no. 5,pp. 1217–1225, Oct. 1990.

[5] H. Parandeh-Afshar, H. Benbihi, D. Novo, and P. Ienne, "Rethinking FPGAs: Elude the flexibility excess of LUTs with and-inverter cones," in Proc. ACM/SIGDA FPGA, 2012, pp. 119–128.

[6] J. Anderson and Q. Wang, "Improving logic density through synthesis inspired architecture," inProc. IEEE FPL, Aug./Sep. 2009, pp. 105–111.

[7] H. Parandeh-Afshar, H. Benbihi, D. Novo, and P. Ienne, "Rethinking FPGAs: Elude the flexibility excess of LUTs with and-inverter cones,"in Proc. ACM/SIGDA FPGA, 2012, pp. 119–128.

[8] J. Anderson and Q. Wang, "Improving logic density through synthesis inspired architecture," in Proc. IEEE FPL, Aug./Sep. 2009, pp. 105–111.

[9] J. Anderson and Q. Wang, "Areaefficient FPGA logic elements: Architecture and synthesis," inProc. ASP DAC, 2011, pp. 369–375.