A Peer Revieved Open Access International Journal

www.ijiemr.org

### **COPY RIGHT**

2019IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 3<sup>rd</sup> Aug 2019. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-08&issue=ISSUE-08

Title DESIGN AND ACCOMPLISHMENT OF SLEEP CONVENTION LOGIC WITH HIGH ACCURACY

Volume 08, Issue 08, Pages: 166-169.

**Paper Authors**

#### M.JYOTHI, R.BHEEMA SHANKAR

KAKINADAINSTITUTEOFENGINEERINGANDTECHNOLOGYFOR WOMEN,KORANGI,ANDHRAPRADESH,INDIA,533461

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic

Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

# DESIGN AND ACCOMPLISHMENT OF SLEEP CONVENTION LOGIC WITH HIGH ACCURACY

<sup>1</sup>M.JYOTHI, <sup>2</sup>R.BHEEMA SHANKAR

<sup>1</sup>M.TECH VLSID, DEPT OF E.C.E, KAKINADA INSTITUTE OF ENGINEERING AND TECHNOLOGY, KORANGI, ANDHRAPRADESH, INDIA, 533461

<sup>2</sup>ASSISTANT PROFESSOR, KAKINADA INSTITUTE OF ENGINEERING AND TECHNOLOGY, KORANGI, ANDHRAPRADESH, INDIA, 533461

#### **ABSTRACT:**

Testability is a considerable trouble in field for today's center system-on-chip format. Design-for-testability (DFT) methods are required for any type of kind of thinking layout, including asynchronous thinking layouts in order to reduce the evaluation rate. Relax convention thinking (SCL) is a new enticing asynchronous thinking layout that is based upon the far more preferred asynchronous thinking style NULL convention thinking (NCL). Rather than the NCL, there is currently no format for testability strategies existing for the SCL. The purpose of this paper is to assess the various errors within SCL pipelines as well as additionally recommend a scan-based DFT technique to make the SCL testable. The recommended DFT technique wants that confirmed with a selection of experiments, disclosing that the method provides a high evaluation insurance policy protection (> 99%). The complete DFT strategy, in addition to the check chain as well as additionally examines cell design, exist.

Keywords: DFT, SCL, NCL, Logic style, Low power consumption, On chip method..

#### 1. INTRODUCTION

SCL circuits have a number of benefits over standard NCL circuits. These benefits are the straight outcome of using the rest device to the circuit. Considering that the NULL stage is currently required via the rest signal as opposed to awaiting the NULL wave front to circulate via the circuit. evictions no more require hysteresis, since input efficiency relative to NULL is naturally made certain by clearly resting all evictions. Getting rid of hysteresis from the NCL entrances causes a considerable quantity of location conserving. Because of this, no added reasoning is needed to be contributed to a combinational block to make it input total

relative to the DATA. Lastly, observability in the SCL circuits is likewise guaranteed through the rest device considering that any type of prospective orphan is clearly removed in between 2 nearby information stages by insisting the rest signal. In recap, the adhering to payments is made. Present **ATPG** devices do not sustain asynchronous circuit designs such as the NCL because of asynchronous responses courses and also lack of a clock signal. There are generally 2 methods in the literary works to make the NCL circuits testable: restricted insertion of control/observation indicates boost mistake insurance coverage and also

A Peer Revieved Open Access International Journal

www.ijiemr.org

simultaneous modelling of NCL pipes to make them suitable with concurrent ATPG devices as well as utilizing check chain strategy.

Fig.1.1. SCL function diagram.

2. RELATED STUDY

The staying component of this paper is arranged as complies with. The associated DFT help the twin rail SCL is reviewed in Section III. Area IV examines numerous stuck-at mistakes within the SCL AES S-After that a scan-based DFT approach is recommended. The suggested technique is ultimately verified by using different screening metrics and also the speculative outcomes are displayed in area V. Finally, the verdicts are reeled in Section VI. Power contrast for the typical s-box procedure as well as the twin rail rest convention reasoning based S-box is made it in the table. Layout for testability (DFT) is a significant worry in today's semiconductor market since it is important lower examination time. boost examination top quality, as well as decrease the price linked with producing and also using examination vectors. In comparison to the NCL circuits, no DFT

technique has actually been established for the SCL circuits up until now. The present NCL details DFT strategies cannot be straight utilized for the SCL circuits as a result of the architectural distinctions brought on by presenting the rest system for power-gating.

## 3. AN OVERVIEW OF PROPOSED SYSTEM

This DFT strategy is made use of generally for testable concurrent circuit. In this check chain layout we think using D-flipflops just. A mux is put at the input of each flip-flop as if all flip-flops can be linked in a change register for one mux choice as well as to operate in a typical setting in the various other Connect the SFF in a change register and also examination combinational component. Degree delicate methods that mention adjustments in FSM are independent of hold-ups neither order of modifications in input signals (if inputs are readied to brand-new worths). Check is specified as a capability to change right into or out of any type of state. The benefits of check style are: suitable with clock layouts, numerous Shorten examination application time, Simplify the sewing of the flip-flops. The key inputs are put on the Dual rail s-box circuit and also the matching below byte makeover will certainly be done to supply the AES security result. Right here the double rail reasoning will certainly make complex the setup of s-box circuit. Therefore the protection will certainly be given due to the fact that hacking is made complex in this approach much more over the screening time will certainly be lowered and also the mistake insurance coverage is enhanced in this DFT. The goal of this paper is to examine the different stuck-at mistakes within an SCL pipe as well as

A Peer Revieved Open Access International Journal

www.ijiemr.org

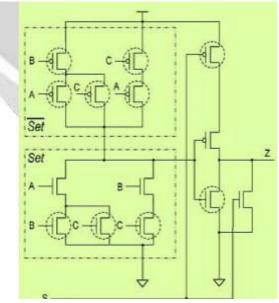

suggest a thorough scan-based screening approach that offers a high examination insurance coverage at the price of the common location overheard brought on by presenting the check chain. The SCL structure is displayed in Fig. 1. As in Null Convention Logic, in each pipe phase of SCL design a combinational reasoning feature block (Fi), a register block (Ri), and also a conclusion detector block (CDi) are had. As well as this SCL calls for an added gateway to integrate in between DATA as well as NULL stages of the circuit. This added gateway is a basic resettable C-element with upside down outcome as well as it is referred to as the conclusion C-element (Ci). Combinational reasoning obstructs in the SCL are constructed from limit entrances which execute the unatefunctions as well as there is no reasoning inversions are enabled.

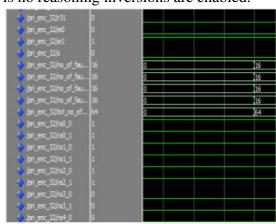

Fig.3.1. Simulation results.

The performance of eliminated reset block is currently done by the resting system. Insisting the rest signal separates the result inverter from VDD and also draws eviction "s outcome, Z, to GND, as well as this resets eviction. Considering that the inputs of each SCL gateway are extracted from the outcomes of coming before SCL entrances, the interior node would certainly after that charge to VDD as well

as finish the reset stage. The hold1 block " s task was to include hysteresis to the NCL entrances that aids to make sure inputcompleteness relative to NULL. In the SCL circuits, given that all evictions within the combinational blocks required to reset by insisting the rest signal, the input-completeness relative to NULL is currently made certain and also for that reason NULL wave front breeding is not required. The circled around transistors in Fig. 2 are of high limit voltage for decreasing leak existing when eviction remains in non-active state and also it decreases the fixed power usage in the circuit.

#### 4. CONCLUSION

In this task we can executed SCL based AES S-box method efficiently by utilizing verilog language. The trouble of screening SCL circuits for stuck-at mistakes was examined. The mistakes were at first split right into 2 different classifications, Faults on reasoning entrances and also Faults on rest signal forks. The mistakes within each after that assessed group independently, as well as the effect of the mistakes was reviewed. Ultimately, the recommended **DFT** technique confirmed with speculative outcomes. By utilizing the mistake shot strategies the mistake insurance coverage will certainly be enhanced.

#### **REFERENCES**

[1] Farhad A. Parsan, Scott C. Smith and also Waleed K. Al- Assadi, "Design for Testability of Sleep Convention Logic", IEEE Transactions on huge range combination (VLSI) systems, 18 March 2015, pp. 1-11.

[2] S. Mutoh, T. Douseki, Y. Matsuya, T. Aoki, S. Shigematsu, as well as J. Yamada, "1-V power supply high-speed

A Peer Revieved Open Access International Journal

www.ijiemr.org

electronic circuit innovation with multithreshold-voltage CMOS," IEEE J. Solid-State Circuits, vol. 30, no. 8, pp. 847-- 854, Aug. 1995.

- [3] P. Lakshmikanthan, K. Sahni, as well as A. Nunez, "Design of ultra-low power combinational typical collection cells making use of an unique leak decrease technique," in Proc. IEEE Int. SOC Conf., Sep. 2006, pp. 93-- 94.

- [4] A. Bailey, A. Al Zahrani, G. Fu, J. Di, as well as S. C. Smith, "Multi-threshold asynchronous circuit layout for ultra-low power," J. Low Power Electron., vol. 4, no. 3, pp. 337-- 348, 2008.

- [5] F. A. Parsan and also S. C. Smith, "CMOS application of fixed limit entrances with hysteresis: A brand-new technique," in Proc. IEEE/IFIP 20th Int. Conf. VLSI Syst.-Chip (VLSI- SoC), Oct. 2012, pp. 41-- 45.

- [6] L. Zhou, "Ultra-low power as well as radiation hard asynchronous circuit style," Ph.D. argumentation, Dept. Elect. Eng., Univ. Arkansas, Fayetteville, AR, USA, 2012.

- [7] N. Rajagopala Krishnan as well as K. Sivasuparamanyan, "A Reconfigurable Low Power FPGA Design with Autonomous Power Gating as well as LEDR Encoding", in Proc. of7' th International Conference on Intelligent Systems and also Control ISCO (2013), pp.221-226.

- [8] Shu.T, M. Krunz, as well as S. Liu, "Secure information collection in cordless sensing unit networks making use of randomized dispersive courses," IEEE Trans. Mobile Comput., vol. 9, no. 7, pp. 941-- 954, Jul. 2010.

- [9] P. Sushruthapani and also S. Mohamed Bilal, "Test Coverage Enhancement Using Test Point Insertion Technique," IJEEC:

International Journal of Electrical Electronics and also Communication, vol. 21, problem. 301, pp. 4441- 4447, Sep. 2016.