A Peer Revieved Open Access International Journal

www.ijiemr.org

#### **COPY RIGHT**

2019IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 3rd Apr 2019. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-08&issue=ISSUE-04

Title: DESIGN AND ANALYSIS OF LOW POWER HYBRID CMOS FULL ADDER

Volume 08, Issue 04, Pages: 80-88.

**Paper Authors**

J.R.V.SAMHITHA, V.GAYATHRI, P.PREMSAI, M.SAISRUTHI, V.ANIL KUMAR REDDY, DR.N.A.V.PRASAD

SRI VENKATESWARA INSTITUTE OF TECHNOLOGY, Anantapur

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic

Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

#### DESIGN AND ANALYSIS OF LOW POWER HYBRID CMOS FULL ADDER

J.R.V.SAMHITHA<sup>1</sup>, V.GAYATHRI<sup>2</sup>, P.PREMSAI<sup>3</sup>, M.SAISRUTHI<sup>4</sup>, V.ANIL KUMAR REDDY<sup>5</sup>, DR.N.A.V.PRASAD <sup>6</sup>

1,2,3,4,5 Btech Scholar, ECE Department, SRI VENKATESWARA INSTITUTE OF TECHNOLOGY,

Anantapur

<sup>6</sup>M.Tech,Ph.D, Professor & HOD, ECE Department, SRI VENKATESWARA INSTITUTE OF TECHNOLOGY , Anantapur

**Abstract:** In this project, novel circuits for XOR/XNOR and simultaneous XOR–XNOR functions are proposed. The proposed circuits are highly optimized in terms of the power consumption and delay, which are due to low output capacitance and low short-circuit power dissipation. We also propose six new hybrid 1-bit full-adder (FA) circuits based on the novel full-swing XOR-XNOR or XOR/XNOR gates. Each of the proposed circuits has its own merits in terms of speed, power consumption, powerdelay product (PDP), driving ability, and so on. An efficient three-input XOR/XNOR circuits as the most significant blocks of digital systems with a new systematic cell design methodology (SCDM) in hybrid-CMOS logic style is proposed in this project. SCDM, which is an extension of CDM, plays the essential role in designing efficient circuits. At first, it is deliberately given priority to general design goals in a base structure of circuits. This structure is generated systematically by employing binary decision diagram. After that, concerning high flexibility in design targets, SCDM aims to specific ones in the remaining three steps, which are wise selections of basic cells and amend mechanisms, as well as transistor sizing. In the end, the resultant three-input XOR/XNORs enjoy fullswing and fairly balanced outputs.we can extend this project for designing of full adder design and it's topologies

#### **INTRODUCTION**

The advantage of utilizing a combination of low-power components in conjunction with low-power design techniques is more valuable now than ever before. Now a day's power is the primary concern due to the remarkable growth and success in the field of personal computing devices and wireless communication system which demand high speed computation and complex functionality with low power consumption. The motivations for reducing power consumption application to application. In the class of

micro-powered battery operated portable applications such as cell phones, the goal is to keep the battery lifetime and weight reasonable and packaging cost low. For high performance portable computers such as laptop the goal is to reduce the power dissipation of the electronics portion of the system to a point which is about half of the total power dissipation. Finally For the high performance non battery operated system such workstations the overall goal of power minimization is to reduce the system cost while ensuring long term device

A Peer Revieved Open Access International Journal

www.ijiemr.org

reliability. In the past, the major concerns of the VLSI designer were area, performance, cost and reliability; power consideration was mostly of only secondary importance. In recent years, however, this has begun to change and, increasingly, power is being given comparable weight to area and speed considerations. Several factors have contributed to this trend.

Perhaps the primary driving factor has been the remarkable success and growth of the class of personal computing devices and wireless communications which demand high-speed systems computation and complex functionality with low power consumption. In these applications, average power consumption is a critical design concern. From the environmental viewpoint, the the power dissipation electronic systems, the lower the heat pumped into the rooms, the lower the electricity consumed and hence the lower the impact on global environment.

#### 1.1 Need for Energy efficient Adders

Adders are the most important components used in most of the Digital signal processors for real applications. Adders are also used in the architecture of other arithmetic operators like Subtractors, Multipliers, shifters, MACs, etc. Many Adder architectures been proposed by various researchers over the years. Even today the researches on Adder architectures are finding a major interest for achieving energy efficient devices. The survey on conventional adder architectures [3, 5-9] have proved there is a lot more scope for optimization. method One optimization is by using different logic styles for different parts of the design instead of using the same logic style throughout the design. This method of designing with different logic styles in various parts of the same circuit is called Hybrid circuit. Various hybrid architectures were surveyed for reference [1, 2 and 4]. This paper presents a Hybrid full adder circuit consisting of two different logic styles namely CMOS logic and Pass transistor logic. This method has lesser power consumption, and hence energy efficient.

#### 1.2 LITERATURE SURVEY

We see many distributed papers thatcompete in outlining better circuits. Such reviews for the most part relyon inventive outline thoughts yet don't take after an efficient approach. As a result, the vast majority of them experience the ill effects of some unique disservices.

1) They are executed with rationale styles that have an incompletevoltage swing in some interior hubs, which prompts staticpower dissipation.2) Most of them experience the ill effects of yield flag debasement extreme maintain low-voltage andcannot They prevalently have operation.3) dynamic power utilization fornonadjusted spread deferral inside and outside circuits, which brings about glitches at the outputs. Therefore, efficient outline procedure can respected as a solid answer for the test. It is not attempt and-blunder driven, which that it efficiently implies intentionally plans to the designgoals. It likewise picks circuit parts astutely and does not postponethe assurance of the attributes after recreation. circuit Celldesign approach (CDM) has been exhibited to plan some limitedfunctions, for example, two-input XOR/XNOR and

A Peer Revieved Open Access International Journal

www.ijiemr.org

carry-inverse carryin the half breed CMOS style. The transcendent outcomes persuadeus to enhance CDM through two phases: 1) producing complexfunctions and 2) correcting residual blemishes. imperfections inpreviously distributed CDM incorporate containing some strides inthe configuration manual stream and producing an extensive number of outlines in whichthe transcendent ones would be resolved after the consummation of simulations. In this way, in the principal arrange, a three-input XOR/XNORas a standout amongst most intricate the and universally handy three-input fundamental gatesin number juggling circuits has been picked. In the event that the productivity of the circuits is affirmed in such a focused domain, it canshow the quality of the approach. In the second stage, CDM ismatured as methodical CDM (SCDM) in outlining the threeinputXOR/XNORs interestingly. methodicallly produces elementarybasic cell (EBC) utilizing parallel choice graph (BDD), and wiselychooses circuit parts in view of a particular target. This takesplace when the specified elements are considered in the not CDM. Therefore, after the efficient era. the SCDM considerscircuit streamlining in light of our objective in three stages: 1) savvy selection of the fundamental cell; 2) astute determination of the alter mechanisms; and 3) transistor measuring. It ought to be noticed that BDD can be utilizedfor EBC era of other three-input capacities. We consider the power-defer item (PDP) as the outline target. It remains as a fairperformance metric, definitely including convenient

electronic systemtargets. The inspiration to utilize this procedure is the nearness of some remarkable components and the capacity to deliver some effective circuits that appreciate every one of these favorable circumstances.

- 1) The SCDM isolates a circuit structure into principle structureand improvement redress systems. In the structure, it fundamental considers highlights including minimal number of transistorsin basic way, genuinely adjusted yields, being force sans ground, and symmetry. The components have the dutyof finishing the usefulness of the circuits, maintaining a strategic distance from anydegradation on the vield voltage, and expanding the drivingcapability.

- 2) minimal number of transistors in basic way builds thechances of the circuit to have better qualities, as experimental results have demonstrated a normal sparing of 10%–50% and 27%–77% as far as deferral and Energy-Delay Product (EDP), respectively.

- 3) The dynamic utilization enhancement originates from the reality ofwell-adjusted spread postponement. This element is advantageous for applications in which the skew between arriving signals iscritical for appropriate operation, and for fell applications to reduce the shot of making glitches.

- 4) Power sans ground primary structure prompts control lessening.

- 5) Symmetrical structure, high measured quality, and normal arrangement of outlines offer ascent to sharing more wells of connected transistors and thusly diminishing the possessed areaabout 26%–32%.

A Peer Revieved Open Access International Journal

www.ijiemr.org

- 6) The corruption in all yield voltage swing can in this way becompletely evacuated, which makes the outline manageable inlow VDD operations and low static power dispersal.

- 7) Internal rationale structure of plans can possibly be vitality efficientabout 17%–53% because of the joined decrease ofpower utilization and engendering delay.

- 8) SCDM uses the advantages of various rationale styles as the hybridstyle.

- 9) The technique has high adaptability in target and systematically consider it in the three outline steps. This can lead to efficient circuits as far as execution, power, PDP, EDP, area, or a blend of them.

- 10) The quick advancement of microelectronics manufacture processes demands another cell library era or a library technologymigration. The efficient deliberate strategy leadsto mechanized stream, which can lessen configuration time and costs, provide consistency in the cell library era process, increase the scope of recreation abilities at the characteristicsstep, and also limit the danger of mistakes.

#### **EXISTING SYSTEM**

The state-of-the art issues in this brief can be divided into twocategories as they are extracted from the topic: 1) conventional three inputXOR and 2) methodologies. Most of the designed SUMs havebeen produced jointly or by cascading some modules. The cascadedmodules derived from reformulations of the Boolean function, such as

$$SUM = C_{in} \bigoplus H (1)$$

$$SUM = C_{in} \cdot H_{\perp} + C_{in} \cdot H (2)$$

SUM =  $C_{\text{in}} \cdot H_{-} + C_{\text{out}} \cdot H$ ,  $C_{\text{out}} = C_{\text{in}} \cdot H + A \cdot H$  (3)

WhereH and Hare A⊕ B and the supplement of H, respectively. In (1), the H yield is XORed with convey of the previousstage (Cin). The SUM modules having a place with this class havebeen used in numerous adders, for example, SERF, XOR-FA, 9A, and 9Bas SUM module. Expression (2) can realizedwith a two-to-one multiplexer with H and H as the selectlines, which is broadly utilized as a part of viper execution. In (3), carry from the past and this stage, Cin and Cout other than H and H\_are utilized to create SUM yield. LPHS-FAis made up of the expression as a SUM module. At last, as specified some time recently, somecircuits mutually delivered the module from which we can point tothree-XOR, newthree-XOR, SUM-connect, SUM-PTL, 10T\_new,12T\_new, and 18T\_new\_FS. Among majority the of mentioned circuits, we consider the SUM modules of Hernandez1, Hernandez2,TFA, Hybrid, NEWHPSC, and 18T NEW FS. LPHS-FA, whoseexcellent execution are affirmed. As aresult, the total correlation will happen by choosing them forreference. As can be seen from the regular circuits, allthe distributed effective plans depend on inventive thoughts of designersThey don't take after an efficient approach, while new solutionsoften have enhanced couple of attributes, thus there is a free spacefor the orderly outline system. CDM has been used todesign some constrained capacities. In this concise, CDM is maturedas SCDM for planning three-input XOR/XNOR. Full adders, being one of the most fundamental

A Peer Revieved Open Access International Journal

www.ijiemr.org

building blocks of all the aforementioned circuit applications, remain a key focus domain of the researchers over the years. Different logic styles, each having its own merits and bottlenecks, investigated to implement1-bit full adder cells. The designs, reported so far, may be broadly classified into two categories: 1) static style 2) dynamic style. In the existing system, full-adder has to obtain intermediate signal and an its complement, which are then used to drive other blocks to generate the final outputs. The overall propagation delay and the power consumption of the fulladder depend on the delay and its complement generated. So, to increase the operational speed of the full-adder, it is necessary to develop a new logic structure that does not require the generation of intermediate signals to control the selection or transmission of other signals located on the critical path. In most hybrid techniques, XOR, and XNOR functions were simultaneously generated by pass transistor logic module by using only six transistors. CMOS module produces full swing outputs of the full adder but at the cost of increased transistor count and decreased speed. Although the hybrid logic styles offers promising performance, most of these hybrid logic adders suffered from poor driving capability issue and their performance degrades drastically in the cascaded mode of operation if the suitably designed buffers not included.

#### PROPOSED SYSTEM

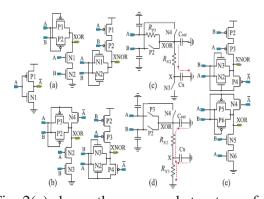

Proposed XOR–XNOR Circuit

The nonfull-swing XOR/XNOR circuit

of Fig. 1(a) [24] is efficient in terms of

the power and delay. Furthermore, this

structure has an output voltage drop problem for only one input logical value. To solve this problem and provide an optimum structure for the XOR/XNOR gate, we propose the circuit shown in 1(b). For all possible input combinations, the output of this structure is full swing. The proposed XOR/XNOR gate does not have NOT gates on the critical path of the circuit. Thus, it will have the lower delay and good driving capability in comparison with the structures of Fig. 1(a) and (b). Although the proposed XOR/XNOR gate has one more transistor than the structure of Fig. 1(b), it demonstrates lower power dissipation and higher speed. The input A and B capacitances of the XOR circuit shown in Fig. 2(b) are not symmetric, because one of these two should be connected to the input of NOT gates and another should be connected to the diffusion of nMOS transistor. Furthermore, the input capacitances of transistors N2 and N3 are not equal in the optimal situation (minimum PDP). Also, the order of input connections to transistors N2 and N3 will not affect the function of the circuit. Thus, it is

better to connect the input A, which is also connected to the NOT gates, to the transistor with smaller input capacitance. By doing this, the input capacitances are more symmetrical, and thus, the delay and power consumption of the circuit will be reduced. To clarify which transistor (N2 or N3) has larger input capacitance, let us consider the condition that the inputs change from AB = 00 to AB = 10.

A Peer Revieved Open Access International Journal

www.ijiemr.org

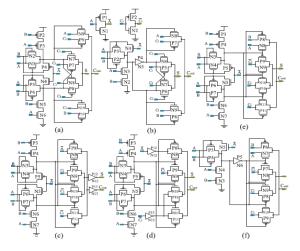

Fig. 2(e) shows the proposed structure of the simultaneous XOR-XNOR gate consisting of 12 transistors. structure is obtained by combining the two proposed XOR and XNOR circuits of Fig. 2(b). If the inputs of this circuit are connected as mentioned in Section III-A, the input A and B capacitances are not equal (the inputs A and B are connected to the same transistor count). Thus, to equal the input of capacitances, they are connected to the circuit, as shown in Fig. 2(e). In this case, the input capacitances are approximately equal and the power and delay are optimized. This structure does not have any NOT gates on the critical path and its output capacitance is very small. For this reason, it is very high speed and consumes low power. The delay of XOR and XNOR outputs of this circuit is almost identical, which reduces the glitch in the next stage. Other advantages of this circuit are good driving capability, full-swing output, as well as robustness against transistor sizing and supply voltage scaling. We proposed six new FA circuits for various applications which have been shown in Fig. 6. These new FAs have been employed swith hybrid logic style, and all of them are designed by using the proposed XOR/XNOR or XOR-XNOR circuit. The well-known four-transistor 2-1MUX structure [Fig. 8(a)] is used to implement the proposed hybrid FA cells. This 2-1-MUX is created with TG logic style that has no static and short-circuit power dissipation.

Fig. 6(a) shows the circuit of first proposed hybrid FA (HFA-20T) which is made by two 2-to-1 MUX gates and the XOR-XNOR gate of Fig. 2(e). The circuit of HFA-20T has not high power consumption NOT gates on critical path and consists of 20 transistors. The advantages of this structure are fullswing output, low power dissipation and very high speed, robustness against supply voltage scaling, and transistor sizing. If  $A \_ B = 1$ , then the output Cout signal equals to the input signal A or B. But to equalize the inputs capacitance, both of the input signals A and B are implementation for and connected to the transistors N9 and P10 [in Fig. 6(a)], respectively. The only problem of HFA-20T is reduction of the output driving capability when it is used in the chain structure applications, such as ripple carry adder. Of course, this problem exists in the circuits that use the transmission function theory in their implementation without buffering output. Fig. 7 shows the circuit layout of proposed HFA-20T which designed for minimum power consumption [26]. One way to reduce the power consumption of FA structures is to use a XOR/XNOR gate and a NOT gates to generate the other XOR or XNOR signal. The proposed hybrid FA cell (HFA-17T) shown in Fig. 6(b) is designed by using the XOR gate of Fig. 2(b).

A Peer Revieved Open Access International Journal

www.ijiemr.org

Fig. 6. Proposed six new hybrid FA circuits. (a) HFA-20T. (b) HFA-17T. (c) HFA-B-26T. (d) HFA-NB-26T. (e) HFA-22T. (f) HFA-19T.

This structure is made by 17 transistors that has three transistors less than the HFA-20T. The delay of HFA-17T is higher than that of HFA-20T due to the addition of NOT gates on the critical path of the HFA-17T (for making the XNOR signal from the XOR signal). It may be expected that the power consumption of HFA-17T is less than that of HFA-20T due to the reduction in the number of transistors. But the NOT gate on the critical path of the circuit increases the short circuit power. So there is no significant reduction in total power dissipation of the HFA-17T. Also, the NOT gate will slightly improve the output driving capability of the circuit. As mentioned earlier, using the buffer on the output of a circuit is almost mandatory, especially in applications that the output capacitance of each stage is high. In practice, the driving capability of VLSI circuits is degraded due to the creation of the parasitic capacitors and resistors during the fabrication, as well as increasing the threshold voltage of transistors over the time, but the output buffer improves this situation. Fig. 6(c) presents the third proposed hybrid FA with buffers on the Sum and Cout outputs (HFA-B-26T), and it is made with 26 transistors. There are XOR-XNOR gate, one 2-1-MUX gate, and NOT gates on the critical path of HFA-B-26T. The output NOT gates are used to prevent the driving output nodes by the inputs of the circuit and also reduce the resistance from the output node of the circuit tothe sources (VDD and GND). The power consumption and delay of HFA-B-26T are more than that of HFA-20T and HFA-17T FAs. Fig. 6(d) shows another proposed hybrid FA with new buffers (HFA-NB-26T), where they are placed in the data inputs of 2-1-MUX gates instead of placing the buffers in the outputs. If the input signals of A and C are produced by the buffer, then for all possible input combinations, the Sum and Cout outputs are not driven by the inputs of the circuit. To do this work, three additional NOT gates are enough, because there was already the A signal and can be made the buffered A signal with an extra NOT gate. So the HFA-NB-26T FA circuit is made by 26 transistors. The data input nodes of 2-1-MUXs reach to their final value (GND or VDD) before the XOR and XNOR signals are produced. Thus, the critical path of HFA-NB-26T consists of an XOR-XNOR gate and a 2-1-MUX The driving capability of the HFA-NB-26T is slightly less than that of HFA-B-26T due to existing the 2-1-MUX gate between the buffer and the output node [which increases the resistance from the output node to the sources (VDD)GND)]. The circuits of HFA-20T and HFA-17T have been designed so that the less number of transistors has been used.

A Peer Revieved Open Access International Journal

www.ijiemr.org

To produce the output Sum signal, the XOR, XNOR, and C signals are onlyused so no additional NOT gates needs to generate the C signal, whereas if the C signal is also used to produce the Sum output, then XOR and XNOR signals will not drive the Sum output through the TG multiplexer, but only they will be connected to the data select lines of 2-1-MUX. So the capacitance of XOR and XNOR nodes become smaller, and the delay of the circuit will be improved. It is expected that the power consumption and delay of the HFA-22T and HFA-19T FA circuits are less than of HFA-20T and HFA-17T, respectively (despite having two more transistors), due to the less capacitance of XOR and XNOR nodes. Also, by adding the C signal, the driving capability of HFA-22T and HFA-19T will be better than that of HFA-20T and HFA-17T, respectively.

#### SIMULATION RESULT

#### **COMPARISION TABLE**

| EXISTING  | PROPOSE    |          |

|-----------|------------|----------|

| METHOD    | D          |          |

|           | METHOD     |          |

| TRANSISTO | 26         | 22       |

| R COUNT   |            |          |

| Control   | 3.96 mW    | 1.392    |

| CONSUME   |            | mW       |

| D         |            |          |

| DELAY     | 1.40 sec   | 0.89 sec |

| Most      | 5.529882e- | 2.598204 |

| extreme   | 005        | e-005    |

| POWER    |            |          |

|----------|------------|----------|

| CONSUME  |            |          |

| D        |            |          |

| Least    | 3.926799e- | 1.392061 |

| POWER    | 009        | e-009    |

| CONSUME  |            |          |

| D        |            |          |

| Normal   | 8.678680e- | 1.451884 |

| POWER    | 007        | e-007    |

| CONSUME  |            |          |

| D        |            |          |

| TRANSIEN | 0.03 sec   | 0.01 sec |

| T        |            |          |

| ANALYSIS |            |          |

# CONCLUSION AND FUTURE SCOPE

SCDM fills in as a plan technique for three-input XOR/XNOR, which is a standout amongst the most perplexing and focused and also generally useful three-input fundamental entryways in math circuits. The philosophy puts accentuation on doing every one of the means in a totally deliberate manner. It likewise appreciates high flexibility in configuration target, while it takes after a similar methodology to acquire the cutting edge plans. This brief has favored SCDM with the shrewd choice of the circuit parts for the PDP target. At last, three new superior three-input XOR/XNOR circuits with less PDP and involved zone are imagined utilizing SCDM. The new circuits appreciate driving capacity, transistor thickness, commotion insusceptibility with low-voltage operation, and minimal likelihood to deliver glitches. As a one of a kind element, the basic way of the exhibited outlines comprises of just two transistors, which causes low spread postponement. All things considered, these circuits outflank their partners with

A Peer Revieved Open Access International Journal

www.ijiemr.org

17%–53% and 27%–77% change in PDP and EDP, separately, in HSPICE reenactment in light of the TSMC 0.13-μm innovation. The range use for the proposed circuits appreciates 26%–32% change with the upsides of consistency and symmetry in format.

#### **BIBLIOGRAPHY**

- [1] ToorajNikoubin, MahdiehGrailoo and ChangzhiLi,Energy and Area Efficient XOR/XNORs with Systemetic Cell Design Methodology,IEEE transaction papers.

- [2] W.J. Dally and J.W. Poulton. Digital systems engineering. Cambridge UnivPr, 1998.

- [3] Yin-Tsung Hwang, Jin-Fa Lin, and Ming-HwaSheu. Low-power pulse-triggered flip-flop design with conditional pulse-enhancement scheme. *IEEE Trans. VLSISyst.*, 20(2):361–366, 2012.

- [4] Bai-Sun Kong, Sam-Soo Kim, and Young-Hyun Jun. Conditional-capture flip-flop for statistical power reduction. *Solid-State Circuits, IEEE Journal of*, 36(8):1263 –1271, aug 2001.

- [5] H. Mahmoodi, V. Tirumalashetty, M. Cooke, and K. Roy. Ultra low-power clocking scheme using energy recovery and clock gating. Very Large Scale Integration(VLSI) Systems, IEEE Transactions on, 17(1):33 –44, jan. 2009.

- [6] N. Nedovic, M. Aleksic, and V.G. Oklobdzija. Conditional pre-charge techniques for powerefficient dual-edge clocking. In Low Power Electronics and

- Design, 2002. ISLPED '02. Proceedings of the 2002 International Symposium on, pages 56 59, 2002.

- [7] V. G. Oklobdzija. Clocking and clocked storage elements in a multi-gigahertz environment. *IBM Journal of Research and Development*, 47(5.6):567 –583, sept. 2003.

- [8] M.W. Phyu, W.L. Goh, and K.S. Yeo. Low-power/ high-performance explicit-pulsed flip-flop using static latch and dynamic pulse generator. *IEE Proceedings-Circuits, Devices and Systems*, 153:253, 2006.

- [9] S.H. Rasouli, A. Khademzadeh, A. Afzali-Kusha, and M. Nourani. Low-power single- and double-edge-triggered flip-flops for high-speed applications. *Circuits, Devices and Systems, IEE Proceedings* -, 152(2):118 122, April 2005.

- J. Tschanz, S. Narendra, [10] Zhanping Chen, S. Borkar, Sachdev, and Vivek De. Comparative delay and energy of single edge-triggered and dual edgetriggered pulsed flip-flops for highperformance microprocessors. Low Power Electronics and Design, International *Symposium* 2001.pages 147 –152, 2001.

- [11]. P. Zhao, T. Darwish, and M. Bayoumi. Low power and high speed explicit-pulsed flip-flops. In *Circuits and Systems*, 2002. MWSCAS-2002. The 2002 45thMidwest Symposium on, volume 2, pages II–477. IEEE, 2002.