A Peer Revieved Open Access International Journal

www.ijiemr.org

### COPY RIGHT

2018IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 5th Dec 2018. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-07&issue=ISSUE-12

Title: PARTITIONAL AND CONVOLUTION BASED FIR FILTER DESIGN USING DISTRIBUTIVE ARCHITCTURE

Volume 07, Issue 12, Pages: 1027–1038.

**Paper Authors**

#### LINGAIAH JADA, RODDA JAHNAVI, K.RAJITHA

Arjun College Of Technology & Sciences

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic Bar Code

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

### PARTITIONAL AND CONVOLUTION BASED FIR FILTER DESIGN USING DISTRIBUTIVE ARCHITCTURE <sup>[1]</sup> LINGAIAH JADA , <sup>[2]</sup>RODDA JAHNAVI, <sup>[3]</sup> K.RAJITHA

<sup>[1]</sup> HOD & Associate Professor, Arjun College Of Technology & Sciences

<sup>[2]</sup> Assistant Professor, Arjun College Of Technology & Sciences

<sup>[3]</sup>VLSI Design (M.Tech), Arjun College Of Technology & Sciences

#### **ABSTRACT:**

In this paper, both Multiplier and Multiplierless strategy have been actualized in light of the ordinary model and Floating point structures. In multiplier technique, Modified Booth and a Modified Booth with Wallace tree multiplier is composed while in the multiplier less strategy, circulated number-crunching and conveyed number-crunching with parcel is outlined utilizing Verilog. The code is reenacted in Model Sim and orchestrated in Xilinx 14.7. This paper outlines the near investigation of the multiplier and multiplier-less technique in view of different parameters. There is an exchange off among zone and postponement. This paper will pick the best technique as per the necessity.

#### 1. INTRODUCTION:

Gaussian convolutions are maybe the frequently utilized picture administrators in low-level PC vision assignments. Shockingly however, there are valuable couple of articles that portray effective and exact usage of these operators. Multiply and Accumulate one (MAC) is of the fundamental squares utilized in numerous computerized flag handling frameworks. The general structure of a MAC unit comprises of a multiplier, a snake and a shifter. Disposal of multiplier in MAC unit can be made conceivable by utilizing calculations. for example, Distributed Arithmetic (DA). Thus; DA takes out the utilization of multipliers and ROM to do numerous calculations, for example, Fast Fourier Transform (FFT), Discrete Cosine

Transform (DCT), and so forth [8]. As computerized flag handling (DSP) is incorporated into more gadgets, time to showcase and the capacity to roll out late plan improvements ends up essential. Programming can give the adaptability in configuration, permitting late plan changes yet its execution is poor contrasted with equipment. Programming executes in a consecutive way where equipment can execute in a genuinely parallel manner. Then again, making an application particular incorporated circuit (ASIC) sets aside the more drawn out opportunity to make and once done it isn't alterable. This is the place a field programmable door cluster (FPGA) turns into an awesome arrangement by consolidating the qualities of equipment and

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

#### www.ijiemr.org

programming. An option in contrast to the MAC approach is DA which is an outstanding strategy to spare assets and was created in the late 1960's autonomously by Croiser et al. also, Zohar. The expression "conveyed number-crunching" is gotten from the way that the math activities are not effortlessly clear and regularly dispersed over the terms. This can be confirmed by looking which is a modified. DA is somewhat level improvement of steady increase, which replaces augmentation with a high number of query tables and a scaling gatherer. Utilizing a DA strategy, the channel can be executed either in bit serial or completely parallel mode to tradeoff among data transmission and region use. Generally, this imitates the query tables, taking into consideration parallel queries. Accordingly the duplication of various bits is performed in the meantime [2]. The key understanding in this calculation is that comprises of parallel constants of the type of intensity of 2. This takes into consideration the precomputation of every one of these qualities, putting away them in a query table, and utilizing the individual data sources xi as a location into the query table. Here, each line figures the last item by utilizing one piece (of the weight) from all inputvalues. This adequately replaces the consistent duplication with a query table. At that point the calculation relating to each line of the is performed by tending to the query table with the fitting qualities as directed by the individual info factors. Each line is processed serially and the yields are moved by the fitting sums (i.e. 0, 1, 2, ...,B1 bits). Figure 1.1 presents a visual

portrayal of the DA adaptation of inward item calculation. The information grouping is nourished into the move enlist at the information test rate. The serial yield is exhibited to the RAM based move registers at the bit clock rate which is B+1 times (n is number of bits in an information input test) the example rate. The RAM based move enlist stores the information in a specific location. The yields of enlisted LUTs are added and stacked to the scaling collector from LSB to MSB, and the outcome is gathered after some time. For a n bit input, n+1 clock cycles are required for a symmetrical channel to create the yield [10]. In an ordinary MAC, with a set number of MAC hinders, the framework test rate diminishes as the channel length increments because of the expanding bit width of the adders and multipliers and thusly the expanding basic way delay. Be that as it may, this isn't the situation with serial DA designs since the channel test rate is decoupled from the channel length. As the channel length is expanded, the throughput is kept up however more rationale assets are required. While the serial DA engineering is effective by development, its execution is restricted by the way that the following info test can be handled simply after all of the present information test is prepared. Each piece of the present info test takes one clock cycle to process.

#### **1.1 MOTIVATION:**

Quick Fourier Transform (FFT) is utilized to assemble different picture preparing frameworks and application particular Digital Signal Processing (DSP) equipment. As of now all detailed plans for FFT utilize

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

#### www.ijiemr.org

ROMs or memory for complex twiddle duplications. Legitimate strategies must be taken after to take out the need of multipliers in FFT outline. A standout amongst the most much of the time utilized and huge technique to wipe out the multipliers utilized in FFT configuration is usingDistributed Arithmetic for twiddle augmentations. While utilizing DA method, one must do exact moving to diminish the quantity of adders.

#### **1.2 CONTRIBUTION:**

A few strategies have been presented for proficient reconfigurable consistent multiplier outline [22], [23] for any application where the channel's coefficients are changing continuously e.g. multistandard advanced up/down converter. Twofold normal sub-articulation disposal (BCSE) calculation is one of those strategies, which presents the idea of wiping out the regular sub-articulation in double shape for outlining an effective consistent multiplier, and is in this manner appropriate for reconfigurable FIR channels with low intricacy [13]. Nonetheless, the decision of the length of the paired basic subarticulations (BCSs) in [13] makes the plan wasteful by expanding the viper step and the equipment cost. The productivity regarding velocity, power, and region of the consistent multiplier has been expanded in the work exhibited in [14] while planning one reconfigurable FIR channel for multistandard DUC by picking 2-bit long BCS prudently Choice of the BCS of settled length (3-bit or 2-bit) in the prior proposed BCSE calculation based reconfigurable FIR channel outlines [13], [14] leaves an

extension to advance the composed channel by thinking about the BCS over the nearby coefficients and in addition inside a solitary coefficient. The tradition considered for speaking to the information and the coefficient of the prior composed FIR channel [13], [14] as marked extent arrange likewise gives an extension to adjust the information portrayal to marked decimal number for more extensive pertinence of the proposed FIR channel in any frameworks. On concentrate the previously mentioned written works, it has been understood that the improvement of an effective reconfigurable consistent multiplier is especially required for its pertinence in any reconfigurable framework.

#### 2. RELATED WORK:

G. NagaJyothi and S. SriDevi, [1] Finite motivation reaction (FIR) channel is a compelling square in different flag handling applications. The complexities in VLSI execution of FIR channels is ruled by the quantity of increase and aggregate (MAC) tasks. Appropriated Arithmetic (DA) is an elective method where the MAC tasks can be supplanted by a progression of look-into tables and expansion activities. FIR channel in view of DA are computationally effective on account of high level of automation engaged with the usage of MAC tasks utilizing DA. Numerous reconfigurable and non-reconfigurable FIR channel models can be produced utilizing DA. This work surveys the current FIR channel designs in light of DA. LUT based DA and LUT-less DA are the huge techniques in the execution non-reconfigurable channels. This of concise condenses the region and power

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

#### www.ijiemr.org

reports of the current non-reconfigurable FIR channel models in view of both LUT based DA and LUT-less DA. One dimensional and two dimensional systolic DA based designs for FIR channel execution are likewise informed. DA based versatile FIR strategies are clarified. This work introduces the similar consequences of FIR and versatile FIR channel models as far as territory, control, region postpone item, least cycle period and vitality per test. This overview can shape a reason for additionally inquire about on DA based FIR channel designs.

G. D. Licciardo, C. Cappetta, L. Di Benedetto and M. Vigliar, [2] another radix-3 apportioning strategy for characteristic numbers, inferred by the weight segment hypothesis, is utilized to fabricate a multiplierless circuit that is appropriate for interactive media sifting applications. The dividing strategy permits helpfully premultiplying 32-b skimming point channel coefficients with the littlest arrangement of parts creating an unsigned whole number info. Thusly, like the disseminated number juggling, shifters and recoding hardware, run of the mill of other understood multiplier circuits, are totally substituted with streamlined gliding point adders. Contrasted with the existent writing, directed to both field-programmable door exhibit and std\_cell innovation, the detailed accomplishes arrangement state-ofthecraftsmanship exhibitions regarding elaboration speed, accomplishing a basic way deferral of around 2 ns both on a Xilinx Virtex 7 and with CMOS 90-nm std\_cells.

N. A. Petrovsky, A. V. Stankevich and A. A. Petrovsky, [3] This work displays an efficient plan of the of the whole number tonumber invertible quaternionic multiplier in view of the square lifting structure and pipelined installed processor of the given multiplier utilizing dispersed numbercrunching (DA) as a square of Mband straight stage paraunitary channel banks (LP PUFB) in light of the quaternionic polynomial math (Q-PUFB) for the lossy-tolossless picture coding. A bank Q-PUFB in light of the DA square lifting structure decreases the quantity of adjusting activities and has a customary design. Since the square lifting structures with adjusting activities can actualize the whole number tointeger change (Q-PUFB).

K. Durga and A. Sivagami, [4] This concise presents a proficient versatile Reversible Logic Finite Impulse Response channel (RLFIR) in view of Distributed Arithmetic (DA) utilizing Reversible doors. Reversible rationale is a standout amongst the most basic issues at present time because of its capacity decrease adequacy in circuit outlining. The postponement and the intelligent assets of the detailed outline were fundamentally decreased by utilizing include one convey select snake in the inward result of the versatile channel. The current convey spare viper in the versatile channel is supplanted by the detailed include one convey select snake and rationale entryways in include one convey select snake is supplanted by reversible rationale doors keeping in mind the end goal to diminish the power utilization. The sensible assets and deferral is diminished to half when

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

contrasted with the current convey spare viper and the power utilization is lessened to half by changing reversible doors. This work presents quantum execution and combinational circuit of all essential reversible entryways and its VHDL code. All reversible rationale entryways are checked and reproduced by Xilinx 8.2i.

#### **3. IMPLEMENTATION:**

The channel is a circuit used to upgrade a few highlights of the information flag or to rejected the undesirable one. There are two kinds of channels utilized in DSP. One is FIR channel and another is IIR channel. A FIR channel is a channel whose motivation reaction is of limited span since it settles to zero in limited time. On the off chance that you give contribution as a drive, that is, a solitary "1" test taken after by many "0" tests, zeroes will turn out after the "1" test has advanced through the postpone line of the channel. The drive reaction is limited on the grounds that there is no criticism arrange in the FIR. Hence, the expression "limited motivation reaction" is almost same with "no criticism". FIR channel offers numerous favorable circumstances when contrasted with IIR channels which are suited for some applications. FIR channel structures involve a multiplier, postponement, and snake. In this paper, the accentuation is more on multiplier square. More effective method for performing MAC activity is required to actualize FIR channel on FPGA. In one strategy, adjusted adaptation of customary multipliers are utilized and in another technique multiplier is supplanted by multiplier-less structures.

#### **CONCEPT: MULTIPLIERS**

Multipliers assume a urgent job in the present DSP and different applications. With progresses in innovation, numerous analysts have attempted are as yet endeavoring to outline multipliers which offer both of the accompanying plan targets - fast, low power utilization, normality of design and less territory or even mix of them in one multiplier. The normal duplication technique is "include and move" calculation. In multipliers, halfway items are created which must be included. The expansion of incomplete items is the essential parameter that decides the execution of the multiplier. To decrease the quantity of fractional items to be included, Modified Booth calculation is a standout amongst the most famous calculations. То accomplish speed enhancements Wallace Tree calculation can be utilized to lessen the quantity of consecutive including stages. Promote by consolidating both Modified Booth calculation and Wallace Tree procedure we can see the upside of the two calculations in single multiplier. The fundamental a augmentation calculation takes after the means demonstrated as follows

• If the LSB of Multiplier is '1', at that point include the multiplicand into a gatherer.

• Shift the multiplier one piece to one side and multiplicand one piece to one side.

• Stop when all bits of the multiplier are zero.

From above obviously the augmentation has been changed to the expansion of numbers [1]. On the off chance that the Partial Products are included serially then a serial viper is utilized. The parallel multiplier is

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

#### www.ijiemr.org

utilized to include all the halfway items parallelly utilizing one combinational circuit. Nonetheless, pressure system can likewise be utilized to lessen the quantity of fractional items and to perform expansion with less dormancy.

Altered Booth Multiplier

The Original form of Booth's multiplier (Radix - 2) had two disadvantages.

• The quantity of tasks ended up factor and badly arranged for parallel increase.

• When there are separated 1s, the Algorithm winds up wasteful.

The above issues of Radix-2 are utilizing overwhelmed bv Radix 4 Algorithm which can check strings of three bits with the calculation given beneath. The plan of Booth's multiplier in this task comprises of Modified Booth Encoded (MBE), sign expansion corrector. incomplete item generators lastly a viper [2]. This technique is utilized to build speed by lessening the quantity of incomplete items significantly. Since a 8-bit stall multiplier is utilized in this undertaking, just four incomplete items should be included rather than eight. The engineering of adjusted Booth is appeared in figure 1.

#### **Modified Booth Encoder (MBE)**

Adjusted Booth encoding is utilized to maintain a strategic distance from variable size halfway item clusters. The multiplier B must be changed over into a Radix-4 number by separating them into three digits individually as per Booth Encoder Table given beneath. Prior to changing over the multiplier, a zero is affixed into the Least Significant Bit (LSB) of the multiplier. The multiplier has been divided into four allotments and subsequently four halfway items will be created utilizing changed corner multiplier approach rather than eight fractional items being produced utilizing an ordinary multiplier. For eg. Convert a 8-bit number into a Radix-4 number. Give the number a chance to be -  $36 = 1 \ 0 \ 1 \ 0$ . A '0' must be attached to the LSB. Consequently the new number is 1 0 1 0. Further, it is encoded into Radix-4 numbers as per the table I. Beginning from right we have 0\*Multiplicand, - 1\*Multiplicand, 2\*Multiplicand, - 1\*Multiplicand.

Halfway Product Generator (PPG) Partial item generator is the blend circuit of the item generator and the 5 to 1 MUX circuit. By duplicating the multiplicand by 0, 1, - 1, 2 or - 2, fractional items are produces utilizing item generator. A 5 to 1 MUX is intended to figure out which item is picked relying upon the M, 2M, 3M control flag which is created from the MBE. For item generator, duplicate by zero means the multiplicand is increased by "0". Duplicate by "1" implies the item continues as before as the multiplicand esteem. Duplicate by "-1" implies that the item is the two's supplement type of the number. Duplicate by "- 2" is to move left one piece the two's supplement of the multiplicand esteem and increase by "2" implies simply move left the multiplicand by one place.

# **PROPOSED**MODELFORMULTIPLIER DESIGN:

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

#### Description:

- 1. The proposed configuration intends to outline a multiplier less multiplier for FIR DA engineering.

- 2. To stress on this FIR channel engineering we have to propose a specfic multipier which would diminish the multifaceted nature and furthermore the power and region contemplations.

- 3. Here, we have proposed a blended half and half multiplier for both ordinary and coasting point augmentation in light of the contribution for thr FIR filters.As we realize that each channel would comprising of coefficients and info varieties/yield varieties in view of the struture choosen for the actualizing the FIR channel.

- 4. By and by we have proposed a DIGITAL FIR DA Architecture. The structure and its advanced apprach have been explaind beneath.

- 5. This plan is contrasted and the present channel structure display as appeared in figure where our outline would manage both multiplier and multiplier less condition.

- 6. According to the outline documentation, we have assessed and computed the particular coeefficients which would portray the DA archtecture an appeared in figure.

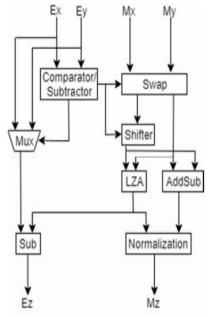

#### FLOW DIAGRAM FOR FLOATING POINT MULTIPLIER DESIGN MODEL:

www.ijiemr.org

Figure: Representing the Floating point model for DA architecture

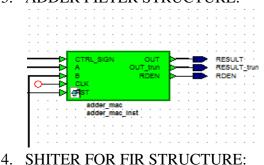

#### PROPOSED MODEL FOR FIR FILTER ARCHITECTURE:

**Realization of 16 Tap Filter Based on Multiplier Less Architecture:**

#### Description:

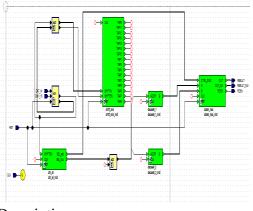

The above outline is a DA acknowledgment circuit chart for 16 tap channel. This channel configuration

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

consolidated with particular auxiliary squares, for example,

1. CONTROL LOGIC:

2. Lut For Filter Architecture For Multipler Less Design:

- Here we have watched an aggregate of 4 modules which are being used for multiplier less DA FIR channel design.

- 2. As we realize that we could gauge the multifaceted nature in light of the structure and its application purpose of usage in ral time viewpoint. This plan is more expected to work for DA FIR channel engineering where we proposed both multipleir and multiplier less design. Every module would produce specific ouputs for age of right dispersed engineering channel plan.

- 3. Considering the structure as appeared underneath we have ROM/LUT as the storable unit for each coeefcient or even specfic input esteems are being put away with the end goal that the multifaceted nature for each circle of the yield created is decreased and in like manner the calculation is required to have an estimations of nlog(n).

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

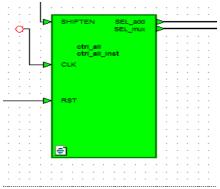

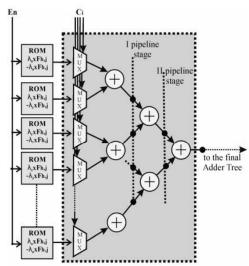

FLOW DIAGRAM FOR DA ARCHITECTURE:

FILTER DESIGN:

Distributed Arithmetic for 3rd order Filter

Coefficients = 4,

No. of inputs = 4

LUT size = 24 = 16 memory location

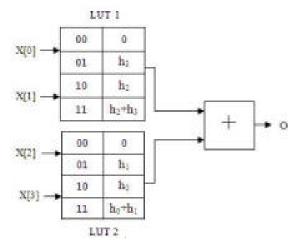

In this strategy, conceivable yields are pre-registered and put away in LUT.LUT is tended to through the contribution of the channel. For 4 tap channel, 4 tap speaks to the no. of the coefficient of the channel and additionally it speaks to the no. of contributions to the channel and address bit for the LUT. Table 2 demonstrates the substance of the LUT for third request channel

For comparing inputs, every area of LUT is appointed to various yields. The conceivable contributions for third request channel are 0(0000) - 15(1111). The yield is figured for each info utilizing the system demonstrated as follows.

Input = 1011 means Output = 1.h0 + 0. h1 + 1.h2 + 1.h3 = h0 + h2 + h3Input = 1111 means Output = h0+h1+h2+h3Input = 0101 means Output = h1+h3Input = X0, X1, X2, X3 X0 = 1011=11 X1 = 1101=13 X2 = 1010=10 X3 =1001=9 h0 = h1 = h2 = h3 = 1Step 1: Store the values in input buffer. X0[0] X1[0] X2[0] X3[0] =1101 X0[1] X1[1] X2[1] X3[1] =1010 X0[2] X1[2] X2[2] X3[2] =0100 X0[3] X1[3] X2[3] X3[3] =1111 Stage 2: Read the qualities from LUT for relating esteems in support. Yield of LUT: O1 = 0011 = 3 O2 = 0010 = 2 O3 = 0001 = 1 O4 = 0100 = 4Stage 3: If the esteem is duplicated by 2, it infers left move. Yield = O1 + Shiftthe estimation of O2 one time + Shift the estimation of O3 2 times + Shift estimation of O4 3 times. Yield = 3 + 4+4+32=43. Disadvantage A channel with N coefficients the LUT has 2N esteems. For higher request channel LUT size will expand, it required more memory space. Disseminated Arithmetic utilizing

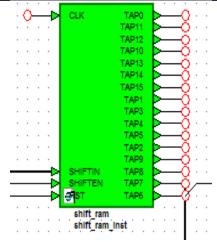

Partition strategy The above DA method holds great just when channels are of low request. For higher request channels, the span of the LUT additionally increments exponentially with the request of the channel. For a channel with N coefficients, the LUT have 2N Consequently, for higher esteems. request channels, LUT size to be diminished to sensible levels. To lessen

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

#### www.ijiemr.org

the size, the LUT can be subdivided into various LUTs, called LUT segments. Each LUT segment works on an alternate arrangement of channel taps. The outcomes got from the allotments are summed. Parcel technique for third request channel Number of segment = 2So, the quantity of LUT'S utilized are 2. Each LUT has 2 inputs. Memory area = no. of segment \* 2n = 2\*22 = 8 areas n =number of contributions of LUT is separated into LUT 1 and LUT 2. Each LUT has 2 sources of info and 4 memory area. It is appeared in figure 4. Info =1011 means First two bits is address bit of LUT 1, yield progresses toward becoming 10 = h0 Remaining 2 bits are address bit of LUT 2, yield moves toward becoming 11 = h2 + h3 Output = yield of LUT1 + yield of LUT 2 = h0+h2 + h3.

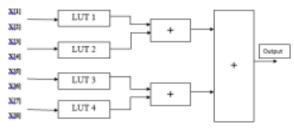

Partition method for 8-tap filter

FIR Filter with 8-tap is utilized in this undertaking. On the off chance that the parcel isn't utilized, at that point the quantity of memory areas that will be utilized is 2^8=256 areas. Along these lines, it will be an exceptionally tedious procedure to compose code for such extensive number of areas. Thus, parcel strategy is utilized in this venture. The design of 8 tap channel with 4 segments is appeared in figure 5.

#### **4. RESULTS** AREA UTILIZATION:

| Device Utilization Summary                     |      |           |             |  |  |  |  |  |

|------------------------------------------------|------|-----------|-------------|--|--|--|--|--|

| Logic Utilization                              | Used | Available | Utilization |  |  |  |  |  |

| Total Number Slice Registers                   | 100  | 178,176   | 1%          |  |  |  |  |  |

| Number used as Flip Flops                      | 95   |           |             |  |  |  |  |  |

| Number used as Latches                         | 5    |           |             |  |  |  |  |  |

| Number of 4 input LUTs                         | 691  | 178,176   | 1%          |  |  |  |  |  |

| Number of occupied Slices                      | 404  | 89,088    | 1%          |  |  |  |  |  |

| Number of Slices containing only related logic | 404  | 404       | 100%        |  |  |  |  |  |

| Number of Slices containing unrelated logic    | 0    | 404       | 0%          |  |  |  |  |  |

| Total Number of 4 input LUTs                   | 704  | 178,176   | 1%          |  |  |  |  |  |

| Number used as logic                           | 691  |           |             |  |  |  |  |  |

| Number used as a route-thru                    | 13   |           |             |  |  |  |  |  |

| Number of bonded <u>IOBs</u>                   | 329  | 960       | 34%         |  |  |  |  |  |

| IOB Flip Flops                                 | 1    |           |             |  |  |  |  |  |

| Number of BUFG/BUFGCTRLs                       | 1    | 32        | 3%          |  |  |  |  |  |

| Number used as BUFGs                           | 1    |           |             |  |  |  |  |  |

| Number of DSP48s                               | 10   | 96        | 10%         |  |  |  |  |  |

| Average Fanout of Non-Clock Nets               | 2.42 |           |             |  |  |  |  |  |

#### POWER UTILIZATION:

| On-Chip | Power (W)  | Used          | Available   | Utilization (%) | Supply | Summary   | Total       | Dynamic     | Quiescent   |

|---------|------------|---------------|-------------|-----------------|--------|-----------|-------------|-------------|-------------|

| Clocks  | 0.026      | 2             |             |                 | Source | Voltage   | Current (A) | Current (A) | Current (A) |

| Logic   | 0.012      | 703           | 178176      | 0               | Vccint | 1.200     | 0.571       | 0.063       | 0.50        |

| Signals | 0.028      | 1293          |             |                 | Vocaux | 2.500     | 0.156       | 0.006       | 0.15        |

| DSPs    | 0.002      | 10            | 96          | 10              | Vcco25 | 2.500     | 0.121       | 0.118       | 0.00        |

| DCMs    | 0.000      | 0             | 12          | 0               |        |           |             |             |             |

| 10s     | 0.320      | 329           | 960         | 34              |        |           | Total       | Dynamic     | Quiescent   |

| Leakage | 0.991      |               |             |                 | Supply | Power (W) | 1.379       | 0.388       | 0.99        |

| Total   | 1.379      |               |             |                 |        |           |             |             |             |

|         |            |               |             |                 |        |           |             |             |             |

|         |            | Effective TJA | Max Ambient | Junction Temp   |        |           |             |             |             |

| Thermal | Properties | (C/W)         | (C)         | (C)             |        |           |             |             |             |

27.5

77,4

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

#### www.ijiemr.org

#### 5. CONCLUSIONS:

In this work different related work has been superior ASICs resuscitated the and capacities of the DSP processors (FFT outline) in the computationally serious applications, for example, advanced flag preparing. Mechanical advancements have caused quickening in the improvement of the region of DSP. One of them is the conceiving of an effective calculation to ascertain the Fast Fourier Transform. What's more they offer the adaptability in equipment and shorter time to showcase. In the in the mean time, multiplier less circuit equipment configuration streams is a testing assignment because of the combination of a few plan instruments and particular engineering that forces configuration difficulties to the creators. The significant goal of this work is to audit ways to deal with diminish the calculation in outlining a circuit and henceforth the equipment assets required for that by formulating a novel technique called distributive and divided engineering strategy.

#### 6. REFERENCES:

[1] S. J. Darak, S. K. P. Gopi, V. A. Prasad, and E. Lai, "Low-complexity reconfigurable fast filter bank for multistandard wireless receivers," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 22, no. 5, pp. 1202–1206, May 2014.

[2] J. L. Nunez-Yanez, T. Spiteri, and G. Vafiadis, "Multistandard reconfigurable motion estimation processor for hybrid video codecs," IET Comput.Digit. Tech., vol. 5, no. 2, pp. 73–85, Mar. 2011.

[3] H. Samueli, "An improved search algorithmfor the design of multiplier less

FIR filters with power-of-two coefficients," IEEE Trans. Circuits Syst., vol. 36, no. 7, pp. 1044–1047, Jul. 1989.

[4] A. G. Dempster and M. D. Macloed, "Use of minimumadder multiplier blocks in FIR digital filters," IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process., vol. 42, no. 9, pp. 569–577, Sep. 1995.

[5] C. Y. Yao, H. H. Chen, T. F. Lin, C. J. Chien, and C. T. Hsu, "Anovel common subexpression elimination method for synthesizing fixed-point FIR filters," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 51, no. 11, pp. 2215–2221, Nov. 2004.

[6] M. Aktan, A. Yurdakul, and G. Dundar, "An algorithmfor the design oflow-power hardware-efficient FIR filters," IEEE Trans. Circuits Syst.I, Reg. Papers, vol. 55, pp. 1536–1545, Jul. 2008.

[7] C. Y. Yao, W. C. Hsia, and Y. H. Ho, "Designing hardware-efficient fixed-point FIR filters in an expanding subexpression space," IEEETrans. Circuits and Systems I, Reg. Papers, vol. 61, no. 1, pp. 202–212, Jan. 2014.

[8] B. Rashidi, "High performance and lowpower finite impulse responsefilter based on ring topology with modified retiming serial multiplieron FPGA," IET Signal Process., vol. 7, no. 8, pp. 743–753, Oct. 2013.

[9] H. Choo, K. Muhammad, and K. Roy, "Complexity reduction of digitalfilter using shift inclusive differential coefficients," IEEE Tans. SignalProcess., vol. 52, no. 6, pp. 1760–1772, Jun. 2004.

[10] J. H. Choi, N. Banerjee, and K. Roy,

"Variation-aware low-power synthesismethodology for fixed point FIR filters," IEEE Trans. Comput.Aided Design

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

Integr. Circuits Syst., vol. 28, no. 1, pp. 87– 97, Jan. 2009.

[11] P. K. Meher, "New approach to lookup-table design and memorybasedrealization of FIR digital filter," IEEE Trans. Circuits Syst. I,Reg. Papers, vol. 57, no. 3, pp. 592– 603, Mar. 2010.

[12] S. Y. Park and P. K. Meher, "Efficient FPGA and ASIC realizations ofDA-based reconfigurable FIR digital filter," IEEE Trans. Circuits Syst.II, Exp. Brief, vol. 61, no. 7, pp. 511–515, Jul. 2014.

[13] R.Mahesh and A. P. Vinod, "Newreconfigurable architectures for implementingFIR filters with low complexity," IEEE Trans. Comput.Aided Design Integr.Circuits Syst., vol. 29, no. 2, pp. 275–288, Feb. 2010.

[14] I. Hatai, I. Chakrabarti, and S. Banerjee, "An efficient VLSI architectureof a reconfigurable pulse-shaping FIR interpolation filter formulti-standard DUC," IEEE Trans. Very Large Scale Integr. (VLSI)Syst., May 2014 [Online]. Available: http://ieeexplore.ieee.org

[15] Y. C. Lim, J. B. Evans, and B. Liu, "Decomposition of binary integersinto signed power-of-two terms," IEEE Trans. Circuits and Systems,vol. 38, no. 6, pp. 667– 672, Jun. 1991. www.ijiemr.org