A Peer Revieved Open Access International Journal

www.ijiemr.org

#### **COPY RIGHT**

2018IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 5th Dec 2018. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-07&issue=ISSUE-12

Title: LOW POWER IMPLEMENTATION OF LUT AND ITS FUTURISTIC APPROACH FOR ADDERESS CYPHERING MODEL FOR MULTPLIERS

Volume 07, Issue 12, Pages: 989-1003.

**Paper Authors**

LINGAIAH JADA, K.SRIDEVI, P.BALA KRISHNA

Arjun College Of Technology & Sciences

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic

Bar Code

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

# LOW POWER IMPLEMENTATION OF LUT AND ITS FUTURISTIC APPROACH FOR ADDERESS CYPHERING MODEL FOR MULTPLIERS

$^{[1]}$  LINGAIAH JADA ,  $^{[2]}$ K.SRIDEVI,  $^{[3]}$  P.BALA KRISHNA

HOD & Associate Professor, Arjun College Of Technology & Sciences

Assistant Professor, Arjun College Of Technology & Sciences

VLSI Design (M.Tech), Arjun College Of Technology & Sciences

#### **ABSTRACT:**

As of late, the counter symmetric item coding (APC) and odd-numerous capacity (OMS) strategies for query table (LUT) outline for memory-based multipliers to be utilized in advanced flag handling applications. The proposed consolidated methodology gives a decrease in query table size to one-fourth of the regular query table. We present an alternate type of Antisymmetric item coding and a changed Odd-different capacity plot, with a specific end goal to consolidate them for proficient memory-based duplication. It is discovered that the proposed query table-based multiplier includes equivalent territory and time many-sided quality for a word size of 8 bits, it includes fundamentally less zone and less increase time than the authoritative marked digit-based multipliers, For 16-and 32-bit word sizes, individually, it offers over 30% and half of sparing in area- defer item over the comparing sanctioned marked digit (CSD) multipliers. We would use our investigation on the LUT-based FPGA innovation mapping issue for postpone minimization under the ostensible defer show, which accept that the interconnect deferral of a net is relative to the fan-out size of the net. At long last, we build up a heuristic LUT mapping calculation for ostensible defer minimization on general Boolean systems. Trial results have demonstrated that our heuristic calculation can create mapping arrangements of littler postponement contrasted and the arrangements of the profundity ideal mapping calculation under the unit defer show.

#### 1. INTRODUCTION

Together with the dynamic gadget scaling and semiconductor memory are less expensive, quicker, and more power-productive. In Addition to that, as indicated by the projections of the universal innovation guide for semiconductors, installed recollections having the overwhelm nearness in the framework on-chips (SOCs),

which may surpass 90% of the aggregate SOC content. Besides, the transistor pressing thickness of memory parts isn't just higher yet additionally expanding substantially quicker than those of rationale segments. Other than that, memory-based figuring structures are more typical than the multiply— collect structures and offer

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

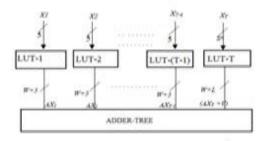

numerous different focal points, as more noteworthy potential for high-throughput, low-inertness execution and less unique power utilization. Memory-based registering is fitting for some advanced flag preparing calculations. which embroil (DSP) duplication with a settled arrangement of coefficients. An ordinary query table (LUT)based multiplier is delineate in Fig. 1, where A will be a coefficient which is consistent, and X is an information word to be increased with A. Think about X as a positive parallel number of word length L, there can be conceivable estimations of X, and appropriately, there can be conceivable estimations of item C = ASubsequently, for memory-based increase, a LUT of words and every conceivable estimation of X contains pre-processed item esteems, is customarily utilized. The item word is put away at the area X-i for 0<Xi<2L, with the end goal that if a L-bit twofold estimation of is utilized as the location for the LUT, at that point the relating item esteem is accessible as its vield. Unmistakable designs have been presented for memory based usage of DSP calculations including symmetrical changes and computerized channels. Be that as it may, we don't locate any critical work on LUT advancement for memory-based duplication. As of late, we have thought of another way to deal with LUT outline, where required the odd products of the settled coefficient to be put away, we alluded it as the odd-various capacity (OMS) plot. Furthermore, we have exhibited that, the counter symmetric item coding (APC) approach, and the LUT size can likewise be diminished to half, where the item words are recoded as hostile to symmetric sets.

Query table (LUT) based FPGA [8, 10] is a famous engineering in which the essential programmable rationale square is a K-input query table (K-LUT), worked in SRAM, which can execute any Boolean capacity of up to K factors. The innovation mapping issue in LUT-based FPGA outlines is to change a general Boolean system into a practically proportional system of K-LUTs by processing a (not really disjoint) K-LUT covering of the system. Broad investigation has been done on the mapping calculations for LUT-based FPGAs as of late. Analysts have concentrated on zone minimization, defer minimization, exchange off among territory and deferral, and routability advancement, and so on.. Endeavors have been made both on the improvement of compelling and effective mapping calculations, and on the investigation of the many-sided quality of the mapping issues. It has been demonstrated that if the system is a tree, or on the off chance that we utilize treebased mapping (i.e. by breaking down a general system into trees and mapping each tree independently), both the territory least mapping issue and the profundity least mapping issue can be illuminated ideally in solid polynomial time [5, 6]. For general Klimited Boolean systems, it is demonstrated that the profundity least mapping issue can be fathomed ideally in solid polynomial time [1], while the zone least mapping issue is NP-hard for K 5 [5]. On the off chance that we permit just sans duplication mapping (i.e. try not to permit hub duplication amid mapping), it has been demonstrated that both the profundity least mapping issue and

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

the zone least mapping issue can be comprehended ideally in polynomial time for any settled K [2]. Postpone minimization has been a vital enhancement objective in FPGA mapping in light of the fact that the speed of FPGA outlines is generally slower than that of the entryway cluster or standard cell plans because of the additional deferral presented by the programmable interconnects on FPGA chips. Most past calculations mapping for postpone minimization utilize the profundity of the mapping arrangement as the estimation of deferral, i.e. in light of the unit defer display, which expect uniform postponement at each rationale level. As appeared in [1], the profundity minimization issue can be understood ideally in polynomial time by productive system stream calculation. In any case, the supposition made by the unit postpone show is more often than not overimproved. In LUT-based FPGA plans, in spite of the fact that the deferral of each LUT is a consistent, the interconnect postponement of each net may fluctuate impressively. Since interconnect delay contributes a critical segment to the aggregate postponement, it is normal to solicit whether this part from deferral can be all the more precisely assessed amid mapping.

# PROBLEM FORMULATION FOR LUT MINIMIZATION:

A combinational Boolean system is spoken to as a coordinated non-cyclic chart in which hubs speak to rationale entryways, and edges speak to interconnects. An essential information (PI) is spoken to by a hub without approaching edge, and an essential yield (PO) is spoken to by a hub without

active edge. The arrangement of fanins of entryway v is indicated input(v), and the arrangement of unmistakable hubs which supply contributions to the doors in sub organize H is meant input(H). Additionally, the arrangement of fanouts of v is meant and the arrangement output(v), unmistakable fanouts of a subnetwork H is meant output(H). The level (or profundity) of a hub v is the quantity of edges on the longest way from any PI hub to v. The profundity of a system is the biggest hub level in the system. A Boolean system is Klimited if jinput(v)j K for each hub v. In this paper we accept that the systems to be mapped are dependably K-limited. For a hub v in the system, a cone of v, signified Cv, is subgraph of rationale entryways comprising of v and its forerunners to such an extent that any way interfacing a hub in Cv and v lies altogether in Cv. The base of Cv is v. The fanin cone of hub v, signified Nv, comprises of v and every one of the ancestors of v. A sans fanout cone (FFC) at v, meant FFCv, is a cone of v with the end goal that for any hub u 6= v in FFCv, output(u) FFCv. A Kfeasible cone of v is a cone Cv with the end goal that jinput(Cv)j K. A cut in a fanin cone Nv of hub v is a bipartition (X; X) of Nv to such an extent that X is a cone of v, and for each PI hub w 2 Nv, w 2 X. On the off chance that X is a K-plausible cone, the cut is known as a Kattainable cut . A K-LUT LU Tv that actualizes hub v covers a Kfeasible FFC Cv of v. On the off chance that Cv isn't fanout free, the nonroot hubs in Cv that have fanouts outside of Cv must be copied with a specific end goal to cover Cv by a K-LUT. Given a Kbounded arrange, the innovation

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

mapping issue for KLUT based FPGA plans is to cover the system with K-practical FFCs, potentially with hub duplications. On the off chance that hub duplication isn't permitted, it is sans duplication mapping. On the off chance that the system is first disintegrated into trees, and each tree is then mapped independently, it is tree-based mapping. Given a hub v, the ostensible deferral related with v is characterized as

$D(LUT_*) = d_L + |output(v)| \cdot d_N$ ; (1) where dL is the postponement of a K-LUT, which is a consistent for a given innovation, and dN > 0 is a steady speaking to the extra deferral because of adding a fanout branch to the net (which is dictated by the innovation, the position/directing devices, and the style of the outline, and so on.). Practically speaking, dN is typically not a steady. Be that as it may, even under such an improved model, the defer minimization issue is substantially more troublesome than the profundity minimization issue in LUT mapping.

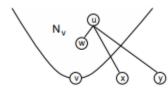

Figure 1: Complication of mapping under the ostensible defer show Under the unit postpone demonstrate, for any hub v, the base profundity of a K-LUT that executes v just relies upon the profundity ideal mapping of the fanin cone Nv of v. This permits the profundity ideal answer for be processed utilizing dynamic programming approach. Under the ostensible postpone demonstrate, in any case, the base deferral of a K-LUT that actualizes v may likewise rely upon the

mapping of hubs outside of Nv . Figure 1 delineates this situation. Give u a chance to be a forerunner of v which has fanouts x and y outside of Nv. On the off chance that the two hubs x and y are pressed into one LUT, the ostensible postponement of hub u diminishes, since the fanout size of u is diminished by one. Then again, if x or y is copied, the ostensible postponement of u will increment. In this manner, delay-ideal mapping of v unmistakably relies upon the mapping of the hubs x and y outside of Nv. This is the innate trouble of ostensible defer minimization in LUT mapping, which prompts the NP-hardness results in the following area.

#### 2. RELATED WORK

Prior to the advanced time, cryptography concentrated on message privacy (i.e., encryption)— change of messages from an intelligible frame into a boundless one and back again at the opposite end, rendering it incoherent by interceptors or spies without mystery information (to be specific the key required for unscrambling of that message). Encryption endeavored to guarantee mystery in correspondences, for example, those of covert agents, military pioneers, ambassadors. In late decades, the field has extended past classification worries to incorporate methods for message trustworthiness checking, sender/collector character verification, advanced marks, confirmations intuitive and secure calculation, among others.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

#### Classic cryptography

# Reconstructed ancient Greek*scytale*, an early cipher device

The principle traditional figure composes are transposition figures, which modify the request of letters in a message (e.g., 'hi world' moves toward becoming 'ehlol owrdl' in an inconsequentially straightforward revamp plan), and substitution figures, which deliberately supplant letters or gatherings of letters with different letters or gatherings of letters (e.g., 'fly without a moment's delay' progresses toward becoming 'gmz bu podf' by supplanting each letter with the one tailing it in the Latin letter set). Basic adaptations of either have never offered much secrecy from ambitious adversaries. An early substitution figure was the Caesar figure, in which each letter in the plaintext was supplanted by a letter some settled number of positions additionally down the letter set. Suetonius reports that Julius Caesar utilized it with a move of three to speak with his officers. Atbash is a case of an early Hebrew figure. The most punctual known utilization of cryptography is some cut ciphertext on stone in Egypt (ca 1900 BCE), yet this may have been improved the situation the beguilement of educated spectators instead of as a method for hiding data.

The Greeks of Classical occasions are said to have known about figures (e.g., the scytale transposition figure professed to have been utilized by the Spartan military). Steganography (i.e., stowing away even the presence of a message to keep it private) was likewise originally created in antiquated occasions. An early precedent, from Herodotus, was a message inked on a slave's shaved head and hid under the regrown hair.[11] More current models steganography incorporate the utilization of undetectable ink. microdots. and computerized watermarks to hide data.

In India, the 2000-year-old Kamasutra of Vātsyāyana talks about two various types of figures called Kautiliyam and Mulavediya. In the Kautiliyam, the figure letter substitutions depend on phonetic relations, for example, vowels getting consonants. In the Mulavediya, the figure letter set comprises of blending letters and utilizing the equal ones.[11] In Sassanid Persia, there were two mystery contents, as per the Muslim creator Ibn al-Nadim: the šāh-dabīrīya (truly "Lord's content") which was utilized for official correspondence, and the raz-sahariya which was utilized to discuss mystery messages with other countries.

First page of a book by Al-Kindiwhich discusses encryption of messages

Page 993

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

Ciphertexts created by an established figure (and some advanced figures) will uncover measurable data about the plaintext, and that data can regularly be utilized to break the figure. After the disclosure of recurrence examination, maybe by the Arab mathematician and polymath Al-Kindi (otherwise called Alkindus) in the ninth century, almost all such figures could be broken by an educated assailant. Such traditional figures still appreciate ubiquity today, however for the most part as riddles (see cryptogram). Al-Kindi composed a book on cryptography entitled Risalah fi Istikhraj al-Mu'amma (Manuscript for the Cryptographic Deciphering Messages), which portrayed the principal known utilization of recurrence investigation cryptanalysis techniques.

16th-century book-shaped Frenchcipher machine, with arms of Henri II of France

Enciphered letter from Gabriel de Luetz d'Aramon, French Ambassador to the Ottoman Empire, after 1546, with partial decipherment

Dialect letter frequencies may offer little for some expanded chronicled help encryption systems, for example. homophonic figure that have a tendency to straighten the recurrence dispersion. For those figures, dialect letter gathering (or ngram) frequencies may give an assault. Basically all figures stayed defenseless against cryptanalysis utilizing the recurrence examination method until the improvement of the polyalphabetic figure, most obviously by Leon Battista Alberti around the year 1467, however there is some sign that it was at that point known to Al-Kindi. Alberti's development was to utilize diverse figures (i.e., substitution letters in order) for different parts of a message (maybe for each progressive plaintext letter at the breaking point). He likewise created what was presumably the main programmed figure gadget, a wheel which actualized a halfway acknowledgment of his innovation. In the Vigenère figure, a polyalphabetic figure, encryption utilizes a catchphrase, which controls letter substitution relying upon which letter of the watchword is utilized. In the mid-nineteenth century Charles Babbage demonstrated that the Vigenère figure was defenseless against Kasiski examination, however this was first distributed around ten years after the fact by Friedrich Kasiski.

In spite of the fact that recurrence investigation can be a ground-breaking and general method against numerous figures, encryption has still regularly been viable by and by, the same number of an eventual cryptanalyst was unconscious of the strategy. Breaking a message without utilizing recurrence investigation basically required learning of the figure utilized and

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

maybe of the key included, accordingly making reconnaissance, gift, thievery, abandonment, and so forth., more appealing ways to deal with the cryptanalytically clueless. It was at long last unequivocally perceived in the nineteenth century that mystery of a figure's calculation is certifiably not a sensible nor functional shield of message security; indeed, it was additionally understood that any satisfactory cryptographic plan (counting figures) ought to stay secure regardless of whether the enemy completely comprehends the figure calculation itself. Security of the key utilized should alone be adequate for a decent figure to keep up privacy under an assault. This unequivocally crucial rule was first expressed in 1883 by Auguste Kerckhoffs and is for the most part called Kerckhoffs' Principle; then again and all the more obtusely, it was repeated by Claude Shannon, the innovator of data hypothesis the essentials of hypothetical and cryptography, as Shannon's Maxim—'the foe knows the framework'. Distinctive physical gadgets and helps have been utilized to help with figures. One of the most punctual may have been the scytale of antiquated Greece, a bar as far as anyone knows utilized by the Spartans as a guide for a transposition figure (see picture above). In medieval occasions, different guides were imagined, for example, the figure grille, which was additionally utilized for a sort of steganography. With the creation of polyalphabetic figures came more refined guides, for example, Alberti's own figure plate, Johannes Trithemius' tabula recta plan, and Thomas Jefferson's wheel figure openly rehashed (not known, and

autonomously by Bazeries around 1900). Numerous mechanical encryption/decoding gadgets were created right off the bat in the twentieth century, and a few protected, among them rotor machines—broadly including the Enigma machine utilized by the German government and military from the late 1920s and amid World War II. The figures executed by better quality models of machine outlines achieved significant increment in cryptanalytic trouble after WWI.

#### 3. IMPLEMENTATION

# LUT RELATED WORK IN SRAM DESIGN:

Look-Into Tables (LUTs) in a FPGA offer liberal adaptability in executing rationale capacities. LUT is a multiplexer (MUX) with a - bit memory [1]. Since MUX is a widespread rationale obstruct; a - input LUT can execute any - variable Boolean capacity. A few LUTs are assembled together to frame bigger totals called Configurable Logic Blocks (CLBs) or basically bunches. LUTs inside a CLB are associated by means of intra-grouping steering system, while CLBs are associated with one another through a configurable directing system. Notwithstanding, this adaptability in a FPGA comes to the detriment of region and execution overheads [2] when contrasted and their Application Specific Integrated Circuits (ASICs) partners, which exceptionally streamlined for a specific class of utilizations. Henceforth, the plain component of FPGAs that makes them exceptional is additionally in charge of their mediocre execution to ASICs.

To connect this hole among FPGAs and ASICs, FPGA designs have been under

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

constant redesign, as far back as their initiation. Beforehand distributed articles, for example, [3–6] endeavor to investigate the ideal qualities for coarser design level points of interest, for example, bunch measure (), the quantity of contributions to a group (), and the cross-bar topologies [7, 8]. FPGA's reconfigurable steering system, its switch box, and association encloses have additionally been investigated detail. In the previous couple of years, some exploration has been engaged towards investigating creative rationale obstructs for FPGA, for example, [9- 11], which can bargain adaptability for enhancing region and execution. The rationale square structures proposed in these works [9- 12] supplant heritage LUTs with imaginative high inclusion rationale components got from every now and again showing up rationale capacities. The thought depends on the way that not all rationale capacities show up with a similar recurrence in computerized circuits [9, 12]. The majority of the designs examined above use the idea of NPN-class proportionality to describe the recurrence with which rationale capacities happen in a circuit. The utilization of NPN-proportional classes expels the excess (on account of LUTs) inborn to FPGAs with some minimal high inclusion rationale squares. Different specialists have endeavored to enhance FPGA rationale hinders on a coarser design level which incorporate [14, 15]. A SRAM table sharing based CLB shares a solitary SRAM table between at least two LUTs, where all the LUTs sharing a solitary SRAM table guide NPN-proportional capacities. The novel SRAM table sharing based CLB proposed in has been enhanced and

additionally investigated in this examination work. The fundamental disadvantage of the rationale squares proposed in [9–11] is that they are determined based on NPNproportional classes for specific benchmark suite; subsequently, they offer top of the line productivity just for the circuits from which their NPN classes were inferred. For instance, the rationale squares of [9] perform surprisingly for the MCNC benchmarks, while for the VPR benchmark suite they neglect to give inclusion to the greater part of the habitually showing up rationale capacities. Be that as it may, the SRAM table sharing based CLB is sufficiently bland to give region advantages to any arrangement of benchmark circuits. In the interim, a considerable measure of research has additionally been coordinated towards designs with diminished number of arrangement memory cells. Designs, for example, [14–17] fall in this classification. The work in uses the idea of Shannon Decomposition to trim down a bigger information work into two littler ones, where one of the halfway capacities has not as much as factors. The rationale squares (named as Extended-LUT) used to delineate capacities require fewer arrangement memory bits than the regular LUTs. The creators of gauge upgrades in region profundity item, without playing out the place and course analyzes. Thus, the proficiency of their proposed Extended-LUT stays unclear. Additionally the proposed rationale cells are not completely permutable, which may bring about directing overheads. Another investigation presents the Scalable Logic Module (SLM) design which like makes utilization of the

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

Shannon Decomposition to discover NPN-identical interconvertible fractional capacities, which can permit the sharing of their memory tables. The outcomes demonstrate that a high level of capacities with input size of 5– 7 can be disintegrated into interconvertible halfway capacities.

Kimura et al. proposed work collapsing to lessen the quantity of arrangement memory bits. Reality table of a capacity is isolated into 2 sections; every bit of relevant information table is then remade utilizing just a solitary part, while the other half is separated utilizing NOT, bit-wise OR, or some other reasonable activity. Be that as it may, does exclude postpone results.

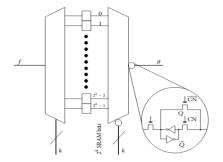

This work utilizes a novel CLB to lessen the quantity of setup memory bits. The decrease in setup memory bits will lessen the region of the FPGA design, as well as the arrangement time and the span of the outside memory used to store the bitstream. The CLB proposed in permits sharing of memory vectors between 2 LUTs (as appeared in Figure 1) on which NPNproportionate capacities are mapped. To acknowledge **NPN** identicalness equipment level, the data sources and yield of one of the two shared LUTs are nullified of with the assistance contingent invalidation (CN) hinder, as appeared in Figure 1(b). To permit sharing of SRAM NPN-identical tables between two capacities, an extra hardware, contingent invalidation (CN) rationale is added to the I/Os of one of the two shared LUTs which share their SRAM vectors.

Figure 1: (a) LUTs with shared SRAM vectors and (b) CN logic.

PROPOSED MODEL FOR DESIGN OF LUT BASED MULTIPLER (LUT MINIMAZATION ALGORITHMS):

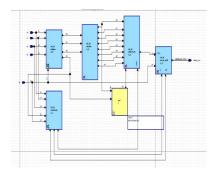

Figure: Representing the LUT address random scheme for Multiplier design.

Figure: Internal modeling for Address generator

From the plan perspective we could dissect the current advanced methodology for the idea for LUT minimization where every

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

calculation is connected and changed over into computerized equipment demonstrating. Considering such application arranged plan demonstrate we could gauge and break down its structures in view of the putting away of every component in LUT stockpiling and its working area as LUT is being used to outline the multiplier.

#### **DESIGN FLOW:**

It is appeared in that, for the augmentation of any double word X of size L, with a settled coefficient A, rather than putting away all the 2L conceivable estimations of C = A · X. Just words relating to the odd products of A might be put away in the LUT, while all the even products of A could be inferred by left-move activities of one of those odd products. In view of all over, the LUT for the duplication of a L-bit contribution with a W-bit coefficient can be outlined by the accompanying technique.

- 1) A memory unit of [ + 1] expressions of (W + L)- bit width is utilized to store the item esteems, where the primary words are odd products of An, and the last word is zero.

- 2) A barrel shifter is utilized for creating a most extreme of (L-1) left moves to infer all the even products of A.

- 3) The L-bit input word is mapped to the (L 1)- bit address of the LUT by a location encoder, and control bits for the barrel shifter are inferred by a control circuit.

| input $X'$ $x'_3x'_2x'_1x'_0$ | product<br>value | # of<br>shifts | shifted input, X" | stored APC<br>word | address<br>d <sub>3</sub> d <sub>2</sub> d <sub>1</sub> d <sub>0</sub> |  |

|-------------------------------|------------------|----------------|-------------------|--------------------|------------------------------------------------------------------------|--|

| 0 0 0 1                       | A                | 0              |                   |                    |                                                                        |  |

| 0 0 1 0                       | $2 \times A$     | 1              | 0001              | P0 = A             | 0000                                                                   |  |

| 0 1 0 0                       | $4 \times A$     | 2              | 0001              | 10-11              | 0000                                                                   |  |

| 1000                          | 8×A              | 3              |                   |                    |                                                                        |  |

| 0 0 1 1                       | 3.4              | 0              | (Josephin)        | est described      | Sonomer                                                                |  |

| 0 1 1 0                       | $2 \times 3A$    | 1              | 0011              | P1 = 3A            | 0001                                                                   |  |

| 1 1 0 0                       | $4 \times 3A$    | 2              |                   |                    |                                                                        |  |

| 0.1.0.1                       | 5.4              | 0              | 0101              | P2 = 5A            | 0010                                                                   |  |

| 1 0 1 0                       | $2 \times 5A$    | 1              | 4.4.              | 12-04              | 0010                                                                   |  |

| 0.111                         | 7.4              | 0              | 0111              | P3 = 7A            | 0011                                                                   |  |

| 1110                          | $2 \times 7A$    | 1              | 0111              | ra-in              | 0011                                                                   |  |

| 1001                          | 9.4              | 0              | 1001              | P4 = 9A            | 0100                                                                   |  |

| 1011                          | 11A              | 0              | 1011              | P5 = 11A           | 0101                                                                   |  |

| 1101                          | 13A              | . 0            | 1101              | P6 = 13A           | 0110                                                                   |  |

| 1111                          | 15.4             | 0              | 1111              | P7 = 15A           | 0111                                                                   |  |

In Table II, we have demonstrated that, at eight memory areas, the eight odd products,  $A \times (2i + 1)$  are put away as, for I = 0, 1, 2,..., 7. The even products 2A, 4A, and 8A are determined by left-move tasks of A. Additionally, 6A and 12A are inferred by left moving 3A, where as 10A and 14A are determined by left moving 5A and 7A, individually. A barrel shifter is utilized for creating a greatest of three remaining movements to infer all the even products of A. From (3), the word to be put away for X = (00000) isn't 0 however 16A, which acquired from A by performing four remaining movements utilizing a barrel shifter.

Execution Of The LUT Multiplier Using APC

For L = 5, The structure and usefulness of the LUT-based multiplier for L = 5 that uses the APC method is make sense of in Fig. 2. It comprises of a four-input LUT of 16 words to store the APC estimations of item words as given in the 6th segment of Table I, aside from on the last line. Where 2A is put away for input X = (00000) rather than putting away a "0" for input X = (10000).

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

Plus, it contains a location mapping circuit and an include/subtract circuit. The coveted location like can be produced utilizing address-mapping circuit, that should be possible by multiplexing XL and utilizing x4 as the control bit. As appeared in the Fig.2, address-mapping circuit can be enhanced to be acknowledged by three XOR doors, three AND entryways, two OR doors, and a NOT entryway. Note that the RESET can be produced by a control circuit (not appeared in this figure) as indicated by (2.1). The yield of the LUT is included with or subtracted from 16A, for x4 = 1 or 0, individually, as indicated by (2.2) by the include/subtract cell. Henceforth, x4 is utilized as the control for the include/subtract cell.

| Ž. | input X product encoded values word |   |   |   |     | # of<br>shifts | address<br>d <sub>3</sub> d <sub>2</sub> d <sub>1</sub> d <sub>0</sub> |   |      |

|----|-------------------------------------|---|---|---|-----|----------------|------------------------------------------------------------------------|---|------|

| 1  | 0                                   | 0 | 0 | 0 | 16A | 0              |                                                                        |   |      |

| 0  | 0                                   | 0 | 0 | 0 | 0   | 16A            | 2A                                                                     | 3 | 1000 |

#### TABLE 3:

B. Implementation of the Optimized LUT Using Modified OMS

As proposed, the APC- OMS joined plan of the LUT for L = 5 and for any coefficient width W is appeared in Fig. 3. It comprises of a LUT of nine expressions of (W + 4)- bit width, a four-to-nine-line address decoder, a location age circuit, a barrel shifter, and a control circuit to create the both RESET flag and control word (s1s0) for the barrel shifter. The pre-processed estimations of A  $\times$  (2i + 1) are put away as Pi, for I = 0, 1, 2, . . . , 7, at the eight sequential areas of the memory exhibit, as indicated in Table II, and 2A is put away at LUT address "1000" for input X = (00000), as determined in

Table III. The decoder takes the 4-bit address from the location generator and produces nine word-select signs, i.e.,  $\{wi, for 0 \le I \le 8\}$ , to choose the referenced word from the LUT. The 4-to-9-line decoder is a basic change of 3-to-8-line decoder, as appeared in Fig. 2 and 3. The control bits s0 and s1 to be utilized by the barrel shifter to deliver the coveted number of movements of the LUT yield that are produced by the control circuit in light of the relations.

Note that (s1s0) is a 2-bit twofold likeness number the required of movements determined in Tables II and III. The RESET flag given by (3) can then again be produced as (d3 AND x4). The control circuit to create the control word and RESET is appeared in Fig. 4(3). The location generator circuit gets the 5-bit input operand X and maps that onto the 4-bit address word (d3d2d1d0), as indicated by (3) and (4). A streamlined location generator is exhibited later in this segment.

C. Optimized LUT Design for Signed and Unsigned Operands

The APC- OMS joined advancement of the LUT can likewise be performed for marked estimations of An and X. At the point when the two operands are in sign-greatness shape, the products of extent of the settled coefficient are to be put away in the LUT, and the indication of the item could be gotten by the XOR activity of sign bits of the two multiplicands. At the point when the two operands are in two's supplement frames, a two's supplement activity of the yield of the LUT is required to be performed for x4 = 1. There is no compelling reason to include the settled esteem 16A for this situation, in light of the fact that the item

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

esteems are normally in hostile to symmetric frame. The include/subtract circuit isn't required in Fig. 2, rather than that a circuit is required to play out the two's supplement activity of the LUT yield. For the augmentation of unsigned information X with marked, and in addition unsigned, coefficient A, the items could be put away in two's supplement portrayal, and include/subtract circuit in Fig could be changed as appeared in Fig. A clear execution of sign-adjustment circuit includes multiplexing of the LUT yield and its two's supplement. To diminish the area- time intricacy over such clear execution, we talk about here a straightforward plan for sign adjustment of the LUT yield.

Note that, with the exception of the last word, every single other word in the LUT are odd products of A. The settled coefficient could be even or odd, however in the event that we expect A to be an odd number, at that point the all the put away item words (with the exception of the last one) would be odd. In the event that the put away esteem P is an odd number, it tends to be communicated as

$$P = P_{D-1} P_{D-2} \cdots P_1 1$$

Where, Pi' is the one's supplement of Pi for  $1 \le I \le D-1$ , and D=W+L-1 is the width of the put away words. On the off chance that we store the two's supplement of the whole item esteems and change the indication of the LUT yield for =1, at that point the indication of the last LUT word require not be changed. In light of, we can in this way have a straightforward signalteration circuit when An is an odd number. Be that as it may, the settled coefficient A

could be even too. At the point when A will be a nonzero considerably whole number, we can express it as  $Ai' \times 2l$ , where  $1 \le l \le D-1$  is a whole number, and is an odd whole number. Or maybe putting away products of An, it is conceivable to store products of Ai' in the LUT, and the LUT yield can be left moved by l bits by a hardwired shifter. Also, we can have a location age circuit as appeared in Fig., since all the moved location (aside from the last one) is an odd whole number.

In spite of the fact that the memory center of the LUT multiplier is lessened to almost one-fourth by the proposed improvement procedure, it isn't effective for operands of little widths, since it requires a viper to include the counterbalance esteem. Be that as it may, it could be utilized for duplication with contribution of substantial word estimate by an information decay conspire. At the point when the width of the info multiplicand X is huge, coordinate usage of LUT multiplier includes a substantial LUT. Along these lines, the information word could be deteriorated into a specific number of sections or sub words, and the incomplete items relating to various sub words could be move added to get the coveted item as talked about in the accompanying.

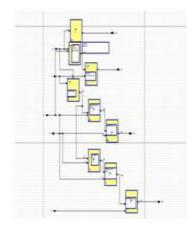

Figure: LUT BASED MULTIPLIER DESIGN STRUCTURE

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

#### 4. RESULTS:

Figure: Representing the address scheme for the design of LUT storage.

Presently, considering the investigation for reproduction we have considered particular qualities for every info cases, for example, x1, x2,x3,x4 where every incentive for these would allocate a capacity component where in every model for x4 would fluctuate the location components for the putting away of each LUT information.

FIGURES: FOR ESTIMATING THE CORRECT SEQUENCE OF LUT ACCESSIBILITY

#### MULTIPLIER REPORT:

Figure: Representing the multiplier initial condition:

Here we have introduced the rst = 0 for all the givn modules to be slated as zero yield

and after adjustment for the rst =1 the qualities are slated to configuration process condition

Figure Representing the input variation as 10011011 and 01110011.

Figure: Representing the design input variation for the multiplier condition

# SYNTHESIS REPORT: AREA UTILIZATION:

| Device Utilization Summary                     |      |           |             |  |  |  |  |  |  |  |

|------------------------------------------------|------|-----------|-------------|--|--|--|--|--|--|--|

| Logic Utilization                              | Used | Available | Utilization |  |  |  |  |  |  |  |

| Number of Slice Latches                        | 4    | 178,176   | 1%          |  |  |  |  |  |  |  |

| Number of 4 input LUTs                         | 14   | 178,176   | 1%          |  |  |  |  |  |  |  |

| Number of occupied Slices                      | 7    | 89,088    | 1%          |  |  |  |  |  |  |  |

| Number of Slices containing only related logic | 7    | 7         | 100%        |  |  |  |  |  |  |  |

| Number of Slices containing unrelated logic    | 0    | 7         | 0%          |  |  |  |  |  |  |  |

| Total Number of 4 input LUTs                   | 14   | 178,176   | 1%          |  |  |  |  |  |  |  |

| Number of bonded IOBs                          | 8    | 960       | 1%          |  |  |  |  |  |  |  |

| IOB Latches                                    | 4    |           |             |  |  |  |  |  |  |  |

| Number of BUFG/BUFGCTRLs                       | 1    | 32        | 3%          |  |  |  |  |  |  |  |

| Number used as BUFGs                           | 1    |           |             |  |  |  |  |  |  |  |

| Average Fanout of Non-Clock Nets               | 2.63 |           |             |  |  |  |  |  |  |  |

#### MULTIPLIER UTILIZATION

| Device Utilization Summary                     |      |           |             |  |  |  |  |  |  |  |

|------------------------------------------------|------|-----------|-------------|--|--|--|--|--|--|--|

| Logic Utilization                              | Used | Available | Utilization |  |  |  |  |  |  |  |

| Number of Slice Flip Flops                     | 357  | 178,176   | 1%          |  |  |  |  |  |  |  |

| Number of 4 input LUTs                         | 704  | 178,176   | 1%          |  |  |  |  |  |  |  |

| Number of occupied Slices                      | 395  | 89,088    | 1%          |  |  |  |  |  |  |  |

| Number of Slices containing only related logic | 395  | 395       | 100%        |  |  |  |  |  |  |  |

| Number of Slices containing unrelated logic    | 0    | 395       | 0%          |  |  |  |  |  |  |  |

| Total Number of 4 input LUTs                   | 736  | 178,176   | 1%          |  |  |  |  |  |  |  |

| Number used as logic                           | 704  |           |             |  |  |  |  |  |  |  |

| Number used as a route-thru                    | 32   |           |             |  |  |  |  |  |  |  |

| Number of bonded IOBs                          | 69   | 960       | 7%          |  |  |  |  |  |  |  |

| Number of BUFG/BUFGCTRLs                       | 1    | 32        | 3%          |  |  |  |  |  |  |  |

| Number used as BUFGs                           | 1    |           |             |  |  |  |  |  |  |  |

| Average Fanout of Non-Clock Nets               | 4.69 |           |             |  |  |  |  |  |  |  |

An estimation for the region and the power have been organized as appeared above figures 1:2, and for control 3:4. Presently, as we realize that with utilization of the LUT minimization calculation in address plot

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

stockpiling for the plan parameters we could assess the execution as appeared. T

#### POWER UTILIZATION:

| On-Chip Power Summary |           |     |       |      |    |      |   |           |   |             |     |

|-----------------------|-----------|-----|-------|------|----|------|---|-----------|---|-------------|-----|

| ı                     | On-Chip   | ı   | Power | (mW) | ı  | Used | Ī | Available | Ī | Utilization | (%) |

| 1                     | Clocks    |     |       | 9.05 | 1  | 3    | 1 |           | ī |             |     |

| ĺ                     | Logic     | - 1 |       | 0.00 | ī. | 14   | Ī | 178176    | i |             | 0   |

| ı                     | Signals   | - 1 |       | 0.00 | T  | 31   | Ī |           | ĺ |             |     |

| ĺ                     | IOs       | - 1 |       | 0.00 | ī. | 8    | Ī | 960       | i |             | 1   |

| ĺ                     | Quiescent | - 1 | 134   | 4.28 | Ĭ. |      | Ī |           | i |             |     |

| ı                     | Total     | i   | 135   | 3.33 | ï  |      | i |           | i |             |     |

#### LUT POWER UTILIZATION

| I |           | On-Chip Power Summary |       |       |   |      |   |           |   |             |     |   |

|---|-----------|-----------------------|-------|-------|---|------|---|-----------|---|-------------|-----|---|

| Ī | On-Chip   | I                     | Power | (mW)  | ı | Used | ī | Available | ī | Utilization | (%) | ī |

| ī | Clocks    |                       | 8     | 33.87 | 1 | 1    | ī |           | ī |             |     | ī |

| i | Logic     | 1                     |       | 0.00  | ī | 736  | i | 178176    | i |             | 0   | i |

| Ī | Signals   | - 1                   |       | 0.00  | 1 | 635  | 1 |           | 1 |             |     | 1 |

| Ī | IOs       | - 1                   |       | 0.00  | 1 | 69   | 1 | 960       | 1 |             | 7   | 1 |

| Ī | Quiescent | 1                     | 135   | 50.88 | 1 |      | 1 |           | 1 |             |     | 1 |

| i | Total     | - 1                   | 143   | 34.75 | 1 |      | 1 |           | 1 |             |     | ī |

So also, we had evaluated the plan for the diverse consistent units, for example, multiplier where every module would assess the power attributes in view of the clk connected on the individual module.

# MULTIPLIER WITH LUT POWER UTILIZATION

The proposed LUT multipliers for word estimate L = W = 8, 16, and 32 bits are coded in VHDL and combined by HDL Designer arrangement and Xilinx 14.2and the LUTs execution is meant with exhibits. Increments are executed by the Wallace tree and swell convey exhibit. The CSD-based multipliers having a similar expansion plans are likewise incorporated with a similar innovation library. Zone and postpone complexities of the multipliers evaluated from the union outcomes are recorded in Table IV. It is discovered that the proposed LUT configuration concern similar territory and time complexities for a word size of 8 bits, yet for higher word sizes, it concern essentially less zone and less augmentation time than the CSD-based multiplier. For L =W = 16, and 32 bits, separately, it offers over 30% and half of sparing in areapostpone item (ADP) over the CSD multiplier.

The likelihood of utilizing LUT based multipliers actualize the steady to duplication for **DSP** applications examined. The full points of interest of proposed LUT based outline, nonetheless, could be inferred if the LUTs are actualized as NAND or NOR read-just recollections and the number juggling shifts are executed by a cluster barrel shifter utilizing metaloxidesemiconductor transistors Additionally work should in any case be possible to determine OMS- APC-based LUTs for higher info sizes with various types of deteriorations and parallel and pipelined option plans for reasonable areapostpone tradeoffs.

#### **COMPARITION TABLE:**

| SN | PARAME  | EXISTING | PROPOSED |

|----|---------|----------|----------|

| О  | TERS    | DESIGN   | DESIGN   |

|    |         |          |          |

| 1. | AREA    | 48%      | 14%      |

| 2. | POWER   | 3.4W     | 1.434W   |

| 3. | LATENCY | 405      | 199      |

| 4. | ROUTE   | 26.87ns  | 12.49ns  |

|    | DELAY   |          |          |

| 5. | TOTAL   | 44.78 ns | 28.8 ns  |

|    | DELAY   |          |          |

#### 5. CONCLUSION:

The LUTs are actualized as varieties of constants for proficient usage of region postpone item. The territory and postpone complexities of the multipliers evaluated from the union outcomes are recorded in Table . It is discovered that the proposed LUT configuration includes similar region and time complexities for a word size of 4 bits, yet for higher word sizes, it has nearly less postpone factor. In this short, we have determined the likelihood of utilizing LUT

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

based multipliers for the steady actualize of activities like duplication particularly for DSP applications. Future degree for this will be usage of inferred OMS- APC-based LUTs for higher information sizes for reasonable territory postpone item with various types of disintegrations. Precise postpone displaying is vital in FPGA many-sided innovation mapping. Our quality outcomes appeared in this paper demonstrates that dynamic defer display is hard to utilize straightforwardly. At present we are chipping away at more successful static estimate of dynamic postpone minimization.

#### SCOPE:

LUT MINIMIZATION: An option in contrast to dynamic defer minimization is iterative static postpone minimization by means of criticism from situation and directing.

#### 6. REFERENCES

- [1] Pramod Kumar Meher, "LUT Optimization for Memory-Based Computation" IEEE Transactions on circuits and systems—ii: express briefs, vol. 57, no. 4, april 2010 [2] International Technology Roadmap for Semiconductors. [Online]. Available: http://public.itrs.net/

- [3] P. K. Meher, "New approach to LUT implementation and accumulation for memory-based Multiplication," in Proc. IEEE ISCAS, May 2009, pp. 453–456.

- [4] P. K. Meher, "New look-up-table optimizations for memory-based multiplication," in Pro. Int. Symp.Integr. Circuits (ISIC'09), Dec. 2009, to be published.

- [5] P. K. Meher, "Memory-based Hardware for resourceconstrained digital signal

- processing systems," inProc. 6th Int Conf. ICICS, Dec.2007, pp.1–4.

- [6] P. K. Meher, "Systolic designs for DCT using a lowcomplexity Concurrent convolutional formulation," IEEE Trans. Circuits Syst. Video Technol., vol. 16, no. 9, pp. 1041–1050, Sep. 2006.

- [7] D. F. Chiper, M. N. S. Swamy, M. O. Ahmad, and T. Stouraitis, "Systolic algorithms and a memory-based design approach for a unified architecture for the computation of DCT/DST/IDCT/IDST,IEEE Trans Circuits Syst. I, Reg. Papers, vol. 52, no. 6, pp. 1125–1137, Jun. 2005.

- [8] H.-C. Chen, J.-I. Guo, T.-S. Chang, and C.-W. Jen, "A memory-efficient realization of cyclic convolution and its application to discrete cosine transform," IEEE Trans. Circuits Syst.Video Technol., vol. 15, no. 3, pp. 445–453, Mar. 2005.

- [9] A. K. Sharma, Advanced Semiconductor Memories: Architectures, Designs, and Applications. Piscataway, NJ: IEEE Press, 2003.

- [10] D. F. Chiper, M. N. S. Swamy, M. O. Ahmad, and T. Stouraitis, "A Systolic array architecture for the discrete sine transform," IEEE Trans. Signal Process., vol. 50, no. 9, pp. 2347–2354, Sep. 2002.

- [11] H.-R. Lee, C.-W. Jen, and C.-M. Liu, "On the design automation of The memory-based VLSI architectures for FIR filters," IEEE Trans. Consum. Electron., vol. 39, no. 3, pp. 619–629, Aug. 1993.