A Peer Revieved Open Access International Journal

www.ijiemr.org

## COPY RIGHT

2018IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 5th Dec 2018. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-07&issue=ISSUE-12

Title: LOW POWER IMPLEMEMENTATION AND COMPLEXITY ANALYSIS FOR ROUND ROBIN ARBITER IN NOC

Volume 07, Issue 12, Pages: 975–988.

**Paper Authors**

#### LINGAIAH JADA, N.AMANI

Arjun College Of Technology & Sciences

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic Bar Code

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

### LOW POWER IMPLEMEMENTATION AND COMPLEXITY ANALYSIS FOR ROUND ROBIN ARBITER IN NOC <sup>[1]</sup>LINGAIAH JADA, <sup>[2]</sup>N.AMANI

<sup>1</sup>VLSI Design (M.Tech), Arjun College Of Technology & Sciences, <sup>2</sup>HOD & Associate Professor, , Arjun College Of Technology & Sciences

### **ABSTRACT:**

Network on chip is presently multi day the decision of a processor creator for move of information in a parcel based correspondence framework as traditional transport based correspondence medium isn't versatile with the expanding quantities of centers. In a NoC framework, each center is associated with a nearby switch and every one of the switches are associated by means of correspondence joins. The switches and in addition the correspondence joins devour a lot of intensity which is a noteworthy worry in a NoC based framework. This has prompted the work that has been proposed in this paper. In this paper, we propose a low power NoC switch in view of the rule of clock gating method by changing the judge square of the switch and contrast the outcome and ordinary Round-Robin authority. Here, the idea of clock-gating has been utilized to change the switch which has prompted the decrease of dynamic power.

#### 1. INTRODUCTION

#### NOC INTRODUCTION

As the innovation downsizes, the entryway defer diminishes, yet the wire postpone expands generally and this worldwide wire delay turns into the fundamental factor which can choose the general execution. Troublesome planning conclusion turns into the principle issue among many outline issues which is caused by long worldwide wire delay. Numerous VLSI originators are endeavoring to unravel this long worldwide wire postpone issue through cushion inclusion. In advertisement dition, numerous present System-on-Chips (SoCs) utilize a framework transport to interface a few practical units. The slave unit would follow this framework transport convention to be

synchronized with the ace unit. In any case, these SoC framework transports can bolster just predetermined number of useful units, and in this way will confront scaling issues in heterogeneous MPSoCs (MultiProcessor System-on-Chips) or vast scale CMPs (Chip-MultiProcessors). Despite the fact that a different transport structure with scaffold and transport network structure could be the elective designs, these arrangements still don't scale well and have the inconveniences of high power utilization. Keeping in mind the end goal to tackle these long worldwide wire deferral and versatility issues. examinations numerous proposed the utilization of a parcel based correspondence

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

#### www.ijiemr.org

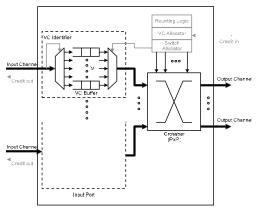

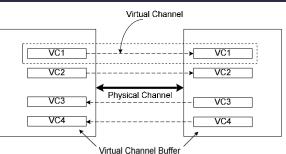

organize which is known as Network-on-Chip (NoC). This NoC is utilized to associate numerous utilitarian units with a widespread correspondence organize [1, 2, 3] .In NoC, a switch sends bundles from a source to a goal switch through a few middle of the road hubs. On the off chance that the head of bundle is hindered amid information transmission, the switch can't exchange the parcel any more. With a specific end goal to expel the blocking issue, the scientist proposed wormhole steering strategy. The wormhole switch parts the parcel into a few bounces which can be moved in a solitary transmission. Support portion and flutter control are performed at a bounce level in wormhole directing since wormhole steering does not assign accessible cradle to entire parcel. There-fore, the wormhole directing is a strategy which can limit generally idleness and may diminish cradle estimate contrasted with others. What's more, virtual channels are utilized to stay away from gridlock issue and in this way increment throughput. The principle reason for virtual channels is to decouple the assignment of cradle space to enable a flutter to utilize a solitary physical channel contending with different dances. Figure 1 demonstrates a virtual channel switch

### [1] . For straightforwardness, a work arrange is utilized as topology and a versatile steering is likewise utilized as a directing system.

Various necessities should be met keeping in mind the end goal to utilize wormhole switch. Every switch needs to trade their credits, which are the data about

what number of VCs are accessible in the contiguous switch. Amid setting up VCs among switches, every switch referees hopeful VCs with this credit data. The transmitting switch needs to keep the acknowledge data, for example, the quantity of accessible free cushions and the quantity of accessible VCs from close-by switches. The accepting switch additionally refreshes the read/compose pointers in inward support control rationale when it gets the bounce from the past switch. Cradles expend much spillage control since cushions, which are executed with registers, involve expansive territories contrasted with other combinational rationales [1]. From [4] the cradles devour around 64 percent of the aggregate switch spillage control. Dynamic power utilization is relative to exchanging action, supply voltage, and capacitance stack. At whatever point the bounce touches base at or leaves from switch, it expends much unique power contingent upon switch movement. In this manner. cradle configuration assumes a vital job in actualizing a vitality proficient on-chip network

Fig. 1. Virtual Channel Router

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

#### www.ijiemr.org

### 2. RELATED WORK:

This proposal draws on and expands on an assortment of related and earlier works in the region of outline of system on-chip cradles, virtual channel distribution (VA) and switch al-area (SA) in the switch. Earlier investigations give ideas and frameworks that will be actualized and additionally refined over the span of the proposed inquire about.

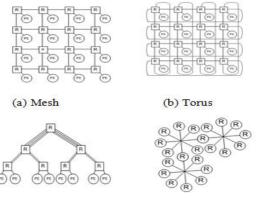

### A. Network-on-Chip Topology

W. J. Hesitate presented Network-on-Chip correspondence and particularly 2D torus architecture in [2]. Kumar et al. [5] utilized 2-D tile-based engineering embracing a work based topology. Work and torus are prominent NoC topologies, and they have distinctive highlights as far as throughput, control utilization, and idleness relying upon defeat ing calculations [6]. Likewise, SPIN organize utilizes the fat tree topology in [3] and octagon topology is proposed in [7]. Every topology has its own trademark. Among postulations topologies, numerous fashioners get a kick out of the chance to utilize work topology due to straightforwardness.

#### **Routing Strategy**

The bundle is routed through systems relying upon a steering technique. The routing algorithms could be one of the accompanying two techniques. Deterministic directing, for example, XY steering is the point at which the courses between given sets of hubs are precustomized and therefore take after a similar way between two hubs. Versatile steering is the point at which the way taken by a bundle may rely upon different parcels, and every switch should know arrange movement status with a specific end goal to maintain a strategic distance from a congested district ahead of time [2].

#### **Dynamic Virtual Channel Allocation**

A non specific switch for the most part utilizes a factually designated support which can cause the Head-of-Line (HoL) blocking issue. [8] proposes cushion customization which de-wrinkles the line blocking likelihood with a specific end goal to enhance the system execution. A plan called dynamic virtual channel controller (ViChaR) is proposed in [9]. In the ViChaR, VCs are dispensed progressively, and support designation for each VC could be diverse relying upon organize activity. For instance, numerous and shallow VCs are more proficient in the light movement, and few and more profound VCs are more effective overwhelming rush hour gridlock. in Likewise, on-chip arrange switch taking care of movement demand must be intended to have minimal number of cushions since the power utilization of the cradle dom-inates the various rationale, for example, VA, SA, and crossbar[9]. ViChaR proposes the technique for expanding cradle usage and diminishing by and large power utilization. From [9] the zone overhead and additional power utilization is insignificant where there is a 4 percent decrease in rationale territory and negligible 2 percent control increment contrasted with square with estimate non specific cradle usage. Particularly, it reports a 25 percent expansion in execution with a similar measure of buffering [9].

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

#### www.ijiemr.org

Progressively Allocated Multi-Queue (DAMQ) cradle engineering is exhibited in [10]. This DAMQ has the bound together and powerfully assigned cushion structure. The idea of DAMQ is comparative with ViChaR. DAMQ utilizes a settled number of lines per input port. Be that as it may, this can cause the HoL blocking issue. Thusly, ViChaR doles out the cushion asset to every one of the VCs as indicated by the system movement to take care of the HoL issue. Completely Connected Circular Buffer (FC-CB) is clarified in [11]. FC-CS is essentially utilizing a Dynamically Allocated Fully Connected (DAFC) strategy [12] so as to have the adaptability in assorted rush hour gridlock by adjusting wormhole steering and virtual channels. Thus, this FC-CB gives a low normal message dormancy and High throughput even under substantial movement. In any case, FC-CB structure has a settled number of VCs and complex rationale to control round cushion and along these lines causes higher unique power utilization.

### System Property

### 1. Topology

Work and torus arrange topologies are chosen as the best decision in a NoC [2]. These two system topologies have straightforwardness of 2-D square structure. Figure 2 (a) demonstrates a 2-D work organize structure [5]. It is made out of a network of level and vertical lines with a switch. This work topology is for the most part utilized since delay among switches can be anticipated in an abnormal state. A switch address is registered by the quantity of even

hubs and the quantity of vertical hubs. 2-D torus topology [2] is a doughnut molded structure which is made by a 2-D work and association of inverse sides as should be obvious in Figure 2 (b). This topology has double the separation data transfer capacity of a work arrange at the expense of a multiplied wire request. Be that as it may, the hubs ought to be interleaved on the grounds that all between hub switches have a similar length. Notwithstanding the work and torus arrange topologies, a fat-tree structure [3] is utilized. In M-ary fat-tree structure, the quantity of associations between hubs increments with a factor M towards the base of the tree. By shrewdly picking the bloatedness of connections, the system can be custom fitted to effectively utilize any transfer speed. An octagon organize was proposed by [7]. Eight processors are connected by an octagonal ring. The deferrals between any two hubs are close to two jumps inside the neighborhood ring. The benefit of an octagon organize has versatility.

### c) Binary Fat Tree (d) Octagon Fig. 2. Example of Four Network Topologies

For instance, if a specific hub can be worked as a scaffold hub, more Octagon system can

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

#### www.ijiemr.org

be included utilizing this extension hub. Figure 2 (c) and (d) demonstrate paired fattree and octagon topologies.

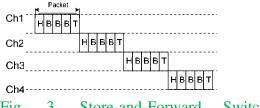

#### Switching Technique

Switching systems decide how organize assets are assigned for information transmission when the info channel is associated with the yield channel chosen by the steering calculation. There are ordinarily four prominent exchanging systems: storeand-forward. virtual slice through, wormhole circuit exchanging, and exchanging [13]. The initial three procedures are ordered into a bundle exchanging strategy. In a store-and-forward exchanging technique, the whole parcel must be put away in the support when a bundle lands at a middle of the road switch. After a parcel arrives, the bundle can be sent to a neighboring hub which has accessible buffering space, accessible to store the whole parcel. This exchanging method requires a great deal of buffering space more than the measure of the biggest bundle. It should expand on-chip the zone. Notwithstanding the region, it could cause huge inertness on the grounds that a specific parcel can't cross to the following hub until the point when its entire bundle is put away. Figure 3 demonstrates a store-and-forward exchanging system and a stream outline.

Fig. 3. Store-and-Forward Switching Technique

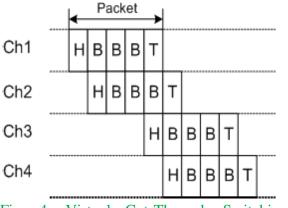

With a specific end goal to tackle long idleness issue in a store-and-forward exchanging plan, virtual slice through exchanging [14] stores a parcel at a middle of the road hub if next switches are occupied, while current hub gets the approaching bundle. In any case, despite everything it requires a great deal of buffering space in the most pessimistic scenario. Figure 4 demonstrates the planning graph for a virtual slice through exchanging strategy. The necessity of vast buffering space can be tackled utilizing the wormhole switch-ing strategy [15]. In the wormhole exchanging technique, the bundles are part to stream control digits (bounces) which are wound along the course in a pipeline mold. There-fore, it doesn't need huge cradles for the entire bundles yet has little supports for a couple of dances. A header flutter construct the directing way to permit other information bounces to tra-stanza in the way. A disservice of wormhole exchanging is that the length of the way is relative to the quantity of flutters in the parcel. Moreover, the header bounce is hindered by clog, the entire chain of dances are slowed down. It additionally blocked different dances. This is called gridlock where organize is slowed down in light of the fact that all cushions are full and round reliance occurs between hubs. The idea of virtual channels [15] is acquainted with present gridlock free directing in wormhole exchanging systems. This strategy can part one physical channel into a few virtual channels. Figure 5 demonstrates the idea of a virtual channel.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

For ongoing spilling information, circuit exchanging bolsters a saved, point-to-point association between a source hub and an objective hub. Circuit exchanging has two stages: circuit foundation and message transmission. Before message transmis-sion, a physical way from the source to the goal is held.

Fig. 4. Virtual Cut-Through Switching Technique

A header flutter lands at the goal hub, and afterward an affirmation (ACK) dance is sent back to the source hub. When the source hub gets the ACK flag, the source hub transmits a whole message at the full data transfer capacity of the way. The circuit is discharged by the goal hub or by a tail flutter. Despite the fact that circuit exchanging has the overhead of circuit association and discharge stage, if an information stream is expansive to amortize the overhead, circuit exchanging will be utilized ceaselessly. Since most Networkon-Chip frameworks require less buffering space and has a low inactivity necessity, the wormhole exchanging strategy with a virtual channel is the most appropriate switching technique.

www.ijiemr.org

As the time of a billion transistors on a solitary chip quick methodologies, all the more Processing Elements (PEs) can be set on a System-on-a-Chip (SoC). Most PEs in anSoCcommunicate with one another by means of transports and memory. As the quantity of transport aces increments in a solitary chip, the significance of quick and ground-breaking directions are fundamental. This makes onchip transport based correspondence a noteworthy test for the framework creator in the current SoC innovation. The correspondence designs must have the capacity to adjust as indicated by the continuous necessities of the PEs. Thus, transport referees are proposed. The judge is an electronic gadgets that apportion access to shared assets. Mediator square assumes essential job in the SoC shared transport correspondence. The bosses on a SoC transport may issue asks for all the while and consequently a judge is required to choose which ace is conceded for transport get to. Transport Arbiter assumes a crucial job in dealing with the solicitations from the ace and reactions from slave (like Acknowledgment flag, Retry, and so forth). The primary target of discretion calculations is to guarantee that just a single ace

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

#### www.ijiemr.org

approaches the transport at some random time, the various experts are compelled to stay in the sit without moving state until the point when they are conceded the utilization of the transport.

The arbiter has 2 plots as takes after.

- 1. Round Robin scheme

- 2. Fixed priority scheme

A specific plan can be modified as required. The round-robin conspire is about timecutting that is we should settle a specific measure of time when each procedure must be executed. It is generally actualized even utilizing break with need for effortlessness. In the event that the undertakings have a moderately approach significance, at that point the round-robin works better, since every one of the errands improve possibility of getting run; we stay away from the circumstance where the assignment with the most minimal need scarcely ever gets run, since there appears to dependably be another undertaking with a higher need. Envision we have to peruse information from various sources.

### **Round Robin Arbiter**

A round-robin arbiter is a reasonable authority which, in the wake of conceding a demand, doles out the least need to that. This can be proficient by creating the following need vector p from the present give vector g. In Verilog, this rationale is given by: dole out next\_p =  $|g ? \{g[n 2:0],g[n-1]\} : p ; In a four-piece round-robin$ authority. On the off chance that a give wasissued on the present cycle, one of the gilines will be high, making pi+1 go high onthe following cycle. This makes the demand alongside the one getting the give most astounding need on the following cycle, and the demand that gets the give least need. On the off chance that no concede is declared on the present cycle, any g is low and the need generator holds its present state. The roundrobin mediator displays solid reasonableness. After a demand is served, it is given the most reduced need. All other pending solicitations will be adjusted before need again turns around with the goal that it tends to be overhauled once more.

### **IMPLEMENTATION:** Proposed Block Diagram:

Figure shows the RTL block diagram of a 6X6 round robin arbiter

### RRB CONCEPT:

A round-robin token passing transport or referee ensures decency (no starvation) among experts and permits any unused timeslot to be assigned to an ace whose round-robin turn is later yet who is prepared at this point. A dependable expectation of the most pessimistic scenario hold up time is another preferred standpoint of the roundrobin convention. The most pessimistic scenario hold up time is corresponding to number of requestors short one. The convention of a round-robin token passing transport or switch mediator functions as takes after. In each cycle, one of the experts (in round-robin arrange) has the most

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

#### www.ijiemr.org

noteworthy need (i.e., claims the token) for access to a mutual asset. On the off chance that the token-holding expert does not require the asset in this cycle, the ace with the following most noteworthy need who sends a demand can be conceded the asset. and the most elevated need ace at that point passes the token to the following expert in round-robin arrange. Here a BA is created to deal with four solicitations. Figure demonstrates the Arbiter square outline for four transport experts. To create transport engineering, Round robin mediator generator (RAG) takes as information the quantity of experts and produces synthesizable Verilog code at the RTL level. FLOW DIAGRAM DESCRIPTION OF **RRB**:

State graph show is utilized for displaying responsive or occasion driven implanted frameworks whose preparing conduct are reliant on state advances. The model portrays the framework conduct with 'states', 'occasions', 'activities' and 'progress'. State is a portrayal of a present circumstance. An occasion is a contribution to the state. The occasion goes about as boosts for state change. Progress is the development starting with one state then onto the next. Activity is a movement to be performed by the state machine. Here we are thinking about just

two experts are asking for transport get to. It comprises of three states- $\Box$  Idle  $\Box$  Master1  $\square$ Master2 areq0 and areq1 are the solicitations produced from master1 and master2 individually. On the off chance that master1 demands for cpu get to then areq0 is set to one and areq1 flag is compelled to be out of gear state. State progress of master1 happens from sit without moving to master1 state. After the fulfillment the information move if on the off chance that areq1 is set the change takes from master1 to master2. In the event that areq1 isn't set at that point progress from master1 to sit out of gear state happens. On the off chance that master2 demands for cpu get to then areq1 is set to one and areq0 flag is compelled to be out of gear state. State change of master2 happens from sit out of gear to master2 state. After the culmination the information move if on the off chance that areq0 is set the change takes from master2 to master1. On the off chance that areq0 isn't set at that point progress from master2 to sit still state occurs.If both the ace's solicitations are set i.e,areq0=1 && areq1=1 then it relies upon the interior flag free. Whenever free flag is set 00 then master1 gets the entrance. Whenever free esteem is set to 01 then master2 gets the entrance.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

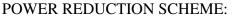

Above Figure demonstrates the clock gating method for the counter by embeddings one AND Gate. Figure demonstrates the yield of counter. From Figure 5 we have seen that when counter is certain edge activated and empower is changing beginning from positive edge to the following positive edge, counter augmentations one additional time, because of small glitch, it gives a wrong yield.

Hook Based AND Gated Clock circuit is appeared in Figure. The empower flag is connected through a hook. Be that as it may, the postponement of the rationale for the calculation of En may fall on the basic way of the circuit and its impact must be considered amid time check. Clock gating of negative edge counter utilizing negative Latch Based AND door Circuit. The revised waveform utilizing hook is appeared underneath Figure. The waveform because of previous and later is delineate by the figure. Round-robin token passing has a solid decency related to it. The most pessimistic scenario hold up time is corresponding to number of requestors less one. In each cycle, one of the bosses (in round-robin arrange) has the most noteworthy need (i.e., claims the token) for access to a common asset.

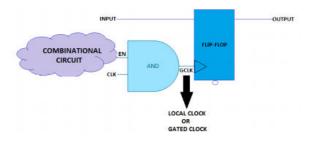

#### ARBITER MODELLED DIAGRAM:

# FIGURE: 6X6 Arbiter model for NOC architecture

Consider the above figure which portrays the 6X6 judge show configuration in view of Verilog execution. Here the demonstrating is centered around the availability of the solicitations and the actuation of the ACTIVE flag which really gives amend reaction of the judge area.

The need of data sources are put in slipping request from in[0] to in[3] in the need rationale squares (Priority Logic 0 through 3) appeared in Figure. Consequently, in[0] has the most elevated need, in[1] has the following need, et cetera. To execute a BA, we utilize the token idea from a token ring in a system. The ownership of the token permits a need rationale square to be empowered. Since every need rationale square has an alternate request of sources of info (ask for signals), the need of demand signals differs with the picked need rationale square. The token is executed in a 4-bit ring counter as appeared in Figure. The yields (four bits) of the ring neutralize as the empower signs to the need rationale squares. In this way, just a single empowered need rationale square can state a give flag. The ack flag to the transport referee is deferred by one intervention cycle by a D flip-slump as appeared in Figure . The postponed ack

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

flag pulls a trigger to the ring counter with the goal that the substance of the ring counter is turned one piece. Consequently, the token piece is turned left each cycle, with 4'b1000 pivoting to 4'b0001 in Figure and the token is introduced to one at the reset stage (e.g., 4'b0001 for four-piece ring counter) so that there is just a single '1' yield by the ring counter. In the round-robin calculation, each ace must hold up no longer than (M1) vacancies, the timeframe assigned to the picked ace, until the point when whenever it gets the token (i.e., most noteworthy need). The relegated schedule opening can likewise be respected another ace if the proprietor of the availability has nothing to send. This convention ensures a dynamic need task to transport aces (requestors) without starvation.

### ARBITER DESIGN ALGORITHM:

The proposed referee plans in particular Real Time\_Staticpriority(RT\_SP), realTime\_Roundrobin. The proposed authority outlines to be specific, genuine Time\_staticpriority(RT\_SP),Real\_Time\_Sta ticpriority(RT\_SP)RealTime\_Roundrobin(R T\_RB), Two-level Dynamic Scheduler and Three-level Dynamic Scheduler are talked about in this segment.

A. RealTime\_Staticpriority (RT\_SP)

The fundamental point of this proposed RT\_SP is to lessen the starvation issue present in the traditional Static Priority calculation at substantial activity conditions. In the proposed RT\_SP, three techniques have been displayed to guarantee low starvation at overwhelming movement conditions.

- B. RT\_SP Method I In this method , following steps are done:

- 1. The bosses are ordered by their need.

2. The regular cautioning line esteem is introduced.

3. The solicitations from the bosses are issued.

4. Static need calculation concedes the most noteworthy need ace.

5. The notice line esteem is checked. On the off chance that the cutoff isn't achieved then the most noteworthy need ace proceeds with its information exchange. In any case, if the point of confinement is achieved, correlation of the staying pending solicitations from the bosses is finished.

6. Presently, the most elevated need ask for out of the pending solicitations is allowed.

7. Once more, Static need based give framework is taken after

8. Stages 4 and 5 are rehashed till no demand is issued from any ace. At the point when there is no demand to be handled Arbitration process stops.

Common warning line: -

The motivation behind this notice line is to consider the lower need experts which are in holding up state, to get give after a specific number of solicitations issued. At first an esteem is set for regular cautioning line. This esteem will decrement from the alloted esteem each time a 'concede' gets created by the static need algorithm.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

### C. RT\_SP Method II

In Method II and Method III the means are comparative as in Method I and just the method for setting the warningline differs. In this Method II, each ace has a different cautioning line. In this way, when an ace has achieved its notice line confine it will be instantly conceded the transport, after the present exchange is finished. Each ace can allocate an alternate an incentive to its notice line

### D. RT\_SP Method III

In this strategy each ace has a different cautioning line. At whatever point an ace issues ask for, its notice line is set to sit tight for specific time length until the point when that ace gets concede flag. Once the holding up time surpasses the point of confinement, that specific ace gets conceded promptly after the present exchange gets finished.

E. RTRB (REAL TIME ROUN ROBIN)

The principle point of this proposed calculation is to dispense with the wastefulness of existing round robin\ calculation. The detriment of the current round robin authority is, it issues allow regardless of whether an ace has not sent any demand. Therefore, that transport cycle will be squandered. Be that as it may, this proposed model will issue give to just asked for aces in a round robin mold. The RT\_RB mediator square outline is appeared in Fig. The authority works in the accompanying way:

1. The experts issue their solicitations.

2. The bosses' solicitations will empower the first OR door and the OR entryway issues a 'HIGH' yield flag.

3. That yield flag will be and worked with ask for flag of ace 1 (Req1).

4. On the off chance that the demand from Master1 is available, i.e. Req1 is HIGH, and after that allow is issued to Master1.

5. Until the point that the Ack flag is gotten from the slave, concede flag to next ace, Master 2 is suspended.

6. Quickly after the landing of Ack flag it is and worked with Req2. In the event that the two data sources are HIGH, at that point the Andgate issues allow flag to Master2. After Master2 has finished its exchange, concede is issued to Master3. After Master3 has finished its exchange, concede is issued to Master4. Along these lines the referee awards thebus to the experts in a round robin mold.

7. On the off chance that the demand is absent for an ace, at that point allow flag is given to the following expert in the request (through the inverter at the yield of the Andgate).

The advantages of RT\_RB are as follows:

• Simple structure

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

#### www.ijiemr.org

- Latency between back to back concede signals is lessened Area and power dispersal is low.

- Removes the drawback of existing round robin arbiter

#### 4. Results

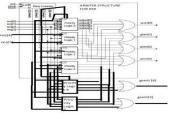

RTL SCHEMATIC FOR ARBITER

STRUCTURE:

### Figure: Representing the Active condition for grant and requests are processed simultaneously.

This figure shows the present condition for the outline parameters considered where each plan esteems are evaluated and displayed as needs be. Presently, we have watched the present dynamic flag changes from the outcomes which would accentuates the right concede restrictive cases for each demand acknowledged.

# Figure: Representing the Initial condition for the design initialization

Think about the figure, which would delineates about the reset condition for the plan where every module information is reset in view of the reset input condition. In present cases we could investigate and gauge the outline in light of the rest condition where the esteem may differ from 0 to 1.

### SYNTHESIS REPORTS:

AREA UTILIZATION FOR 3BIT RRB SCHEDULING ALGORITHM:

| Device Utilization Summary                     |      |           |             |  |  |  |  |

|------------------------------------------------|------|-----------|-------------|--|--|--|--|

| Logic Utilization                              | Used | Available | Utilization |  |  |  |  |

| Number of Slice Flip Flops                     | 13   | 36,864    | 1%          |  |  |  |  |

| Number of 4 input LUTs                         | 79   | 36,864    | 1%          |  |  |  |  |

| Number of occupied Slices                      | 40   | 18,432    | 1%          |  |  |  |  |

| Number of Slices containing only related logic | 40   | 40        | 100%        |  |  |  |  |

| Number of Slices containing unrelated logic    | 0    | 40        | 0%          |  |  |  |  |

| Total Number of 4 input LUTs                   | 79   | 36,864    | 1%          |  |  |  |  |

| Number of bonded IOBs                          | 15   | 448       | 3%          |  |  |  |  |

| Number of BUFG/BUFGCTRLs                       | 1    | 32        | 3%          |  |  |  |  |

| Number used as BUFGs                           | 1    |           |             |  |  |  |  |

| Average Fanout of Non-Clock Nets               | 3.08 |           |             |  |  |  |  |

The use for the region is 10% altogether for the proposed outline for mediator and will be evaluated for the plan advancement in light of the no of the counter and flip-slump used.

### POWER REPORT:

| On-Chip Fower Summary |         |     |           |    |      |   |           |    |             |     |   |

|-----------------------|---------|-----|-----------|----|------|---|-----------|----|-------------|-----|---|

| I                     | On-Chip | P   | ower (mW) | I  | Used | I | Available | I  | Utilization | (%) | I |

| C1                    | ocks    | 1   | 5.18      | T  | 1    | ī |           | T  |             |     | ī |

| Lo                    | gic     | 1   | 0.00      | 1  | 79   | 1 | 36864     | 1  |             | 0   | 1 |

| Si                    | gnals   | 1   | 0.00      | 1  | 101  | Т |           | I. |             |     | 1 |

| 10                    | 3       | 1   | 0.00      | 1  | 15   | Т | 448       | I. |             | 3   | 1 |

| Qu                    | iescent | 1   | 332.86    | 1  |      | Т |           | Т  |             |     | н |

| To                    | tal     | 1.1 | 338.03    | T. |      | Т |           | T. |             |     | 1 |

|                       |         |     |           |    |      |   |           |    |             |     |   |

From the above zone and power outline age for 3bit Arbiter plan we could gauge the base power and control angle for the outline. The power variety is just watched through Timing control circuit where the planning examination for each clock is evaluated. The planning age for each case is examined and advanced for the demand in light of the dynamic condition. Each such dynamic condition would arrive remedy awards for the particular said information input.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

#### www.ijiemr.org

### COMPARITION:

| S  | PARA | EXISTI   | PROPOSE  |

|----|------|----------|----------|

|    |      |          | PROPUSE  |

| Ν  | METE | NG       | D        |

| 0  | RS   | DESIG    | DESIGN(6 |

|    |      | N(4X4)   | X6)      |

| 1. | AREA | 15%      | 10%      |

| 2. | POWE | 1.4W     | 0.338W   |

|    | R    |          |          |

| 3. | LATE | 45       | 19       |

|    | NCY  |          |          |

| 4. | ROUT | 6.87ns   | 2.49ns   |

|    | Е    |          |          |

|    | DELA |          |          |

|    | Y    |          |          |

| 5. | TOTA | 24.78 ns | 7.8 ns   |

|    | L    |          |          |

|    | DELA |          |          |

|    | Y    |          |          |

### 5. CONCLUSION

The proposed idea of usage has given a consolidated answer for clock gating Round Robin mediator generator(C-RAG) outline (4X4). Clock gating innovation can lessen the utilization of clock signs' exchanging intensity of flip-flops. The created BA utilizing Clocks gating Round Robin referee generator (C-RAG) is low power. reasonable, quick, and has a low and unsurprising most pessimistic scenario hold up time. The clock entryway empower capacities can be recognized by Boolean investigation of the rationale contributions for all Clocks gating Round Robin referee generator(C-RAG). Clock gating Round Robin referee generator(C-RAG) plan (4X4) is reenacted utilizing ISE Design Suite 14.2 programming. The produced judge is

reasonable, quick, and has a low and unsurprising most pessimistic scenario hold up time. The different squares of the plan, every one of which is being demonstrated in Verilog, i.e. intelligently checked, and orchestrated. In this plan case, the power advancement and further, extraordinary part of enhancement for the quantity of the rationale doors utilized for executing clock gating methods at RTL level is finished. All the power for the diverse part of improvement for the quantity of the rationale doors utilized for actualizing clock gating procedures at RTL level is organized for examination is finished utilizing Vivado Design suite 16.2 programming. Three diverse actualizing of time gating strategies at RTL level for Clock gating Round Robin referee generator(C-RAG) is done in Verilog, i.e. legitimately checked, and blended and in this way the forces are arranged for correlation utilizing Vivado. Present plan criteria wherein different parts of configuration utilizing check gating in Round Robin referee for organize on-chip (NOC) have been contemplated. This work predicts that Area and Power of existing plan can be additionally improved by Low Power Design Methodology. The proposed work does not give the impact of additional hardware on the region and execution data of the general system. Work should be done in these angles to see the impact on zone and in addition arrange throughput and delay.

### 6. REFERENCES

[1]. E. S. Shin, V. J. Mooney III, G. F. Riley, "Round-robin Arbiter Design and Generation," Georgia Institute of

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

Technology, Atlanta, GA, Technical Report GIT-CC-02-38, 2002, Available HTTP: http://www.cc.gatech.edu/tech\_reports

[2]. "Round-robin arbiter design and generation," in Proceedings of the International Symposium on System Synthesis, pp. 243–248, October 2002.

[3]. A paper on "Design and Analysis of Dynamically Configurable Bus Arbiters for SoCs" byS.HemaChitra, P.T.Vanathi.

[4]. "SYSTEM-ON-A-CHIP VERIFICATION-Methodology and Techniques" by PrakashRashinkar, Peter Paterson, Leena Singh, Kluwer Academic Publishers.

[5]. Alex A. Aravind, "An Arbitration algorithm for multiport memory systems", IEICE Electronic Express, Vol. No2, No.19, 488-494, Oct 2005.

[6]. Bu-chung Lin, Geeng-Wei Lee, Juninn Dar Huang and Jing-Yang Jou, "A Precise bandwidth Control Arbitration Algorithm for Hard RealTime SOC Buses", DAC 2007, pages 165-170.

[7]. KanishkaLahiri and AnandRaghunathan, "Lotterybus: A new high-performance communication architecture for System-on-chip Designs", DAC 2001, June 18-22, 2001, ACM, USA.

[8]. Massimo Conti, Marco Caldari, Giovanni B.Vece, Simone Orcioni, Claudio Turchetti,

[9]. "Performance Analysis of differentArbitration Algorithm of the AMBA AHBBus,"DesignAutomation

Conference,(DAC'04),2004, 41stVolume , Issue , 2004 Page(s): 618 - 621