A Peer Revieved Open Access International Journal

www.ijiemr.org

### **COPY RIGHT**

2018IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 28th Dec 2018. Link:

http://www.ijiemr.org/main/index.php?vol=Volume-07&issue=ISSUE-13

Title: LOW POWER IMPLEMENTATION OF MULTILEVEL FIFO STRUCTURAL DESIGNS IN NOC

Volume 07, Issue 13, Pages: 649-667.

**Paper Authors**

LINGAIAH JADA, EPPA SWETHA

ARJUN COLLEGE OF TECHNOLOGY & SCIENCE

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic

Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

# LOW POWER IMPLEMENTATION OF MULTILEVEL FIFO STRUCTURAL DESIGNS IN NOC

<sup>1</sup>LINGAIAH JADA, <sup>2</sup>EPPA SWETHA

<sup>1</sup>HOD & ASSOCIATE PROFESSOR, ARJUN COLLEGE OF TECHNOLOGY & SCIENCE <sup>2</sup>M.TECH(VLSI), ARJUN COLLEGE OF TECHNOLOGY & SCIENCE

#### **ARCHITECTURESABSTRACT:**

This short proposes an on-line direct test framework for revelation of inactive hard accuses which make in first information first yield backings of switches in the midst of field activity of NoC. The technique incorporates reiterating tests irregularly to thwart accumulation of inadequacies. A model use of the proposed test estimation has been consolidated into the switch channel interface and on-line test has been performed with fabricated self-equivalent data movement. The execution of the NoC after development of the test circuit has been investigated the extent that throughput while the locale overhead has been considered by coordinating the test hardware. Similarly, an on-line test system for the coordinating basis has been proposed which considers utilizing the header ricochets of the data movement advancement in transporting the test outlines.

#### 1. INTRODUCTION:

All through the latest decade, compose onchip (NoC) has ascended as a prevalent correspondence establishment differentiated transport and correspondence orchestrate complex chip plots vanquishing the inconveniences related to information exchange limit, hail respectability, and power dispersal [1]. In any case, like each and every other system on-a-chip (SoCs), NoC-based SoCs ought to similarly be striven for disfigurements. Testing the parts of the NoC structure incorporates testing switches and between switch joins critical proportion of zone of the NoC data transport medium controlled bv switches. which overwhelmingly required by FIFO bolsters and coordinating reason. In like way, the probabilities of run-time faults deformations occurring in backings and method of reasoning are through and

through higher differentiated and substitute fragments of the NoC. Thusly, test get ready for the NoC structure must begin with preliminary of supports and steering reason of the switches. Additionally, the test must be performed at times to ensure that no fault gets gathered. coincidental run-time down to earth issues have been one of the huge stresses in the midst of testing of significantly scaled CMOS-based memories. These inadequacies are a delayed consequence of physical effects, for instance, ecological defenselessness, developing, and low supply voltage and in this manner are unpredictable (nonpermanent indicating device mischief or glitch) in nature [2]. In any case, these spasmodic faults generally show a for the most part high occasion rate and over the long haul tend to twist up unmistakably immutable [2]. Also,

A Peer Revieved Open Access International Journal

www.ijiemr.org

annihilate of memories in like manner since imperfections wind unmistakably visit enough to be appointed constant. Along these lines, there is a prerequisite for online test strategy that can recognize the run-time weaknesses, which are unpredictable in nature yet a tiny bit at a time get the opportunity to be unmistakably unchanging after some time. Because of quick advancement in VLSI industry a large number of frameworks or highlights can be presented in an electronic gadget by creating a large number of transistors on a solitary silicon wafer or chip [9]. Presently a days chip makers are endeavoring to discharge the multi-center items with numerous more centers in the framework. This multi-center wave may prompt hundreds and even a large number of centers incorporated on a solitary chip. Notwithstanding the incorporation of many broadly useful centers on a solitary chip, expanding transistor checks will prompt more noteworthy framework combination for multiprocessor frameworks on-chip (MPSoCs). A framework on chip with expansive number of IP centers certainly needs a good, adaptable and high data transfer capacity correspondence framework. Transport framework and crossbar frameworks came into picture however they neglected to give an effective correspondence framework. So on chip organize appeared and replaces those two frameworks effortlessly. This on-chip organize has a few switches in fact called as switches and directing wires. For different processing spaces multi center engineering are exceptionally fundamental prerequisite. These models will build the levels of connecting capacity to the server The applications which throughput situated will require a high transfer correspondence. speed

Correspondence deferral or idleness can have a considerable job on the execution of multi-strung frameworks. Synchronization between strings will require correspondence having low overhead for adaptability reason. In MPSoCs, Utilization of an on-chip system can help empower separation: MPSoCs outline heterogeneous IΡ obstructs from an assortment of sellers; with standard interfaces, these squares can speak with the assistance of an on-chip organize in a fitting and-play design. The on-chip systems have some fundamental building squares i.e. topology, stream control component, exchanging systems, directing calculations and so forth. An effective directing calculation can upgrade the execution of an on-chip organize.

In this concise, we have proposed an online straightforward test strategy for first-input first-yield underpins (FIFO) coordinating basis present inside the switches of the NoC system. Our duties are according to the accompanying. A direct SOA-MATS++ test period count has proposed centering in-field never-ending deficiencies made in SRAM based FIFO memories and it has been utilized to perform on the web and irregular preliminary of FIFO memory show inside the switches of the NoC. Moreover, we have also proposed an online test technique for the coordinating method of reasoning that is played out at the same time with the preliminary of pads. The recommendation incorporates two strategies for utilizing the unused fragment of the header skips of the moving toward data distributes transporting the test outlines. In any case, deterministic test outlines for the coordinating method of reasoning delivered by Tetramax are set in the unused fields of the header shudder and are transported in the midst of the

A Peer Revieved Open Access International Journal

www.ijiemr.org

Second, conventional cycle. the pseudorandom outlines in the built data used in the midst movement conventional task and getting in contact at the directing basis are considered as test models. Accuse extension is assessed for both of the two proposals.

#### **Fault Model and its importance:**

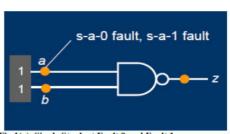

Single Stuck-at Faults Sign of a blame that results in mixed up circuit(system) yields or states Caused by deficiencies. A blame model is a planning model of something that could turn out severely in the improvement or task of a touch of equipment. only a solitary blame occur in a circuit. if we describe k possible blame sorts in our blame showcase the circuit has n signal lines, by single blame supposition, the total number of single shortcomings is k×n. A banner, or passage yield, is stuck at a 0 or 1 regard, self-ruling of the commitments to the circuit. Veritable flaws too much different and frequently not Three properties portray a single stuck to blame • Only one line is defective • The broken line is everlastingly set to 0 or 1 • The blame can be at a data or yield of a passage. Precedent: NAND entryway has 3 blame areas ( • ) and 6 single stuck-at

Fig.1(a). Single Stuck at Fault 0 and Fault 1

#### 2. RESEARCH WORK

#### 2.1 **BIST ARCHITECTURE FOR EXISITING MODEL:**

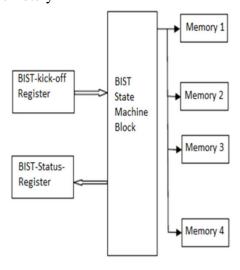

#### **BIST CONTROLLER DESIGN:**

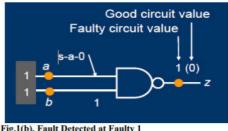

A procedure that empowers a machine to test itself is called worked in singular test (or BIST). It can make plans in light of a grouping of computations, each revolved around a particular kind of equipment or accuse create. Examination work has different exceptional utilization incorporating genuine comparators and also signal analyzers. In this assignment we will design Memory BIST (MBIST), which uses no less than one computations especially planned for testing memory issues. BIST structures create models and consider yield responses for a dedicated piece of equipment. You can complete BIST on entire designs, diagram squares or structures inside blueprint squares. Precedent age and what's more yield examination equipment can change dependent upon the diagram. Example age and in addition yield examination hardware can shift contingent upon the outline.

Fig. 1: Circuit with surrounding built-in self-test circuitry

MBIST hardware creates designs and distinguishes gadget disappointments. A fundamental MBIST square graph is appeared in Fig. 1.

### **BIST FAULT MODELS:**

A collecting blemish is a physical issue that occurs in the midst of the gathering methodology, causing device breakdowns or something like that. The explanation behind test age is to make a plan of test

fla ws.

A Peer Revieved Open Access International Journal

www.ijiemr.org

outlines that recognize whatever number collecting surrenders as could be permitted. The basic sorts of memory issues consolidate stuck-at. advancement. coupling and neighborhood outline delicate. In this endeavor we will design BIST for memory adhered to accuse show, which infers that a memory misses the mark if one of its control signs or memory cells remains stuck at a particular regard.

Stuck-at defects show this lead, where a banner or cell appears, apparently, to be appended to control (stuck-at-1) or ground (stuck-at-0). Contraption testing requires support, a framework to apply change to the device or circuit under test (CUT), and a couple of means to examinations or difference the device's responses and a conventional (non-broken) response. Built up testing uses outside test plans as lift and applies the models to the device by methods for an analyzer. The analyzer takes a gander at the contraption's response, differentiating it against the alluded to incredible response set away as a component of the test plan data. Fig. 1 exhibits how BIST puts each one of these limits inside the equipment enveloping the CUT. A state machine is used to create lift and examinations the response of the CUT.

#### **BIST** specifications.

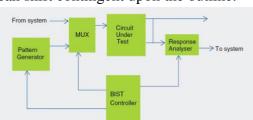

BIST is on a very basic level used to help in the testing of memory, which is a to an incredible degree complex plan (fabricate insightful), with the help of two or three pins. Frankly, while testing a memory using BIST, applying a clear clock movement close by a few pins helps test the entire memory IC. Presented here is a BIST setup using Verilog, which is reproduced using Model Sim programming. Here, we plan a memory appear, BIST controller and its test situate, which is used to drive the entire undertaking of BIST. In bist\_controller.v code, the constrained state machine is driven by methods for a data generator, an area generator and a control generator. Also, MUX is used to pick the action of BIST or standard memory assignments.

We diagram and separate BIST using the precedent generator, which will form and read-back same models in all memory regions.

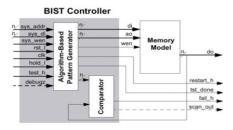

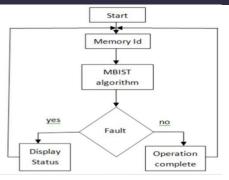

MBIST fundamental is showed up in Figure 2. This square graph contains memory BIST controller (BIST plan generator) and memory illustrate. The BIST controller has two yield shows the test accomplishment signals (tst\_done) and test pass/miss the mark hail (fail\_h). After test closes, tst\_done push toward getting to be '1'. Likewise, If the test made do with no error(pass) fail\_h is set '0', for the most part '1'(fail). With this MBIST controller govern, the memories can be attempted remotely

A Peer Revieved Open Access International Journal

www.ijiemr.org

The Memory BIST State machine holds up ST IDLE State until bist reset deactivate, sitting tight for bist start to tweaked in Bist\_Kickoff\_Register. At the point when bist\_ start is programm, the state machine skips to ST\_1\_ W0\_A state and starts making zeros from convey 0 to max address in climbing demand. It will be in this state tillit plays out the create action to the general memory. By then it bobs to the accompanying state ST\_2\_R0W1R1\_A and starts scrutinizing zeros, piece ones, and examining zeros undertaking at every area zone. Resulting to performing read it ponders against the typical characteristics if relationship confounds, it jumps ST\_STATUS state. While ricocheting to this state it similarly gives information like bist comp fail, bist fail address, bist\_fail\_mem\_id, bist\_fail\_err\_pos and the best possible state information (state info). If bist\_stop is programm at whatever point in the midst of the running of Memory BIST action. It bounces to ST\_STATUS State, proclaims bist done accompanying clock cycle, checks the bist\_fail\_counter and verifies bist\_pass or bist\_fail close by botch information in Bist\_Status\_Register. In ST\_STATUS, it bolts the information (like bist\_comp\_fail, address, err\_pos and mem\_id) it got from before state into Bist\_Status\_Register, and it also builds a bist\_fail\_counter in this state. In case bist\_halt\_on\_error altered the time when memory BIST was initiated by bist\_start, it sits tight in this state for bist\_resume or bist stop. If it gets a bist stop signal. It announces bist\_done on the accompanying clock and ricochets back to ST IDLE state and sit tight for bist\_start; If it gets a bist\_ proceed in this state it clears all the oversight information BIST\_STATUS\_REGISTER and jumps back to the state (state\_info) from where it arrived and starts performing Memory BIST undertaking from the accompanying area into the memory. In case bist\_halt\_on\_error isn't programm when memory BIST was started, while doing memory BIST errand. At whatever point it gets any failure, it jumps to ST\_STATUS state, snares all the mix-up information into Bist\_Status\_Register, builds bist\_fail\_counter and bounces back to the state from where it arrived (state info), paying little heed to whether it gets bist resume or not. Resulting to coming back to the earlier state. The state machine performing continues Memory Operation to the straggling leftovers of the memory and jumps to the accompanying state, if it recovers any slip-up in the to back states; it ricochets to ST\_STATUS state plays out a comparative assignment delineated previously. Exactly when the state machine has done each one of the undertakings in the last Memory BIST state (ST 8 R1 A), it jumps to ST\_STATUS State and verifies bist\_done to demonstrate fulfillment of Memory BIST Operation. Here in the state if bist\_fail\_counter is non-zero it announces bist\_fail and fitting last botch information in Bist\_Status\_Register close by bist\_done, to infer Memory BIST Operation failed. In case bist\_fail\_counter is zero by then, it bist\_pass and bist done Bist\_Status\_Register to suggest Successful

A Peer Revieved Open Access International Journal

www.ijiemr.org

of Memory BIST. Completion Memory BIST Operation is perform onto the memory whose id is changed in bist\_mem\_id in Bist\_Kickoff\_Register. While programming bist start. bist\_broadcast is programm, the state machine will trigger memory BIST for each memory in an enduring movement in a continuous way. Exactly when bist impart is programm, by then in the wake of completing of memory BIST for each memory (bist\_done), the status gets invigorated in Bist\_Status\_Register. In Non-impart mode, free of bist\_halt\_on\_ botch, bist\_fail\_counter implies the amount of bungles experienced in that fitting memory while performing Memory BIST. In any case, in convey mode. The primary sign we get is the best possible memory id's, Memory BIST Passed/failed, we won't any information on get no dissatisfactions (bist\_fail\_counter) occurred in the midst of memory BIST for each memory. Memory BIST Kick off must be achievable for any of the single memory inside the social affair of memory, or in convey mode, each one of the memories are decided for Memory BIST reliably. There is no decision of picking any widely appealing plan or any amidst number of memories for Memory BIST in the present **Implementation** of Memory Moreover, bist\_force\_error when program while initiating Memory BIST, it controls the state machine to implant botches while forming data into the memory. The consecutive read assignment will touch base into a bumble. This bit is used for negative testing of Memory BIST State machine. Each one of the indications of MBIST controller those are showed up in Figure 7 are elucidate in the Table

To test the framework memory square is arranged by forming a HDL code in

Verilog, the schematic showed up in Figure 8 is the amazing square of memory related remotely. In which wr en is a form engage banner to the memory to starts the composed work process in the memory, wr\_addr is a banner vector of 10 bits that can arrange up to 2<sup>10</sup> memory regions: Once the memory module is arranged it is emulated using diversion device [MODELSIM] to make the waveform that shows in results. After concentrated proliferation, the memory module arranged using mix gadget [Xilinx ISE] which creates the blend report.

MBSIT controller reenactment is finished by mentor outlines gadget ModelSimsimulator. Figure 9 is the waveform reenactment of module mbist\_top. The kick\_off enroll is used as an information select under read/make mode. bist start signal is used to begin memory BIST controller. bist\_resume is used to proceed with MBIST Controller, if miss the mark occurs. In addition, bist\_stop is used to stop memory BIST action. The bist\_status select is used to store the outcome of the test, where bist\_pass indicate MBIST test pass, bist\_fail show MBIST test crash and burn. bist done demonstrate fulfillment of the test. In this diversion making/examining in various zone of memory is showed up in Figure 6. Four memory prevents with same data significance are attempted by MBIST controller and test is serial. After the bist\_done is set '1' test closes with crash and burn/pass status, in the status select.

# 3. ROUTER'S FIFO ARCHITECTURE DESIGN AND TEST CRITERIA IN NOC:

### 3.1INTRODUCTION TO FIFO:

Multiprocessor frameworks on-chips (MPSoCs) have risen in the previous decade as an imperative class of huge scale

A Peer Revieved Open Access International Journal

www.ijiemr.org

(VLSI) frameworks. coordination MPSoC is a framework on-chip a VLSI framework that fuses most or every one of the segments essential for an application that uses different programmable framework processors as segments. MPSoCs are broadly utilized in systems administration, correspondences, handling, and interactive media among different applications .A pattern multiprocessor framework on-chip (MPSoC) plan being interconnected with on-chip systems is as of now developing for utilizations of parallel preparing, logical figuring, et cetera. System on chip Network on chip or system on a chip (NoC or NOC) is a correspondence subsystem on an incorporated circuit, ordinarily between licensed innovation (IP) centers in a framework on a chip (SoC). NoCs can traverse synchronous and offbeat clock spaces or utilize unclocked nonconcurrent rationale. **NoC** innovation applies organizing hypothesis and techniques to onchip correspondence and brings eminent changes over traditional transport and crossbar interconnections. NoC enhances the versatility of SoCs, and the power proficiency of complex SoCs contrasted with different outlines. Steering on NoC Routing on NoC is very like directing on any system. A steering calculation decides how the information is directed from sender to recipient. Directing calculations separated into two gatherings, are neglectful versatile calculations. and Negligent calculations are additionally isolated into two subgroups: deterministic calculations. stochastic calculations course bundles with no data about activity sums and states of the system, deterministic calculations course parcels dependably along a same course

and stochastic steering depends on arbitrariness.

## 3.2 ROUTERS ALGORIHMS MODELLING IN NOC:

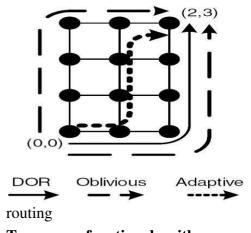

First we have to decide the topology for the on-chip system and after that a particular directing calculation ought to be picked. A steering calculation decides the whole way for the message or information parcels to achieve the goal. Principle errand of a steering calculation is to convey the movement from various hubs uniformly all through the system. Like that it will maintain a strategic distance from hotspots and enhance the system inertness and throughput esteem by limiting dispute. A specific steering calculation influences the switch plan unpredictability, territory and subsequently influences the utilization in entire system to accomplish execution necessities. There different order of steering calculation. The point by point characterization is portrayed in part 3. For the most part steering calculations are grouped into three sorts. Those are I) Deterministic directing ii) Oblivious Routing iii) Adaptive steering. proposed different directing Analysts calculations. Be that as it may, there is a Dimension arrange directing (DOR) which is exceptionally easy to execute. So it is best for the systems. DOR is a case of deterministic steering. XY directing goes under this DOR which is depicted in section 4. Deterministic directing is a subset of unaware steering. In deterministic steering one way is computed among source and goal and directing in that way is done all through the procedure. In absent steering is done in various ways however it doesn't make a big deal about the blockage in organize. In versatile directing in excess of one way is computed among source and

A Peer Revieved Open Access International Journal

www.ijiemr.org

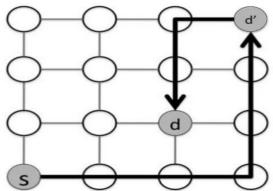

goal yet just way is chosen by the blockage in the system. There is another arrangement of directing calculations i.e. Negligible and Non-insignificant directing. In negligible directing a way having most modest number of jumps is chosen. Noninsignificant directing is the exact inverse. Without organize clog non-insignificant directing will expand the dormancy esteem. Be that as it may, with blockage it's execution is adequate. An insignificant directing which can maintain a strategic distance from congested connections will give agreeable outcome by diminishing the system inertness. In directing a case of DOR, unmindful and versatile steering is appeared. Every one of the hubs are distinguished by (x,y) organizes. Here (0,0)is picked as the source and (2,3) is picked as the goal. In DOR steering is done in that one way all through the system. In clear steering two ways are figured for directing. In versatile steering calculation directing is finished with that way maintaining a strategic distance from congested connections.

Example of DOR, Oblivious and Adaptive

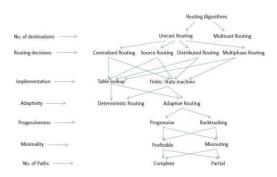

### Taxonomy of routing algorithms

Routing in NOC decides the way that every bundle takes after among source and goal match. There are a few properties of steering calculations which are basically required for interconnection systems i.e. network, adaptivity, gridlock and livelock opportunity, adaptation to non-critical failure [14]. Network is the capacity to course parcels from any source hub to any goal hub. Adaptivity is the capacity to course parcels through elective ways within the sight of conflict or broken segments. Gridlock opportunity is the capacity to ensure that bundles won't square or meander over the system for eternity. Adaptation to internal failure is the capacity to course parcels within the sight of flawed parts. There are numerous approaches to characterize directing in onchip-systems. As indicated by number of goals directing calculations are grouped into two kinds i.e. unicast and multicast directing [15]. If there should arise an occurrence of unicast directing voyaging bundles have just a single goal, however if there should be an occurrence of multicast steering, the parcels have in excess of one goal. Between the two accessible unicast steering directing strategies are considered as a decent strategy for Network on Chip as it has point-to-point correspondence joins among different hubs on a framework on chip. As per steering evaluation capacity unicast directing has four orders. They are source steering, circulated directing, and brought together steering and multiphase directing. As indicated by source directing, steering way is controlled by some directing choices when information is produced by the hub and put away in the parcel header. Yet, as indicated by conveyed directing, steering way is chosen as the bundles or flutters stream in the system. Multiphase directing is shaped by joining the source and goal steering plan. In brought together information steering, stream framework is controlled by a unified

A Peer Revieved Open Access International Journal

www.ijiemr.org

controller. In execution perspective steering calculations are of two sorts i.e. query table based and FSM based. As indicated by Lookup table directing calculations a query table is available in every switch and they are executed in programming level. Consequently they are prominent. The sections of the query table is continued refreshing by the directing calculation If these passages will transform change the entire calculation. Limited State Machine based steering calculations can be actualized in both ways i.e. programming equipment. In adaptivity perspective steering calculations are likewise ordered into two classes. In deterministic steering one way is figured among source and goal and through that way just directing is done inside a system. In versatile directing calculations various ways are computed among source and goal yet steering is done in one chose way which is less congested. Drawbacks of this compose calculation is its execution many-sided quality, cost and more power utilization. So we need to consider the privilege QoS measurements before usage of this. There are another sort of directing calculation i.e. backtracking directing calculation which is adaptation to internal failure in nature. Another calculation exists i.e. dynamic steering where a divert is held for possible later use for bounces to be pushed ahead. Some

steering calculations send parcels or flutters just toward that path which is closer to the goal and these directing calculations are known as gainful calculations. misrouting calculation may forward a parcel or dance far from the goal also and can cause bundle misfortune. As per the quantity of accessible steering ways, directing calculations can likewise be ordered i.e. finish and halfway directing calculations. Different application particular steering calculations have been proposed for the NOC [3]. Numerous scientists recommended static directing calculations and performed correspondence investigation in view of the static conduct of NOC forms, in this way, deciding the static steering for NOC. Siebenborn et al. also. Hu et al. [16] utilized Communication Dependency Graph to assess between process correspondences.

# 3.3Classification of routing algorithm base donadaptively Deterministic Dimension-Ordered Routing

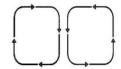

A directing calculation can be depicted by which turns are allowed. Figure 3.2 shows every single conceivable turn in a 2D work arrange while Figure 3.3 represents the more restricted arrangement of reasonable turns permitted by DOR X-Y directing. Permitting all turns result in cyclic asset conditions, which can prompt system halt. To keep these cyclic conditions, turns might be denied. As should be obvious, no cycle is available in Figure 3.3. In particular, a message voyaging east or west is permitted to turn north or south; notwithstanding, messages voyaging north and south are allowed no turns. Two of the four turns won't be allowed, so a cycle isn't conceivable. Then again, Y-X steering can be utilized where messages voyaging north or south are permitted to turn east or west

A Peer Revieved Open Access International Journal

www.ijiemr.org

yet once a message is voyaging East or West, no further turns are allowed. Contingent upon the system measurements, i.e. regardless of whether there are more hubs along X or Y, one of these directing calculations will offset stack better with uniform irregular movement since channel stack is higher along the measurement with less hubs. Measurement arrange directing is both straightforward and halt free; be that as it may, it takes out way assorted variety in a work system and consequently brings down throughput. With measurement arrange steering, precisely one way exists between each source and goal combine. Way assorted variety, the directing calculation can't course around flaws in the system or stay away from territories of clog. Because of directing limitations, measurement arrange steering completes a poor employment of load adjusting the system [17].

Figure 3.2 Allpossibleturns

#### **Oblivious Routing**

Utilizing a neglectful steering calculation [18], directing ways are picked without respect to the condition of the system. By not utilizing data about the condition of the system, these steering calculations can be kept basic. Valiant's randomized steering calculation is one case of an unaware directing calculation. To highway a parcel from source s to goal d utilizing Valiant's calculation, a middle of the road goal d' is arbitrarily chosen. The bundle is first steered from s to d' and afterward from d' to d. By directing first to an arbitrarily chose transitional goal before steering to the last goal, Valiant's calculation can

balance activity over the system; the randomization causes any movement example to seem, by all accounts, to be uniform arbitrary. Load offsetting with Valiant's calculation comes to the detriment of area; for instance, by directing to a halfway goal, the region of close neighbor activity on a work is annihilated. Bounce check is expanded, which thus builds the normal bundle idleness and the normal vitality devoured by the parcel in the system. Valiant's directing calculation can be limited to help just insignificant courses [158], by confining steering decisions to just the most brief ways with a specific end goal to protect area. In a k-ary n-solid shape topology, the halfway hub 'd' must exist in the negligible quadrant; the littlest n-dimensional sub-connect with s and d as corner hubs jumping this quadrant. With both Valiant's randomized steering and insignificant versatile measurement arrange directing can be utilized to course from s to d' and from d' to d. On the off chance that DOR is utilized, not all ways will be misused but rather preferred load adjusting 3 ix-accomplished deterministic steering specifically to d. Figure 3.4 and Figure 3.5 shows a steering way chosen utilizing Valiant's calculation and negligible negligent directing. In Figure 3.4, Valiant's calculation arbitrarily chooses a middle of the road goal d'. The arbitrary choice can crush area and essentially increment jump tally; here, the bounce check is expanded from three bounces to nine bounces. To safeguard negligible unmindful area, steering can be utilized as in Figure 3.5. Presently, d' must be chosen to exist in the insignificant quadrant shaped by s and d, protecting the base jump tally of three. One conceivable determination is featured (two different ways are workable for this source-

A Peer Revieved Open Access International Journal

www.ijiemr.org

goal combine as appeared with dashed lines). Valiant's steering calculation and insignificant unmindful directing are without halt when utilized related to X-Y directing. A case of an unaware directing calculation that isn't sans halt is one that arbitrarily picks between X-Y or Y-X courses. The absent calculation that haphazardly picks between X-Y or Y-X courses isn't sans halt since every one of the four abandons Figure

4.2 are conceivable prompting potential cycles in the connection obtaining diagram.

Figure 3.4 Valiant's routing algorithm

#### **Adaptive Routing**

A more modern steering calculation can be versatile, i.e. the way a message takes from A to B relies upon the system movement circumstance. For example, a message can be coming the X-Y course, see blockage at (1,0's) east cordial connection and rather take the north friendly connection towards the goal. Neighborhood or worldwide data can be utilized to settle on versatile directing choices [19]. Versatile directing calculations regularly depend on nearby switch data, for example, line inhabitance and lining postponement to measure clog and select connections. The backpressure instruments utilized by stream control (talked about in the following part) enable blockage data to proliferate from the clog site back through the system. Figure 3.6 demonstrates all conceivable (negligible) courses that a message can take from Node (0,0) to Node (2,3). There are nine conceivable ways. A versatile steering calculation that use just insignificant ways could misuse a substantial level of way decent variety to give stack adjusting and adaptation to internal failure. Versatile steering can be limited to taking negligible courses between the source and the goal. An elective alternative is to utilize misrouting, which enables a bundle to be steered in a misrouting non-gainful heading bringing about non-insignificant ways. When misrouting is allowed, livelock turns into a worry. Without components to ensure forward advancement, livelock can happen as a livelock parcel is persistently misrouted in order to never achieve its goal. We can battle this issue by permitting a most extreme number of misroutes per bundle and giving higher need to parcels have been misrouted countless. Misrouting builds the bounce check yet Figure 3.5 Minimal oblivious routing may lessen end-to-end parcel idleness by dodging blockage (lining delay). With a completely versatile steering calculation, stop can turn into an issue. For instance, the versatile course appeared in Figure 3.6 is a superset of unaware directing and is liable to potential gridlock. Planar-versatile directing limits the assets expected to deal with halt by confining adaptivity to just two measurements at once. Duato has proposed stream control systems that permit full directing adaptivity while guaranteeing opportunity from halt. Halt free stream control will be talked about in Chapter 5. Another test with versatile steering is safeguarding between message requesting as might be required by the soundness convention. In the event that messages must land at the goal in a similar request that the source issued them, versatile directing can be hazardous.

A Peer Revieved Open Access International Journal

www.ijiemr.org

Systems to re-arrange messages at the goal can be utilized or messages of a given class can be limited in their steering to avert rerequesting.

Figure 3.6 Adaptive routing example

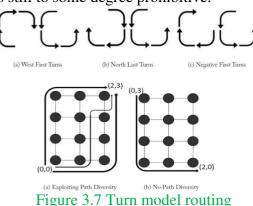

### **Adaptive Turn Model Routing**

While we presented turn display steering before section, talking about how measurement arrange X-Y directing dispenses with two out of four turns (Figure 3.3), here, we clarify how turn model can be more turn demonstrate directing comprehensively connected to infer versatile stop free directing calculations. Versatile turn demonstrate steering dispenses with the base arrangement of swings expected accomplish stop opportunity while holding some way decent variety and potential for adaptivity. With measurement arrange directing just four conceivable turns are allowed of the eight turns accessible in a two dimensional work. Turn display directing builds the adaptability of the calculation by permitting six out of eight turns. Just a single abandon each cycle is dispensed with. In Figure 3.7, three conceivable directing calculations delineated. Beginning with every single conceivable turn (appeared in Figure 3.2), the north to west turn is dispensed with; after this end is made, the three steering calculations appeared in Figure 3.7 can be inferred. In Figure 3.7a, the west-first calculation is appeared; notwithstanding dispensing with the North to West turn, the South to West turn is wiped out. At the end of the day, a message should initially go in the West course before going some other way. The North-Last calculation (Figure 3.7b) dispenses with both the North to West and the North to East turns. Once a message has turned North, no further turns are allowed; subsequently, the North turn must be made last. At long last, Figure 3.7c expels abandons North to West and East to South make the Negative-First calculation. A message goes in the negative headings (west and south) first before it is allowed to movement in positive ways (east and north). Every one of the three of these turn show directing calculations are stop. Figure 3.9 represents a conceivable turn end that is invalid; the disposal of North to West joined with the end of West to North can prompt halt. A stop cycle is portrayed in Figure 3.9 that can result from an arrangement of messages utilizing the turns indicated in 3.9 Illegal turn demonstrate directing and coming about gridlock cycle. Odd-even turn demonstrate proposes wiping out an arrangement of two turns relying upon whether the present hub is in an odd or even section. For instance, when a bundle is crossing a hub in an even column1, abandons East to North and from North to West are restricted. For bundles crossing an odd segment hub, abandons East to South and from South to West are restricted. With this arrangement of confinements, the odd-even turn display is without stop gave 180° turns are prohibited. The odd-even turn display gives preferred adaptivity over other turn demonstrate calculations, for example, West-First. With West-First, goals toward the West of the source, have no adaptability; with odd-

A Peer Revieved Open Access International Journal

www.ijiemr.org

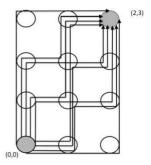

notwithstanding steering, there adaptability relying upon the reasonable turns for a given segment. In Figure 3.8 Negative initially steering precedent, we apply the Negative-First turn display directing to two diverse source goal sets. In Figure 3.8a, three conceivable courses are appeared somewhere in the range of (0,0)and (2,3) (more are conceivable); abandons North to East and from East to North are allowed taking into consideration critical adaptability. Nonetheless, in Figure 3.8b, there is just a single way permitted by the calculation to course from (0,3) to (2,0). The directing calculation does not enable the message to abandon East to South. Negative courses must be finished first, bringing about no way decent variety for this source-goal match. As shown by this precedent, turn demonstrate steering give more adaptability and adaptivity than measurement arrange directing however it is still to some degree prohibitive.

Figure 3.8 Negative first routing example

Figure 3.9 Illegal turn model routing and resulting deadlock cycle

### **Problems inrouting**

There are various types of issues emerge amid the steering procedure. Particularly in unaware directing this sort of issue emerges which results in blockage of activity. So steering gadgets needs to sit tight for the decrease of movement and afterward have a go at sending over and again. Gridlock, livelock and starvation are potential issues on both absent and versatile directing. These issues are talked about as follows in the following subsection.

#### **Deadlock**

At the point when the information parcels are moving around the system, they ordinarily hold some asset in the middle of the way. At the point when every one of the parcels are sitting tight for one another to discharge the assets in a cyclic way then this sort of circumstance is called as gridlock. Thus the all bundles will be hindered inside the halt condition and they can't be directed to their goal and that is a gigantic misfortune in the on chip systems.

#### Livelock

This sort of issue happens when the parcels are moving around a goal without coming to there. So information can't be directed to the goal. This kind issue will occur in non-negligible directing calculation where the steering calculation pick the longest way whether the most limited way exist or not by watching the system clog. For throughput change this sort of issue ought to be stayed away from.

#### Starvation

This sort of issue is fundamentally the same as the genuine circumstances. Diverse need task to the information parcels in NoC can cause this sort of issue. So high need bundles can achieve their goal effectively however the low need components will

A Peer Revieved Open Access International Journal

www.ijiemr.org

never achieve their goal. This sort of circumstance emerges in light of the fact that the high need bundles hold the assets and the low need parcels get starved for the assets. This sort of issue can be maintained a strategic distance from by utilizing a suitable directing calculation which has some transmission capacity booking for the low need packets.

Performanceparametersforroutingalgorithm

Performance requirements that every NoC

must satisfy

- Small inertness

- Guaranteed throughput

# 3.4 PROPOSED ARCHITECTURE FIFO ROUTER:

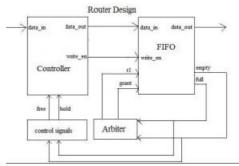

The above present square structure portrays us the switch demonstrating in view of the controlling angles which uses control flag and mediator where these module would be considered to underline the outline viewpoints to enhance the power and zone capabilities. Here, we could watch the data\_in and data\_out motion from the DUT where the signs are the being used from the controller and will be exchanged to next phase of FIFO cradles where controlling signs would create a specific period of information to be prepared by the referee and the individual information would be put away in FIFO in light of the read and compose cycles. Before read and composing the information in FIFO the underlying check for FULL and EMPTY is watched and confirmed in like manner.

- Path decent variety

- Sufficient exchange limit

- Low control utilization

- Fault and diversion resistance

- Architectural necessities of adaptability and programmability

Be that as it may, there are three critical parameters for NoC which we are thinking about in this proposition i.e. System Latency, Network Throughput and Total Network Power, Packet drop.

## DESIGNED CIRCUIT DIAGRAM FOR FIFO ROUTER:

Consider the above model for the proposed engineering for the FIFO BUFFER control configuration in light of the Router control calculation where every datum frame the FIFO control is controlled by the legitimate bundle condition. For each port the condition check for bundle substantial is confirmed and concurring each port FIFO is worked. For four port of FIFO we have set up control channel which would assess which port have been chosen and which port would get the information from the plan. Estimation of the information stream from input area to yield segment is checked and seen in reenactment results as needs be.

A Peer Revieved Open Access International Journal

www.ijiemr.org

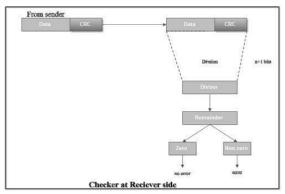

# **DESIGN TEST CONSIDERATIONS:** CRC Check and Test Criteria:

Cyclic Redundancy Check (CRC): A mistake identification component in which an exceptional number is added to a square of information keeping in mind the end goal to distinguish any progressions presented amid capacity (or transmission). The CRC is recalculated on recovery (or gathering) and contrasted with the esteem initially transmitted, which can uncover certain sorts of mistake. For instance, a solitary defiled piece in the information results in a one-piece change in the computed CRC, however various degenerate bits may counterbalance one another.

A CRC is inferred utilizing a more intricate the straightforward calculation than CHECKSUM, including **MODULO** ARITHMETIC (henceforth the 'cyclic' name) and regarding each info word as an arrangement coefficients of for a polynomial.

- CRC is more ground-breaking than VRC and LRC in distinguishing blunders.

- It did not depend on twofold expansion like VRC and LRC. Or maybe it depends on parallel division.

- At the sender side, the information unit to be transmitted IS isolated by a foreordained divisor (parallel number) keeping in mind the end goal to acquire the rest of. This leftover portion is called CRC.

- The CRC has one piece not as much as the divisor. It implies that if CRC is of n bits, divisor is of n+ 1 bit.

- The sender adds this CRC to the finish of information unit with the end goal that the subsequent information unit turns out to be precisely separable by foreordained divisor i.e. leftover portion winds up zero.

- At the goal, the approaching information unit i.e. information + CRC is isolated by a

- similar number (foreordained parallel divisor).

- If the rest of division is zero at that point there is no blunder in the information unit and beneficiary acknowledges it.

- If leftover portion after division isn't zero, it shows that the information unit has been harmed in travel and subsequently it is rejected.

- This procedure is more great than the equality check and checksum mistake recognition.

- CRC depends on twofold division. A succession of repetitive bits called CRC or CRC leftover portion is added toward the finish of an information unit, for example, byte.

### **Requirements of CRC:**

A CRC will be substantial if and just on the off chance that it fulfills the accompanying prerequisites:

- 1. It ought to have precisely one less piece than divisor.

- 2. Affixing the CRC to the finish of the information unit should result in the bit arrangement which is precisely separable by the divisor.

# • The different advances followed in the CRC technique are

- 1. A string of n as is attached to the information unit. The length of foreordained divisor is n+ 1.

- 2. The recently shaped information unit i.e. unique information + string of n as are partitioned by the divisor utilizing double division and leftover portion is gotten. This leftover portion is called CRC.

A Peer Revieved Open Access International Journal

www.ijiemr.org

- 3. Presently, string of n Os annexed to information unit is supplanted by the CRC leftover portion (which is additionally of n bit).

- 4. The information unit + CRC is then transmitted to recipient.

- 5. The collector on getting it isolates information unit + CRC by a similar divisor and checks the rest of.

- 6. In the event that the rest of division is zero, recipient expect that there is no mistake in information and it acknowledges it.

- 7. In the event that leftover portion is non-zero at that point there is a blunder in information and beneficiary rejects it.

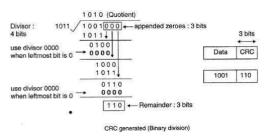

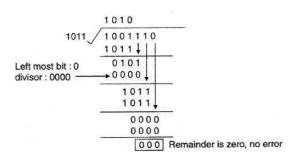

- For instance, if information to be transmitted is 1001 and foreordained divisor is 1011. The method given underneath is utilized:

- 1. String of 3 zeroes is affixed to 1011 as divisor is of 4 bits. Presently recently framed information is 1011000.

1. Information unit 1011000 is separated by 1011.

2. Amid this procedure of division, at whatever point the furthest left piece of

- profit or leftover portion is 0, we utilize a series of Os of same length as divisor. Accordingly for this situation divisor 1011 is supplanted by 0000.

- 3. At the collector side, information got is 1001110.

- 4. This information is again isolated by a divisor 1011.

- 5. The rest of is 000; it implies there is no mistake.

CRC decoded (binary division)

- CRC can identify all the burst mistakes that influence an odd number of bits.

- The likelihood of blunder identification and the kinds of noticeable mistakes relies upon the decision of divisor.

- Thus two noteworthy necessity of CRC

- (a) CRC ought to have precisely one piece not as much as divisor.

- (b) Appending the CRC to the finish of the information unit should result in the bit arrangement which is precisely distinct by the divisor.

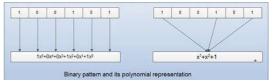

#### Polynomial codes

- An example of Os and 1s can be spoken to as a polynomial with coefficient of o and 1.

- Here, the intensity of each term demonstrates the situation of the bit and the coefficient demonstrates the estimations of the bit.

- For instance, if paired example is 100101, its relating polynomial portrayal is x5 + x2

- + 1. Figure demonstrates the polynomial

A Peer Revieved Open Access International Journal

www.ijiemr.org

where every one of the terms with zero coefficient are expelled and x J is supplanted by x and XO by 1.

- The advantages of utilizing polynomial codes is that it creates short codes. For instance here a 6-bit design is supplanted by 3 terms.

- In polynomial codes, the degree is 1 not as much as the quantity of bits in the paired example. The level of polynomial is the most astounding force in polynomial. For instance as appeared in fig level of polynomial x5 + x2 + 1 are 5. The bit design for this situation is 6.

- Addition of two polynomials depends on modulo-2 technique. In, for example, case, expansion and subtraction is same.

- Addition or subtraction is finished by joining terms and erasing sets of indistinguishable terms. For instance including x5 + x4 + x2 and x6 + x4 + x2 give x6 + x5. The terms x4 and x2 are erased.

- If three polynomials are to be included and on the off chance that we get a same term three times, a couple of them is identified and the third term is kept. For instance, if there is x2 three times then we keep just a single x2

- in the event of duplication of two polynomials, their forces are included. For instance, duplicating x5 + x3 + x2 + x with x2+x+1 yields:

$$(X5 + x3 + x2 + x) (x2 + x + 1)$$

= x7 + x6 + x5 + x4 + x3 + x4 + x3 + x2 + x3 + x2 + x

=X7+x6+x3+X

In this, first polynomial is increased by all terms of second. The outcome is then disentangled and combines of equivalent terms are erased.

• Incase of division, the two polynomials are isolated according to the guidelines of parallel division, until the point that the level of profit is not as much as that of divisor.

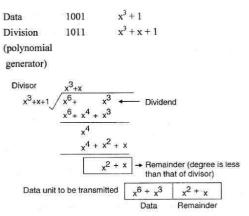

### **CRC** generator using polynomials

• If we consider the information unit 1001 and divisor or polynomial generator 1011their polynomial portrayal is:

CRC division using polynomial

- Now string of n 0s (one not as much as that of divisor) is affixed to information. Presently information is 1001000 and its relating polynomial portrayal is x6 + x3.

- The division of x6+x3 by x3+x+1 is appeared in fig.

- The polynomial generator ought to have following properties:

- 1. It ought to have no less than two terms.

- 2. The coefficient of the term x0 ought to be 1.

- 3. It ought not be distinct by x.

- 4. It ought to be distinguishable by x+1.

#### 4. RESULTS

#### **SYNTHESIS RESULTS:**

#### AREA UTILIZATION

| Resource | Utilization | Available | Utilization % |

|----------|-------------|-----------|---------------|

| LUT      | 115         | 133800    | 0.09          |

| FF       | 55          | 267600    | 0.02          |

| IO       | 61          | 500       | 12.20         |

| BUFG     | 1           | 32        | 3,12          |

A Peer Revieved Open Access International Journal

www.ijiemr.org

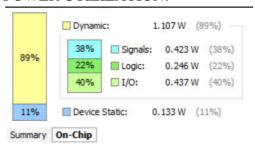

#### POWER UTILIZATION:

#### AREA AND POWER DISCUSSIONS:

- From our outline perspective we have assessed and ascertained the correct fan out and fan in light of the reenactment results and union outcomes.

- 2. For each such fan out we have a tendency to streamline the region of 15 % which saw on just info and yield conditions.

- 3. The outlined parameter, for example, inactivity is seen from the union outcomes which can be watched and arranged in result table.

### 5. CONCLUSIONS:

We have displayed a versatile switch configuration utilizing cushion resizing system for Network-on-chip (NOC). Buffer resizing strategy with a coasting FIFO is executed in the switch configuration to decrease the blockage of information bundles which has beneficial outcome on the speed. The fundamental components of switch, for example, FIFO, FSM controller and judge are outlined and reenacted utilizing verilog HDL on Xilinx Isim test system instrument. With cradle resizing

method it is seen that, when static FIFO is full, skimming FIFO is relegated to that specific port and the information is accessible at each clock cycle. Henceforth information clog is lessened by utilizing the proposed cradle resizing method. The outline is confirmed by building up a confirmation domain in framework verilog MODEL-SIM test system device.

#### **FUTURE SCOPE**

The above ends are simply fit for a 2-Dimension a 3x3 and 4x4 work topology NoC. These directing calculations are just relevant to general systems. We have to contemplate distinctive steering calculations for sporadic topologies. We have to examine other directing calculations which can likewise give better outcomes for various parameter variety.

#### 6. REFERENCES:

- [1] P. Gartz, "Regional Congestion Awareness for Load Balance in Networkson-Chip," in 14th

- International Symposium on High-Performance Computer Architecture, Austin, 2006.

- [2] G. Ascia, "Neighbors-on-Path: A New Selection Strategy for On-Chip Networks," in IEEE ESTIMedia, Hong Kong, 2006.

- [3] M. Palesi, "Application Specific Routing Algorithms for Network on Chip," in IEEE TRANSACTIONS ON PARALLEL AND DISTRIBUTED SYSTEMS, March 2009.

- [4] A. Mejia, "Region based Routing: A Mchanism to Support Efficient Routing Algorithms in NoCs," in IEEE TRANSACTIONS ON VLSI SYSTEMS, 2009.

- [5] M. Palesi, "Bandwidth-aware routing algorithms for networks-on-chip platforms," in IET Computers & Digital

A Peer Revieved Open Access International Journal

www.ijiemr.org

Techniques, 2009, Vol. 3, Iss. 5, pp. 413–429 413.

- [6] S. Rodrigo, "Efficient implementation of distributed routing algorithms for NoCs," in IET Computers & Digital Techniques, 2008.

- [7] R. Manevich, "Centralized Adaptive Routing for NoCs," in IEEE COMPUTER ARCHITECTURE LETTERS, 2010.

- [8] Jose' Flich, "A Survey and Evaluation of Topology-Agnostic Deterministic Routing Algorithms," in IEEE TRANSACTIONS ON PARALLEL AND DISTRIBUTED SYSTEMS, Chicago, March 2012.

- [9] W. J. Dally, "Route packets; not wire," in DAC 2001, Las vegas, 2001.

- [10] S. P. a. N. Dutt, "Network on Chip," in On-Chip Communication Architectures, Morgan Kaufmann, 2010, p. 439.

- [11] J. K. Singh ,A.K. Swain "Performance evaluation of different routing algorithms in Network on Chip," in PrimeAsia 2013, Vishakhpatnma, 2013.

- [12] T. L. Ville Rantala, "Network on Chip Routing Algorithms," citeseerx, 2006.

- [13] M. A. Yogita A. Sadawarte, "Comparative Study of Switching Techniques for Network-on- Chip Architecture," in ICCCS'11, Rourkela, 2011.

- [14] Z. Lu, "Using Wormhole Switching for Networks on Chip: Feasibility Analysis and Microarchitecture Adaptation," Royal Institute of Technology, Sweden, 2005.