A Peer Revieved Open Access International Journal

www.ijiemr.org

# **COPY RIGHT**

2018IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 19th Dec 2018. Link:

http://www.ijiemr.org/main/index.php?vol=Volume-07&issue=ISSUE-13

Title: DESIGN AND IMPLEMENTATION OF ASYNCHRONOUS MODELING FOR TRANSRECEIVER IN UNIVERSAL COMMUNICATION

Volume 07, Issue 13, Pages: 594-603.

**Paper Authors**

P.ANUSHA, A.MANASA

Ashoka Institute of Engineering and Technology

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic

Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

# DESIGN AND IMPLEMENTATION OF ASYNCHRONOUS MODELING FOR TRANSRECEIVER IN UNIVERSAL COMMUNICATION

<sup>1</sup>P.ANUSHA, <sup>2</sup>A.MANASA

<sup>1</sup>M.Tech Scholar, VLSI System Design (ECE), Ashoka Institute of Engineering & Technology <sup>2</sup>Assistant Professor, Department of ECE, Ashoka Institute of Engineering & Technology <sup>1</sup>pendemanusha01@gmail.com<sup>2</sup>apurimanasa@gmail.com

#### **ABSTRACT**

Universal Asynchronous Receiver Transmitter (UART) is a serial correspondence interface. The plan of UART for FPGA based frameworks utilizing Verilog. The UART configuration has programmable highlights for Transmission, Reception and Baud Rate generation. It has FIFO stockpiling, programmable serial interface qualities, complete status detailing abilities and mistake discovery. We present the outline of 9-bit UART modules in view of Verilog HDL. This design highlights programmed address distinguishing proof in the character itself. In this executed the VLSI plan of the module and pass information between the proposed 9-bit UART module with a host CPU. The plan comprises of recipient module, transmitter module, prescaler module and nonconcurrent FIFOs. The plan is executed utilizing Hardware Description Language Verilog. The plan is reproduced and checked on Xilinx ISE. centers around the outline of a UART chip with installed BIST engineering utilizing basic LFSR with the assistance of VHDL dialect. The paper depicts the issues of (VLSI) testing taken after by the conduct of UART that incorporates both transmitter and beneficiary segment utilizing VHISC Hardware Description Language (VHDL). In this paper, the reenactment result is contrasted and past work and it has been seen that the outcome is promising and decreases timing requirements and generally speaking force dissemination. The UART is focused at broadband modem, base station, PDA, and PDA outlines.

#### 1. INTRODUCTION

#### **Transreciever for Data Communications**

The UART comprises of three principle parts to be specific receiver, transmitter, and baud rate generator which is only the frequency divider. The universal asynchronous receiver/transmitter is abbreviated as UART. "Asynchronous" shows that UART recuperate character timing data from the information stream, utilizing assigned "begin" and "stop" bits to

demonstrate the confining of each character. The historical backdrop of the principal UART - like gadgets was pivoting mechanical commutates, these sent 5-bit codes for mechanical teletypewriters, their after supplanted more code 8 bit, 10 bit FIFO and so forth. The UART is utilized in the middle of the moderate and the quick fringe gadgets for instance: PC and engine

A Peer Revieved Open Access International Journal

www.ijiemr.org

drives or peripherals or in the middle of the controller and LCD projectors, because of this reason, UART is utilized for the most part for the short separation, low speed and is of minimal effort. The UART utilizes the Verilog portrayal dialect to receive the core elements of UART and acclimatize them into a FPGA chip. It has three primary segments i.e. transmitter, receiver, and the BRG (baud rate generator). Here we are utilizing the state machines for transmitter and collector because of this our proposed UART turns out to be more steady, solid, smaller and less mind boggling for serial information correspondence. Because of which, the utilization of LUTs, cut flip lemon or in short the zone utilization of the chip turns out to be less. We have additionally tried our outline for the mistakes which emerges amid transmission of information to investigate that our yield of the recipient is free from the blunders or not. Along these lines we are tried it for equality and CRC mistakes.

### 2. RESEARCH WORK

### **2.1 UART**

universal asynchronous receiver-(UART) transmitter takes bytes information and transmits the individual bits in a consecutive manner. At the goal, a second UART re-amasses the bits into finish bytes. Each UART contains a move enroll, which the major strategy transformation among serial and parallel structures. Serial transmission of advanced data (bits) through a solitary wire or other medium is less expensive than parallel transmission through numerous wires. The UART generally does not straightforwardly produce or get the outer signs utilized between various things of gear. Isolate interface gadgets are utilized to change over the rationale level signs of the UART to and from the outside flagging levels, which might be institutionalized voltage levels, levels. different signs. current or Correspondence might be simplex (in one heading just, with no arrangement for the getting gadget to send data back to the transmitting gadget), full duplex (the two gadgets send and get in the meantime) or half duplex (gadgets alternate transmitting and accepting).

### 2.2 Data Framing

The sit out of gear, no information state is high-voltage, or fueled. This is a notable inheritance from telecommunication, in which the line is held high to demonstrate that the line and transmitter are not harmed. Each character is surrounded as a rationale low begin bit, information bits, perhaps an equality bit, and at least one stop bits. In many applications the slightest noteworthy information bit (the one on the left in this outline) is transmitted first, yet there are special cases, (for example, the IBM 2741 printing terminal). The begin bit flags the collector that another character is coming. The following five to nine bits, contingent upon the code set utilized, speak to the character. In the event that an equality bit is utilized, it would be put after the majority of the information bits. The following a couple of bits are dependably in the check (rationale high, i.e., '1') condition and called the stop bit(s). They flag the collector that the character is finished. Since the begin bit is rationale low (0) and the stop bit is rationale high (1) there are dependably no less than two ensured flag changes between

A Peer Revieved Open Access International Journal

www.ijiemr.org

characters. On the off chance that the line is held in the rationale low condition for longer than a character time, this is a break condition that can be identified by the UART.

#### 2.3 Receiver

All activities of the UART equipment are controlled by a time flag which keeps running at a different of the information rate, commonly 8 times the bit rate. The beneficiary tests the condition of the approaching sign on each clock beat, searching for the start of the begin bit. In the event that the evident begin bit keeps going something like one-portion of the bit time, it is legitimate and flags the beginning of another character. If not, it is viewed as a deceptive heartbeat and is overlooked. In the wake of holding up a further piece time, the condition of the line is again tested and the subsequent level timed into a move enroll. After the required number of bit periods for the character length (5 to 8 bits, ordinarily) have slipped by, the substance of the move enroll are made accessible (in parallel design) to the getting framework. The UART will set a banner showing new information is accessible, and may likewise produce a processor hinder to ask for that the host processor exchanges the got information. Imparting UARTs more often than have no mutual not planning framework separated from the correspondence flag. Normally, UARTs resynchronize their inward timekeepers on each difference in the information line that isn't viewed as a fake heartbeat. Acquiring timing data in this way, they dependably get when the transmitter is sending at a marginally unexpected speed in comparison

to it should. Oversimplified UARTs don't do this, rather they resynchronize on the falling edge of the begin bit just, and after that read the focal point of each normal information bit, and this framework works if the communicate information rate is sufficiently precise to enable the stop bits to be tested dependably. It is a standard component for a UART to store the latest character while accepting the following. This "twofold buffering" gives a getting PC a whole character transmission time to get a got character. Numerous UARTs have a little first-in, first-out FIFO support memory between the beneficiary move enlist and the host framework interface. This permits the host processor much more opportunity to deal with a hinder from the UART and forestalls loss of got information at high rates.

#### 2.4 Transmitter

Transmission activity is more straightforward as the planning does not need to be resolved from the line state, nor is it bound to any settled planning interims. When the sending framework stores a character in the move enroll (after culmination of the past character), the UART produces a begin bit, moves the required number of information bits out to the line, creates and sends the equality bit (if utilized), and sends the stop bits. Since fullduplex task expects characters to be sent and got in the meantime, UARTs utilize two distinctive move registers for transmitted and got characters. Superior UARTs could contain a transmit FIFO (first in first out) cradle to enable a CPU or DMA controller to store different characters in a burst into the FIFO instead of need to store one character

A Peer Revieved Open Access International Journal

www.ijiemr.org

at any given moment into the FIFO. Since transmission of a solitary or different characters may take quite a while in respect to CPU speeds, a UART keeps up a banner demonstrating occupied status so the host framework knows whether there is somewhere around one character in the transmit cradle or move enroll; "prepared for next character(s)" may likewise be motioned with an interfere.

### 2.5 Application

Transmitting and accepting UARTs must be set for a similar piece speed, character length, equality, and stop bits for legitimate activity. The getting UART may recognize some befuddled settings and set an "encircling mistake" hail bit for the host framework: in remarkable accepting UART will deliver an inconsistent stream of disfigured characters exchange them to the host framework. Regular serial ports utilized with PCs associated with modems utilize eight information bits, no equality, and one stop bit; for this design the quantity of ASCII characters every second equivalents the bit rate separated by 10. Some minimal effort home PCs or implanted frameworks get rid of a UART and utilize the CPU to test the condition of an info port or specifically control a yield port for information transmission. While extremely concentrated (since the CPU timing is basic), the UART chip would thus be able to be precluded, setting aside some cash and space. The method is known as bitslamming.

#### 3. IMPLEMENTATION

In parallel correspondence the expense and in addition many-sided quality

of the framework increments because of concurrent transmission of information bits on various wires. Serial correspondence eases this downside and rises as powerful strategy in numerous applications for long separation correspondence as it decreases the flag mutilation in light of its basic structure. Widespread Asynchronous Receiver Transmitter (UART) is a sort of correspondence convention. serial Universal Asynchronous Receiver Transmitter (UART) is a mainstream and generally utilized gadget for information correspondence in the field of media transmission. It has numerous points of interest, for example, straightforward assets, dependable execution, solid antijamming capacity, simple to work and acknowledge et cetera. The UART is a vast scale coordinated circuit which contains all the product programming important completely control the serial port of a PC (Personnel PC). UART performs parallel-totransformation on information character got from the host processor into serial information stream, and serial-toparallel change on serial information bits got from serial gadget to the host processor. It likewise includes the begin and stop bit to information for synchronization. Notwithstanding the essential occupation of changing over information from parallel to serial for transmission and from serial to parallel on gathering, a UART will generally give extra circuits to signals that can be utilized to show the condition of the transmission media and to manage the stream of information if the remote gadget acknowledge isn't set up to information.

A Peer Revieved Open Access International Journal

www.ijiemr.org

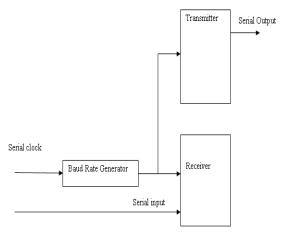

### 3.1 The UART Modules

The UART serial correspondence module is partitioned into three sub-modules: the baud generator, recipient module transmitter module Therefore, the execution of the UART correspondence module is really the acknowledgment of the three submodules .The baud rate generator is really a recurrence divider that can be ascertained by framework clock recurrence and the coveted baud rate. The capacity of baud rate generator is to create a nearby clock flag which is substantially higher than the baud rate to control the UART get and transmit. The collector performs serial-to-parallel change on the nonconcurrent information outline got from the serial information input. The transmitter module changes over the bytes into serial bits as per the fundamental casing position got from the CPU. With a specific end goal to synchronize the offbeat serial information and to safeguard the information trustworthiness, begin, equality and stop bits are added to the serial information. **UART** has standard information outline design which comprises of a begin bit '0', 5-8 bits information, discretionary equality bit and stop bit '1'. Fig.3.2 demonstrates the information outline arrangement of a UART. While out of gear state, serial information line will be in rationale '1' state. A begin bit '0' toward the start of the information casing will cause a falling edge on the serial information line. This denotes the recognition information character. Start bit and stop bit in UART is to accomplish information synchronization. A discretionary equality bit can be in odd equality or even equality. Odd equality implies that aggregate of all bits

gives an odd number, while even equality implies whole of all bits gives a considerably number. The serial information outline is moved out with the slightest huge piece (LSB) first.

Fig 1: UART Basic Block Diagram

#### 3.2 Bit UART Module

In the ongoing year, an altered UART configuration is proposed with programmed address sign, which is called 9-bit UART. In a transmission utilizing typical UART, each Slave gadgets will look each character transmitted for deliver byte and endeavor to coordinate with its remarkable location. This outcomes in a considerable measure of squandered preparing time for gadgets. In a 9-bit organize. UART utilizes the ninth piece of a character to separate between a location or an information character by designing ninth piece of UART information outline by '0' or '1' for information character and address character individually. Utilizing this ninth piece, Slave gadgets can recognize a location byte, contrast the location and choose whether with acknowledge or dispose of the approaching information bytes. This diminishes the handling time of the Slave's CPU.

A Peer Revieved Open Access International Journal

www.ijiemr.org

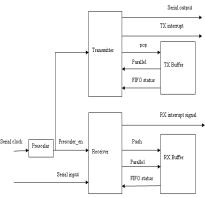

# 3.3 Proposed Work

The 9-bit UART configuration proposed comprises of the essential sub modules of a UART which are the recipient, transmitter and baud rate generator that we called prescaler.

Fig 2 Simplified proposed Block Diagram

Notwithstanding that, this plan has interior cradles in both collector and transmitter. Since this outline works in serial clock space and interfaces with parallel clock area of the processor, we execute the cushions by utilizing nonconcurrent FIFOs. The offbeat **FIFO** configuration gives smooth information exchange between two distinctive clock areas. Fig 4.2 beneath delineates the general square chart of the 9bit UART.In the above fig 4.2 existing square outline is clarified about the past work same as the procedure of proposed square graph. be that as it may, in these the two contemplations in just distinction are existing in clarified every single square however proposed are in generally speaking UART explanation concerning states are there and task are additionally contrast contrasted with the two frameworks etherise existing or proposed working standards are very unique.

Fig 3 Proposed Block Diagram

In this above fig 4.3 proposed square outline to clarified the present activity of UART in this we have beneath transmitter, recipient and prescaler module are there these three modules are clarified about aggregate working of proposed framework. In these above square outline remotely associated TX, RX and prescaler these three are conveniently clarifying and exclusively about status, begin, clk, information, and stop principle inputs most importantly status toss Tx and subsequent to going to Rx handling will be on working.

#### **Transmitter**

UART will be in transmission mode when TXMODE is empowered in the setup enlist of the UART. The processor sets the goal address, information byte(s) to be sent and other transmission settings. Transmission information bytes are spared into an inside TX support before being prepared for transmission. Transmitter module changes over the location and information got from the processor into serial bits, and includes begin bit of "0", equality bit of "1" for address byte or "0" for information byte, and stop bit of "1". The location can be a communicated address or a novel deliver that has a place with a particular Slave gadget. Accordingly the accompanying information bytes can be a communicated message implied for all Slave gadgets or a

A Peer Revieved Open Access International Journal

www.ijiemr.org

particular direction for a particular Slave device.

### 3.4 Error Detection Algorithm

**Euclidean Distance:**

Hamming separation isn't constantly reasonable for code plan. As a rule, in the event that we utilize a delicate choice decoder at the beneficiary, Euclidean metric is utilized as outline criteria and the coding plans are picked that boost the base Euclidean separation. Additionally if the channel is thought to be Gaussian with high SNR, Euclidean separation rules the blunder Notwithstanding, bound. Euclidean separation isn't utilized for Raleigh Fading channels and hard choice disentangling, rather hamming separation is utilized as a rule in such a situation. Both Hamming separation and Euclidean separation can be condensed utilizing a general recipe called MinKowsky condition given by,

D (A,B)= $[\sum ni=1wi[ai-bi]P]1/P$ Where if,

P=1 => Manhattan Distance

P=2 => Euclidean distance

P=1 and ai, bi  $\in \{0,1\} \Rightarrow$  Hamming distance

W is a weighting factor which is set to '1' when computing Euclidean/Hamming distances.

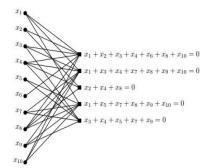

LDPC codes are straight codes acquired from scanty bipartite diagrams. Assume that

G is a diagram with n left hubs (called message hubs) and r right hubs (called check hubs). The chart offers ascend to a straight code of square length n and measurement at any rate n - r in the accompanying way: The n directions of the code words are related with the n message hubs. The codeword's are those vectors  $(c1, \ldots, cn)$  with the end goal that for all check hubs the aggregate of the neighboring positions among message hubs is zero. Figure 2 gives a model. The chart portrayal is similar to a framework portrayal by taking a gander at the nearness lattice of the diagram: let H be a parallel  $r \times n$ -network in which the passage (I, j) is 1 if and just if the ith check hub is associated with the jth message hub in the diagram.

At that point the LDPC code characterized by the chart is the arrangement of vectors c =  $(c1, \ldots, cn)$  with the end goal that  $H \cdot c >$ = 0. The lattice H is known as an equality check grid for the code. On the other hand, any parallel r × n-framework offers ascend to a bipartite chart between n message and r check hubs, and the code characterized as the invalid space of H is correctly the code related to this diagram. Hence, any straight code has a portrayal as a code related to a bipartite diagram (take note of that this chart isn't interestingly characterized by the code). Be that as it may, only one out of every odd twofold straight code has a portrayal by a meager bipartite graph.1 If it does, at that point the code is known as a low-thickness equality check (LDPC) code. The sparsity of the chart structure is key property that takes into consideration the algorithmic proficiency of LDPC codes. Whatever is left

A Peer Revieved Open Access International Journal

www.ijiemr.org

of this note is committed to expounding on this relationship.

#### 4. RESULTS

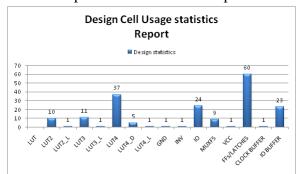

# **Design Cell Usage Statistics Report**

In this outline cell utilization insights report in what number of LUTs, FF, IOBs, IOs, hooks, GND, VCC, and CBs are said underneath configuration of diagram plan .these are utilized for finish configuration circuit use parts and rationale components.

Fig 4: Design statistics of cell usage

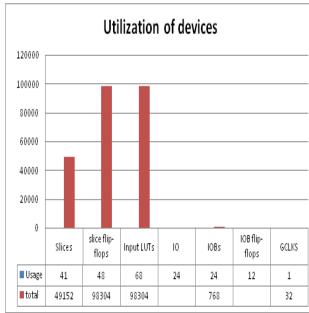

In the below bar chart is demonstrate about how many slices slice flip-flops, LUTs, IOBs, IOs and GCLKs are utilized the total elements and utilizations are compared.

Fig 5: Device utilization

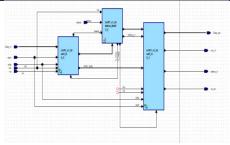

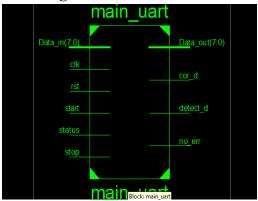

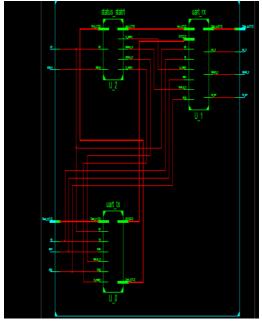

# RTL and schematic diagrams

### **RTL Diagram**

Fig 6.3 RTL diagram

### Schematic diagram

Fig 6.4 RTL Schematic diagram

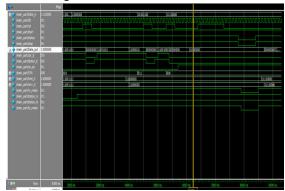

# **Error ouput**

Fig 6.6: error output

A Peer Revieved Open Access International Journal

www.ijiemr.org

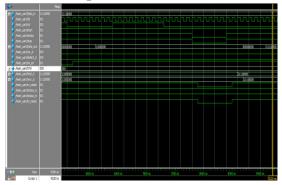

# **Correct Output**

Fig 6.7: without error output

### 5. CONCLUSION

We have reproduced the outline utilizing Xilinx and Model sim Simulation apparatus. 6 demonstrates the reenactment waveform of the recipient module. In the reenactment, collector module is out of gear state subsequent to being reset. At the point when a begin bit is identified, state machine is being actuated. Equality bit got is rationale "1"; along these lines this shows a location byte. The recipient catches the information address of 8"h01 and spare it in rx data enlist to be contrasted and UART"s claim address and communicate address. Fig. 6 Simulation waveform of beneficiary Fig.5.7 beneath demonstrates the reenactment waveform of the transmitter module. In this reenactment, UART will transmit out an information byte of 8"hCB. The transmitter module includes begin bit of "0", moved information byte as "11010011", sets equality bit to ,,0" and 1 stop bit of ,,1". From the waveform, we can see that the yield on the serial information line, po\_sout is right. In this paper, an adjusted UART configuration is proposed with programmed address sign, which is called 9-bit UART. The 9-bit UART configuration is actualized utilizing Verilog HDL and mimicked to see the usefulness of each sub-modules and the outcome. This plan demonstrates that utilizing the ninth piece strategy gives preferred standpoint of sparing the UART preparing time by contrasting the location and chooses whether with get or overlooks the approaching information bundles. The stop bit blunder checking component in this plan additionally offers information honesty checking. With every one of the highlights specified, it adds to the adaptability, strength and dependability to the ordinary UART plan that is generally being utilized.

### 6. REFERENCES

- [1] J. Norhuzaimin, and H.H. Maimun, "The design of high speed UART," Asia Pac. Conf. on Appl. Electromagnetics (APACE 2005), Johor, Malaysia, Dec. 2005.

- [2] C. He, Y. Xia, and L. Wang, "A universal asynchronous receiver transmitter design," Int'l Conf. on Elect. Comm. and Control (ICECC 2011), Ningbo, China, Sept. 2011.

- [3] Y. Wang, and K. Song, "A new approach to realize UART," Int'l Conf. on Elect. and Mech. Eng. and IT (EMEIT 2011), Harbin, Heilongjiang, China, Aug. 2011.

- [4] Using a 9-bit Software UART with Stellaris® Microcontrollers Application Note (AN01280), Texas Instruments, P.O. Box 655303, Dallas, Texas 75265, USA, Aug. 2010.

- [5] Zilog Z8 Encore! XP® 9-bit UART Implementation Application Note (AN014602-1207), Zilog Inc., Dec. 2007.

- [6] Z. Zhang, and W. Wu, "UART integration in OR1200 based SoC Design," 2nd Int'l Conf. on Comp. Eng. and Tech. (ICCET 2010), Chengdu, China, Apr. 2010.

- [7] Y. Fang, and X. Chen, "Design and simulation of UART serial communication module based on VHDL," 3 rd Int'l

A Peer Revieved Open Access International Journal

www.ijiemr.org

Workshop on Intel. Sys. and App. (ISA 2011), Wuhan, China, May 2011.

- [8] C.E. Cummings, "Simulation and synthesis techniques for asynchronous FIFO design," Synopsys User Group (SNUG), San Jose, USA, 2002.

- [9] X. Wang, and J. Nurmi, "A RTL asynchronous FIFO design using modifiedmicropipeline," The 10th Biennial Baltic Elect. Conf. (BEC 2006), Tallinn, Estonia, Oct. 2006.

- [10] X. Wang, T. Ahonen, and J. Nurmi, "A synthesizable RTL design of asynchronous FIFO," in Proc. Int'l Sympo. OnSoC 2004, Tampere, Finland, Nov. 2004.