A Peer Revieved Open Access International Journal

www.ijiemr.org

### **COPY RIGHT**

**2018IJIEMR**. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 11th Dec 2018. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-07&issue=ISSUE-13

Title: HIGH STEP-UP CLOSED LOOP CONTROLLED DC-DC CONVERTER WITH MINIMUMOUTPUT VOLTAGE RIPPLE

Volume 07, Issue 13, Pages: 153-165.

**Paper Authors**

# KALYANAM HARITHA,S M GAVASKAR MEDABALIMI,GOWSE BASHEED SHAIK

ST MARY'S Engineering College, CHEBROLU; GUNTUR (Dt); AP, India

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic

Bar Code

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

# HIGH STEP-UP CLOSED LOOP CONTROLLED DC-DC CONVERTER WITH MINIMUMOUTPUT VOLTAGE RIPPLE

<sup>1</sup>KALYANAM HARITHA, <sup>2</sup>S M GAVASKAR MEDABALIMI, <sup>3</sup>GOWSE BASHEED SHAIK

<sup>1</sup>M-tech Student Scholar, Department of Electrical & Electronics Engineering, ST MARY'S Engineering College, CHEBROLU; GUNTUR (Dt); AP, IInda

<sup>2</sup>Assistant Professor, Department of Electrical & Electronics Engineering, ST MARY'S Engineering College, CHEBROLU; GUNTUR (Dt); AP, India

<sup>3</sup>Assistant Professor, Department of Electrical & Electronics Engineering, ST MARY'S Engineering College, CHEBROLU; GUNTUR (Dt); AP, India

<sup>1</sup>harithakalyanam220@gmail.com, <sup>2</sup>gavaskar267@gmail.com, <sup>3</sup>gowse.basha@gmail.com

**ABSTRACT** A new high step-up dc—dc converter with high voltage gain is proposed on this work. This converter is suitable for the applications with a high voltage gain between the input and the output. The proposed converter combines the it is possible to extend the topology by increasing the number of active—passive inductor cells. High voltage gain with lower duty cycle, low-current and —voltage stresses on switches, small inductors, and small size of filter are the main advantages of the proposed structure. The proposed converter is analyzed in different operating modes. In order to design the components' values of the proposed converter, the equations of output voltage ripple are calculated in each operating mode and a design procedure is proposed based on the aforementioned equations.. In order to verify the feasibility topology; principle of operation, simulation analysis, and closed loop operation, reference and line regulations and waveforms are shown.

**Index Terms**—Active–passive inductor cell (APIC), high step-up dc–dc converter, high voltage gain, output voltage ripple (OVR).

#### 1. INTRODUCTION

The future is looking towards alternative power sources allof which will need to be regulated in one Form or another. To make this possible, a highly efficient low cost productwill have to be designed. Among all the different converterdesigns only a few are capable of providing high powerwith high efficiency. The basic switched-mode dc-dcconverters including boost, buck-boost, cuk, andsepic have been used in various electronic applications dueto their numerous advantages such as good performance, simple structure, , high

efficiency, easy design, and simplecontrol circuit. To get high voltage from low voltage boostconverters are used. The high voltage converters are widely used in many industry applications, such asphotovoltaic systems, fuel cell systems, vehicles, and high intensity discharge lamps. PV cells can beconnected in series order obtain large voltage. Though PV cells can be made into array and connected inseries to produce high voltage there exist serious problemslike shadowing effects, short which drasticallyreduces circuit

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

efficiency. In order to overcome such adverseeffects this micro source energy is utilized by the high stepup converter to high voltage and thedemands. Thus high step up dc-dc converters are used asfront end converters to step from low voltage to highvoltage which are required to have a large conversion ratio, high efficiency and small volume [2].The conventional converters are not suitable for thehigh conversion [3] applications because the dutycycle of the boost converter with high step-up conversionis large, which results in narrow turn off time. Theextremely narrow turn-off time will bring large peakcurrent considerable conduction and switching losses[4] .conventional boost converter is shown in fig(1). However extreme duty ratio will result in serious reverserecovery problems electromagnetic and interferences.Impacts of SiC (silicon **MOSFETS** carbide) on converter, switching and conduction losses are reduced even thoughfast switching is done. Si diodes have ideal, but sill SiCdevices processes large amount of ringing current at turnoff relatively to other devices. And the SiC are comparing0with [5].Forward converter, push-pull flybackconverters converter and transformer based converters (isolatedconverters) ,can achieve high voltage gain by adjusting theturns ratio of transformers. But it thedisadvantages of voltage spike across the main switch andpower dissipation due to leakage inductance of the transformer [7] and safety standard needs [8]. In [9] itproposes a novel single switch high stepup converter. The coupled inductor is act as both forward and flybackconverter, thus it can charge two capacitors in parallel

anddischarge high in series.A transformer less converter is presented consisting in[10]. It of hybrid combination of two twolevel dc/dc converters . Thus it have large no ofcomponents and it will increase cost. Switched capacitortechniques have been widely inorder to improve highvoltage gain [11-12]. But here high charging current willflowing through main switch and increase the conductionlosses. Converters with charge pump will provide voltage gainin proportion to the stage number of capacitors, but itsdrawback includes fixed voltage gain and large device area.In [15] diode techniques are implemented. It canachieve high voltage gin in proportional to the number ofstages, which is able to be extended by adding capacitors and diodes. But it may result in the larger voltage dropconsumption due to cut in voltage of the diodes in series. Tapped inductor technology is explained in [13]. Different converter topologies are explained. Coupledinductor based converters also achieve high step-upvoltage gain by adjusting the turns ratio [14]. However thestored energy in the leakage inductor causes a voltagespike on the main switch and deteriorates the conversionefficiency. To overcome this problem, coupled inductorbased converter with active clamping circuits are presented [16].It proposed compare converter andconventional boost converter with coupled inductor onlyand active clamp circuit only. High step-up converter withtwo switch [17-19] and one switch [20] are explained. Asno of switches increased losses will increased. However theconversion ratio is not large enough.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

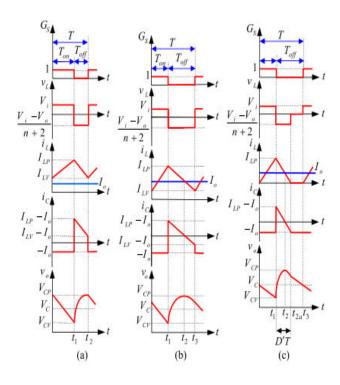

### 2 PROPOSED CONVERTER

The power circuit of the proposed converter is shown in Fig. 1. The operation of this converter in continues conduction mode (CCM) is classified into complete inductor supply mode (CISM) incomplete inductor supply mode (IISM). Discontinues conduction mode (DCM) just includes IISM. To simplify the analysis, all elements are assumed ideal and also the capacitance of capacitors is considered high and all of the inductors have the same inductance. In the proposed converter, by comparing minimum current of inductors with load current, CISM and IISM operations are determined. In CISM, the minimum current of inductors is more than the load current, whereas in IISM, the minimum current of inductors is less than the load current. Current and voltage of the inductor, the capacitor current, and the voltage waveforms output operational modes are shown in Fig. 2.

# 3. ANALYSIS THE PROPOSED CONVERTER

# A Analysis of the Proposed Converter in CCM

Time interval of Ton: All of the switches are turned ON simultaneously and diodes D12, D22, . . . , Dn2 and D11, D21, . . . , Dn1, Do are turned ON and OFF, respectively. The voltage across the inductors is given by

$$v_L = V_i. (1)$$

Current of inductors is as follows:

$$i_L = \frac{V_i}{L}t + I_{LV}.$$

(2)

Considering (2), during this time interval, the inductors are charged and the current through them is increased so that in t = DT, the inductors current will be at its maximum value. Applying t = DT to (2), the maximum current of inductors is obtained as follows:

$$I_{\rm LP} = \frac{V_i DT}{L} + I_{\rm LV}. \tag{3}$$

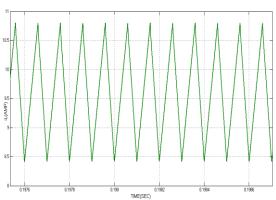

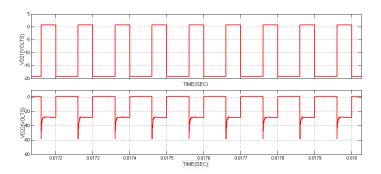

Fig.2. Voltage and current waveforms. (a) CISM-CCM. (b) IISM-CCM. (c) IISM-DCM.

During this time interval, the capacitor current equals to —Io and provides load current. At the end of this time interval, the capacitor energy is discharged and its voltage is decreased to VCV .Time interval of Toff: The switches are turned OFF simultaneously and diodes D12, D22, ..., Dn2 and D11, D21, ..., Dn1, Do are turned OFF and ON, respectively. The voltage across the inductors is given by

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

$$v_L = \frac{V_i - V_o}{n+2} \tag{4}$$

Where n is the number of the APICs. By assuming t1 = 0 (new time base), the inductors' current is calculated as follows:

$$i_L = \frac{V_i - V_o}{(n+2)L}t + I_{LP}.$$

(5)

In this time interval, the inductors are discharged and at the end of this time interval, their current is reached to ILV . Applying t = (1 - D)T to (5), the minimum current of inductors is given by

$$I_{\rm LV} = \frac{(V_i - V_o)(1 - D)T}{(n+2)L} + I_{\rm LP}.$$

(6)

During Toff, the capacitor current is calculated as

$$i_C = \frac{V_i - V_o}{(n+2)L}t + I_{LP} - I_o.$$

(7)

Considering (7), the currents of capacitor and inductors are decreased [see Fig 2(a)]. The inductors provide load current and also along charge the capacitor. During Toff, the capacitor is charged and its voltage is increased from VCV to VCP. The time interval of Toff in IISM-CCM is divided into times intervals of (t1, t2) and interval t3).Time of (t1, Considering (6), as iL decreases, iC will decrease and reaches zero at the moment of t2. Considering Fig. 2(b) and (7), iC decreases same as iL. iC decreases to the value of ILV – Io at the moment of t3.

The inductor and capacitor provide the load current together at this time interval. Voltage gain Calculation: By applying the volt-second balance law, and considering (1) and (4), the voltage gain is obtained as follows:

$$M_{\text{CCM}} = \frac{V_o}{V_i} = \frac{1 + (n+1)D}{1 - D}.$$

(8)

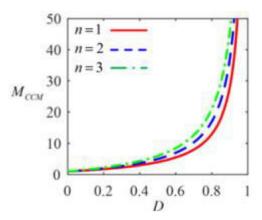

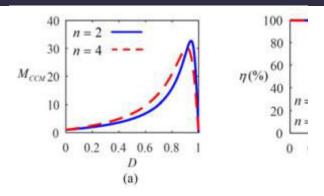

Fig. 3. Variation of voltage gain versus duty cycle and n.

Fig. 3 shows the variation of voltage gain versus duty cycle and n in CCM. As can be seen for certain value of duty cycle, as the value of n increases the voltage gain will be increased. Voltage stress of the diodes and switches: Similarly to the voltage gain, the normalized voltage stress of the diodes and switches versus output voltage can be obtained by applying volt-second balanced law. These results are given in Table I.

# **B.** Analysis of the Proposed Converter in DCM

This mode is divided into four time intervals. Time interval of Ton: Analysis of the proposed converter at this time interval is same as the CCM, which was mentioned before. By applying ILV = 0

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

and t = DT in (3), ILP is obtained as follows:

$$I_{\rm LP} = \frac{V_i DT}{L}.$$

(9)

Time interval Toff: This time interval is divided into three time intervals of (t1, t2), (t2, t2a), and (t2a, t3). Time interval of (t1, t2): iC and iL can be obtained from (5) and (7). The energy transmission process is same as CCM during (t1, t2) [see Fig. 2(c)]. Time interval of (t2, t2a): The energy transmission process is same as the CCM during (t1, t2) with a difference that iL is zero in t = t2a. In this time interval, capacitor's current equals load current. According to Fig. 2(c), the capacitor voltage decreases as the capacitor energy is discharged. Assuming t1 = 0 (new time base), ILP is as follows:

$$I_{\rm LP} = \frac{(V_o - V_i)D'T}{(n+2)L}.$$

(10)

By applying (9) to (10), D is obtained as follows:

$$D' = \frac{(n+1)V_i D}{(V_o - V_i)}.$$

(11)

Time interval of (t2a, t3): At this time interval, iC equals (-Io). The capacitor provides the load current alone. The capacitor's voltage decreases as the capacitor's energy is discharged [see Fig. 2(c)]. Voltage gain calculation: By using the current-second balance law for capacitor, voltage gain in DCM is obtained as follows:

$$\frac{V_o}{V_i} = \frac{1}{2} + \sqrt{\frac{(n+2)RD^2}{2Lf}} + \frac{1}{4}.$$

(12)

### **4 CRITICAL CONDUCTION MODE**

In order to determine the critical inductance between different operating modes, first, ILV should be obtained.

# A Critical Inductance Between CCM and DCM

The maximum current of inductors can be obtained as follows:

$$I_{\rm LP} = I_o \left[ \frac{1}{1-D} + \frac{RD}{2Lf} \frac{(1-D)}{[1+(n+1)D]} \right].$$

(13)

By applying (13) in (6), ILV is obtained as follows:

$$I_{\text{LV}} = I_o \left[ \frac{1}{1 - D} - \frac{RD}{2Lf} \frac{(1 - D)}{[1 + (n+1)D]} \right].$$

(14)

By applying ILV = 0 in (14), the critical inductance between CCM and DCM is obtained as follows:

$$L_C = \frac{(n+2)(V_o - V_i)V_i^2 R}{2fV_o[(n+1)V_i + V_o]^2}.$$

(15)

B. Critical Inductance Between CISM and IISM

By applying ILV = Io in (14), the critical inductance between CISM and IISM is obtained as follows:

$$L_K = \frac{(n+2)RV_i^2}{2fV_o[(n+1)V_i + V_o]}.$$

(16)

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

Fig. .4. (a) Variation of LC versus n. (b)

Variation of LK versus n

Variations of the critical inductances versus n are shown in Fig. .4. Considering Fig. 4(a), it is obvious that the critical inductance is decreased as the output voltage is increased. Therefore, for low value of inductance when the output voltage is high, the converter can operate in CCM. This figure shows that by increasing the number of APIC, LC is decreased and LK is increased.

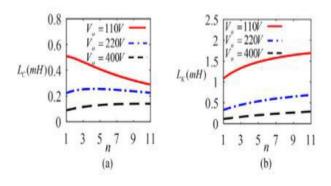

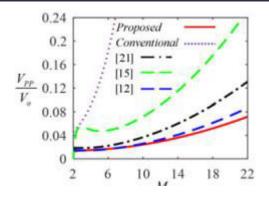

### **5 COMPARISON**

In this section, the proposed converter is compared with the literature. For comparison, some important indexes are shown in Table II. Variation of the voltage gain versus duty cycle is shown in Fig. 5(a). As it is shown, voltage gain of the proposed converter for n = 5 is more than the other converters. It is obvious that for lower duty cycles, voltage gain of the converter proposed in [15] is more than the others. But in this condition, the converter is not applicable in high voltage. Variation of the normalized voltage stress of the switches versus voltage gain is shown in Fig. 5(b). As can be seen the voltage stress of S is less than the others. As it is shown S is more than the others, for specific voltage gain. But by considering Fig. 5, this voltage gain for the proposed converter is obtained for low duty cycles compared with the others. Variation of the

maximum current of the switches versus voltage gain is shown in Fig. 5(c). As it is shown, the maximum current through the proposed converter switches is less than the others. It can be concluded for the proposed converter that the voltage stress and conduction loss of the switches is low. In [10], in addition to high current stress caused by using four coupled inductors, leakage inductance causes voltage stress to increase, too. Variation of the normalized power of the inductors versus voltage gain is shown in Fig. 5(d). As can be seen, the power of the proposed converter's inductors is lower than the others. Therefore, the inductance for proposed converter can be selected low; however, the amount of the power is just for one inductor but it is obvious that the summation of the powers is also lower than the others.

# 6 VOLTAGE GAIN AND EFFICIENCY IN REAL CONDITION

The average current through the inductors is as follows

$$I_L = \frac{I_o}{1 - D}. ag{17}$$

The average input current is as follows:

$$I_i = I_L[(n+1)D + 1].$$

(18)

By applying (17) in (18), the average input current is as

$$I_i = \frac{[1 + (n+1)D]}{1 - D} I_o.$$

(19)

The efficiency of proposed converter can be obtained by the following equation:

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

The voltage gain in real condition is obtained as follows:

$$\frac{V_o}{V_i} = \frac{M_{\text{CCM}}}{1 + \frac{(n+2)(r_s D + r_L)}{R(1-D)^2} + \frac{r_{Do} + Dr_C + nr_{D1}}{(1-D)R} + \sum_{j=0}^{n} (21)}$$

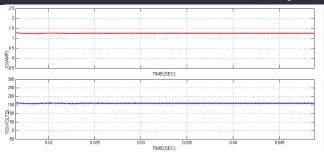

Variations of voltage gain and efficiency of the proposed converter versus duty cycle are shown in Fig. 6. This figure shows that in real conditions and for high values of duty cycle, by increasing the duty cycle, the voltage gain is decreased.

# 7 DESIGN OF THE PROPOSED CONVERTER

The designing of the proposed converter is done based on the OVR [22] and [23]. In order to have a minimum OVR, the value of the elements should be selected suitably.

### 7.1 Output Voltage Ripple

The OVR is calculated as follows:

$$V_{\rm CP} = V_{\rm CV} + \frac{1}{C} \int_0^t i_C dt. \tag{22}$$

According to (22), the OVR in CISM can be determined by integrating the capacitor current in time interval of Ton and also it can be determined in IISM-CCM and IISM-DCM, by integrating the capacitors current in (t1, t2). The OVR in the operation modes of the converter is obtained as Table III. As can be seen, the OVR is independent of inductance values

in CISM-CCM and is reversely related with Vi and R. The ratio of the OVR variations is reversely related with inductance, Vi, and R values in IISM-CCM and IISM-DCM. In order to design the converter, it is assumed that Vi,min Vi Vi,max and Rmin R R Rmax. As it is understandable from (15) and (16), LC and LK are functions of Vi and R. For a specific inductance, the converter can operate in one of the modes, whereas the input voltage and load resistance values vary. The minimum and maximum critical inductances are

# TABLE II PERFORMANCE BETWEEN DIFFERENT CONVERTERS

| Converter                                   | Conventional    | [21]                                  | [15]                            | [12]                                              | [10]                                                            | Proposed                                                                                                                          |

|---------------------------------------------|-----------------|---------------------------------------|---------------------------------|---------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Switches                                    | 1               | 2                                     | 1                               | 1                                                 | 2                                                               | n + 2                                                                                                                             |

| Diodes                                      | 1               | 1                                     | 3                               | 2                                                 | 2                                                               | 2n                                                                                                                                |

| Inductors                                   | 1               | 1                                     | 2                               | 2                                                 | 4                                                               | n+2                                                                                                                               |

| Voltage gain                                | $\frac{1}{1-D}$ | $\frac{1+D}{1-D}$                     | $\frac{2-D}{1-D}$               | $\frac{1+ND}{1-D}$                                | $\frac{1+(2N+1)D}{1-D}$                                         | $\frac{1+(n+1)D}{1-D}$                                                                                                            |

| Voltage stress of the switches              | $V_o$           | $\frac{V_{\phi}\left(1+M\right)}{2M}$ | $\frac{V_0\left(1-M\right)}{M}$ | $\frac{V_{o}\left(N+M\right)}{\left(N+1\right)M}$ | $\frac{V_o\left[(2N+1)+M\right]}{(2N+2)M}$                      | $\frac{V_{\phi}\left[\left(n+1\right)+M\right]}{\left(n+2\right)M}$                                                               |

| Summation of Voltage stress of the switches | $V_o$           | $\frac{V_{\phi}(1+M)}{M}$             | $\frac{V_{\phi}(1+M)}{2M}$      | $\frac{V_O\left(N+M\right)}{\left(N+1\right)M}$   | $\frac{V_O\left[\left(2N+1\right)+M\right]}{\left(N+1\right)M}$ | $\frac{V_{o}\left[\left(n+2\right)\left(1+M\right)+M\right]+\sum_{j=1}^{n}\left[\left(n-j+2\right)+jM\right]}{\left(n+2\right)M}$ |

| Voltage stress of the output diode          | $V_{o}$         | $\frac{V_{\phi}(1+M)}{M}$             | $\frac{V_{\theta}(M+1)}{M}$     | $\frac{V_0 N (N+M)}{(N+1)M}$                      | $\frac{V_{\theta}(1+2N)[(2N+1)+M]}{(2N+2)M}$                    | $\frac{V_o\left(1+M\right)}{M}$                                                                                                   |

| The maximum current through the switches    | $2I_i$          | $\frac{I_i\left(1+M\right)}{M}$       | $I_i$                           | $\frac{(M+N)(1+N)I_{i}}{M(N+2)-1}$                | $\frac{I_{i}(1+N)(2N+M+1)I_{i}}{(2N+2)M}$                       | $\frac{I_{j}\left(n+1+M\right)}{\left(n+2\right)M}$                                                                               |

| Efficiency $P_{out} = 200 \text{W}$         | %98.33          | %98.89                                | %90.5                           | %93.8                                             | %95.1                                                           | %96.35                                                                                                                            |

Fig. 5. Variation of (a) the voltage gain versus duty cycle, (b) voltage stress of the switches, (c) maximum current of the switches, (d) normalized power of the inductors versus voltage gain.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

Fig. 6. Variation of (a) voltage gain and (b) efficiency versus duty cycle.

given, respectively, as follows:

$$L_{C,\min} = \frac{(n+2)(V_o - V_{i,\min})V_{i,\min}^2 R_{\min}}{2fV_o[(n+1)V_{i,\min} + V_o]^2}$$

(23)

$$L_{C,\text{max}} = \frac{(n+2)(V_o - V_{i,\text{max}})V_{i,\text{max}}^2 R_{\text{m}}}{2fV_o[(n+1)V_{i,\text{max}} + V_o]^2}$$

(24)

### TABLE III

# OUTPUT VOLTAGE RIPPLE IN THE OPERATION MODES

### TABLE IV

# DIFFERENT OPERATIONAL MODES IN THE PROPOSED CONVERTER

### VERSUS INDUCTANCE VALUES

| State                                       | Operational mode |      |

|---------------------------------------------|------------------|------|

| $L > L_{C, \text{max}}$                     | CCM              |      |

| $L < L_{C, min}$                            | DCM              |      |

| $L_{C, \text{min}} < L < L_{C, \text{max}}$ | $L > L_C$        | CCM  |

| .,                                          | $L < L_C$        | DCM  |

| $L > L_{K,max}$                             | CISM             |      |

| $L < L_{K, min}$                            | IISM             |      |

| $L_{K,\text{min}} < L < L_{K,\text{max}}$   | $L > L_K$        | CISM |

|                                             | $L < L_K$        | IISM |

$$L_{K,\min} = \frac{(n+2)R_{\min}V_{i,\min}^2}{2fV_o[(n+1)V_{i,\min} + V_o]}$$

(25)

$$L_{K,\text{max}} = \frac{(n+2)R_{\text{max}}V_{i,\text{max}}^2}{2fV_o[(n+1)V_{i,\text{max}} + V_o]}.$$

(26)

Classification of the modes and the operational regions versus the inductance values is shown in Table IV.

### 7.2 Maximum Output Voltage Ripple

The maximum OVR (MOVR) for a specific inductance value is obtained as Vi,min and Rmin. Due to the different inductance values, the operational region of proposed converter can possess five distinctive sections on the inductance axis. Parameters LK,min and LC,max significantly Vi related to and R. Therefore, the operation region classification would differ considering LC max <LK,min or LC max >LK,min conditions. Analysis the MOVR for the proposed converter is as same as [22] and [23]. Relation between MOVR in the operational region

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

Fig. 7. Variation of the normalized OVR versus voltage gain.

# TABLE V MAXIMUM CURRENT THROUGH THE SWITCHES

$$\begin{array}{ll} \text{CCM} & I_{\text{SP}}^{\text{CCM}} = \frac{V_o \left[ V_o + (n+1) V_i \right]}{(n+1) \text{RV}_i} + \frac{(V_o - V_i) V_i}{2 L f \left[ V_o + (n+1) V_i \right]} \\ \\ \text{DCM} & I_{\text{SP}}^{\text{DCM}} = \sqrt{\frac{2 V_o \left( V_o - V_i \right)}{(n+2) R f L}} \end{array}$$

of proposed converter is as follows:

$$L_{C \max} < L_{K,\min}$$

$V_{\text{PP1,max}} > V_{\text{PP2,max}} > V_{\text{PP3,max}} > V_{\text{PP4,max}} = V_{\text{PP5,m}}$

(27)

$$L_{C,\text{max}} > L_{K,\text{min}}$$

$V_{PP1,\text{max}} > V_{PP2,\text{max}} > V_{PP3,\text{max}} = V_{PP4,\text{max}} = V_{PP5,\text{m}}$

(28)

Variation of the normalized OVR versus voltage gain is shown in Fig. 7. The curves are plotted under the same condition for all of the converters, as can be seen the OVR of the proposed converter is lower than the others for high voltage gains. But it has the same amount as [12] in low voltage gains.

### 7.3 Current Stress of the Switches

The maximum current of switches equals the maximum current of inductors. The maximum current of switches in CCM and DCM is given in Table V. The maximum value of iS in CCM and minimum value in DCM are obtained for L = LCConsidering (15) in Table V, results in

$$I_{\text{SP,min}}^{\text{DCM}} = I_{\text{SP,max}}^{\text{CCM}} = \frac{V_o[(n+1)V_i + V_o]}{(n+2)RV_i}.$$

(29)

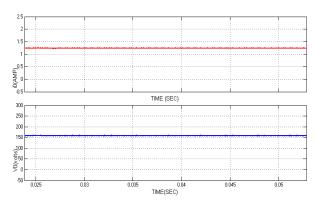

### **8.Closed loop Operation**

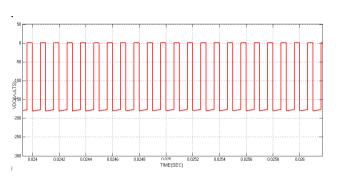

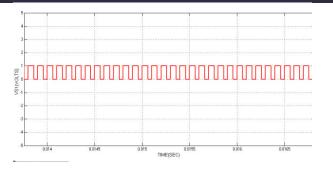

The closed loop operation carried out by the voltage controller (PI controller) processes the error signal and produces appropriate current signal (IS). The current signal (IS) is multiplied with unit sinusoidal template which is produced by using phase locked loop (PLL), to produce IS sinωt. The load current iLsubtracted from the IS sin ωt to produce the reference current signal  $iS^*$ . As the boost inductor current can't be alternating, the absolute circuit gives the absolute value of the reference current signal  $iS^*$  that is  $iC^*$ . The actual signal (iC) and the required reference signal  $(iC^*)$  are given to the current controller to produce the proper gating signal. The current controller adopted is a hysteresis current controller. Upper and lower hysteresis band is created by adding and subtracting a band 'h' with the reference signal  $iC^*$  respectively shown in the Fig. 8. The inductor current is forced to fall within the hysteresis band. When the current goes above the upper hysteresis band, i.e. iC \*+h, the pulse is removed resulting the current forced to fall as the current will flow through the load. When the current goes below the lower hysteresis band i.e. iC \*-h, the pulse is given to the switch, so the current increases linearly.

Fig 8 Adopted control scheme for the Closed Loop operation

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

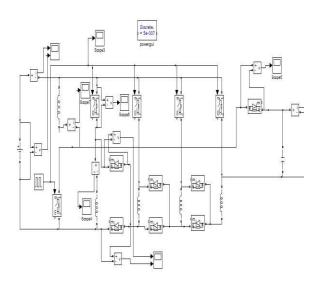

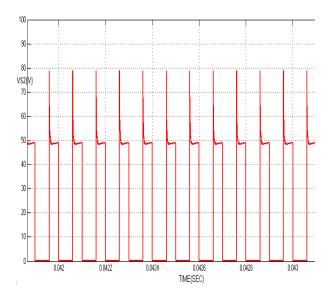

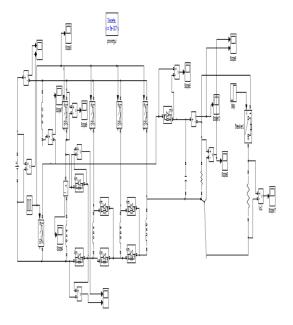

# 9. MATLAB AND SIMULINK RESULTS

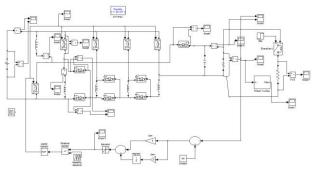

FIG 9 simulink diagram of proposed concept

(a)  $L=500 \mu H$ .

(b)  $L = 700 \mu H$ .

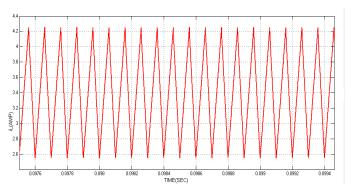

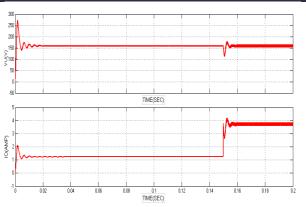

fig. 10 simulation results for vi,m in = 20 v and rm in = 150  $\omega$ .

fig 11 Voltage stress of the diode (vdo)

fig 12 Voltage stress of the diodes (vd21 & vd22)

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

fig 13 Voltage stress of the swithVs1

fig 14 Voltage stress of the swithVs1

fig 15simulink diagram of sudden load changes of proposed concept

fig 16 resistive load output voltage and current wave forms

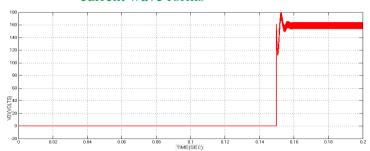

fig 17 sudden load output voltage wave forms

fig 18simulink diagram of proposed concept with closed loop system

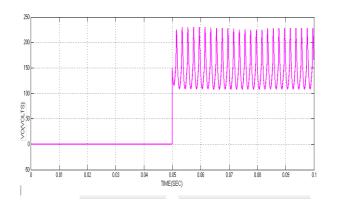

fig 19: final output voltage waveform of closed loop system

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

### 9)CONCLUSION

In this paper, a high step-up dc-dc converter was proposed. In the proposed converter by increasing the number of APICs, the voltage gain is increased and voltage stresses on switches is decreased. The high voltage gain has been obtained for low duty cycle that it results in reducing the conduction loss of converter. Maximum current of switches is low that can cause low conduction loss, too. Because of low inductor current ripple, inductor with small inductance is needed, which causes reduction in the size of the magnetic core. Moreover, the critical inductance is reduced by increasing the number of APICs. In the proposed converter, because the switches are turned ON and OFF simultaneously, so, one switching control circuit can be used. The elements of converter were designed based on the maximum output voltage ripple. Closed loop operation of dc-dc converter; line and reference regulations, principle of operation, Simulation analysis, and waveforms are discussed.

### **REFERENCES**

- [1] W. Li and X. He, "Review of nonisolated high-step-up dc/dc converters in photovoltaic grid-connected applications," IEEE Trans. Ind. Electron., vol. 58, no. 4, pp. 1239–1250 Apr. 2011.

- [2] D. Cao, S. Jiang, and F. Z. Peng, "Low cost transformer isolated boost half-bridge micro-inverter for single-phase grid-connected photovoltaic system," in Proc. IEEE Appl. Power Electron. Conf., Orlando USA, 2012, pp. 71–78.

- [3] M. Nymand and M. A. E. Alldersen, "High efficiency isolated boost dc/dc converter for high power low voltage fuelcell applications," IEEE Trans. Ind.

Electron., vol. 57, no. 2, pp. 505–514, Feb. 2010.

- [4] C.-M. Wang, "Wang A novel ZCS–PWM flyback converter with a simple ZCS PWM commutation cell," IEEE Trans. Ind. Electron., vol. 55, no. 2, pp. 749–757, Feb. 2008.

- [5] H. MashinchiMaheri and E. Babaei, "Mathematical modeling of buckboost DC–DC converter and investigation of converter elements on transient and steady state responses," Int. J. Elect. Power Energy Syst., vol. 44, no. 1 pp. 949–963, Jan. 2013.

- [6] L. Huber and M. M. Jovanovic, "A design approach for server power supplies for networking applications," in Proc. 15th Annu.IEEE Appl. Power Electron. Conf. Exp., New Orleans, LA, USA, 2000, pp. 1163–1169.

- [7] T. F. Wu, Y. S. Lai, J. C. Hung, and Y. M. Chen, "Boost converter with coupled inductors and buck-boost type of active clamp," IEEE Trans. Ind. Electron., vol. 55, no. 1, pp. 154–162, Jan. 2008.

- [8] Y. P. Hsieh, J. F. Chen, T. J. Liang, and L. S. Yang, "Novel high step-up dcdc converter with coupled inductor and switched-capacitor techniques," IEEE Trans. Ind. Electron., vol. 59, no. 2, pp. 998–1007, Feb. 2012.

- [9] R. J. Wai, C. Y. Lin, and C. C. Chu, "High step-up dc–dc converter for fuel cell generation system," in Proc. 30th Annu. Conf. IEEE Ind. Electron. Soc., 2004, pp. 57–62.

- [10] L. Hong-Chen and L. Fei, "Novel high step-up dc-dc converter with active coupled-inductor network for a sustainable

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

energy system," IEEE Trans. Power Electron., vol. 30, no. 12, pp. 6476–6482, Dec. 2015.

- [11] T. Dumrongkittigule, V. Tarateeraseth, and W. Khan-ngern, "A new integrated inductor with balanced switching technique for common mode EMI reduction in high step-up dc/dc converter," in Proc. 17th Int. Zurich Symp. Electromagn.Compat., Singapore, 2006, pp. 541–544.

- [12] K. B. Park, G. W. Moon, and M. J. Youn, "Nonisolated high step-up boost converter integrated with sepic converter," IEEE Trans. Power Electron., vol. 25, no. 9, pp. 6476–6482, Sep. 2010.

- [13] F. Z. Peng, F. Zhang, and Z. Qian, "A magnetic-less dc–dc converter for dual voltage automotive systems," IEE Trans. Ind. Appl., vol. 39, no. 2, pp. 511–518, Mar./Apr. 2003.

- [14] B. Axelrod, Y. Berkovich, and A. Ioinovici, "Switched-capacitor/switched inductor structures for getting transformerless hybrid dc–dc PWM converters," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 55, no. 2, pp. 687–696, Mar. 2008.

- [15] E. H. Ismail, M. A. Al-Saffar, A. J. Sabzali, and A. A. Fardoun, "A family of single-switch PWM converters with high step-up conversion ratio," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 55, no. 4, pp. 1159–1171, May 2008.

- [16] A. A. Fardoun and H.I. Esam, "Ultra step-up dc-dc converter with reduced switch stress", IEEE Trans. Ind. Appl., vol. 46, no. 5, pp. 2025–2034, Sep./Oct. 2010.

- [17] T. Nouri, E. Babaei, and S. H. Hosseini, "A generalized ultra step-up dc/dc converter for high voltage application with design considerations," Elect. Power Syst. Res., vol. 105, pp. 71–84, 2013.

- [18] C. M. Stein, J. R. Pinheiro, and H. L. Hey, "A ZCT auxiliary commutation circuit for interleaved boost converters operating in critical conduction mode," IEEE Trans. Power Electron., vol. 17, no. 6, pp. 954–962, Nov. 2002.

- [19] W. Li and X. He, "An interleaved winding-coupled boost converter with passive lossless clamp circuits," IEEE Trans. Power Electron., vol. 22, no. 4, pp. 1499–1507, Jul. 2007.

- [20] T. Nouri, S. H. Hosseini, E. Babaei, and J. Ebrahimi, "Interleaved high step-up dc/dc converter based on three-winding high-frequency coupled inductor and voltage multiplier cell," IET Power Electron., vol. 8, no. 2, pp. 175–189, 2015,

- [21] L. S. Yang, T. J. Liang, and J. F. Chen, "Transformerless DC–DC converters with high step-up voltage gain," IEEE Trans. Ind. Electron., vol. 56, no. 8, pp. 3144–3152, Aug. 2009.

- [22] E. Babaei, M. E. SeyedMahmoodieh, and H. MashinchiMaheri, "Operational modes and output voltage ripple analysis and design considerations of buck-boost dc-dc converters," IEEE Trans. Ind. Electron., vol. 59, no. 1, pp. 381–391, Jan. 2012.

- [23] E. Babaei and M. E. SeyedMahmoodieh, "Calculation of output voltage ripple and design considerations of SEPIC converter," IEEE Trans. Ind. Electron., vol. 61, no. 3, pp. 1213–1222, Mar. 2014.