A Peer Revieved Open Access International Journal

www.ijiemr.org

#### **COPY RIGHT**

2018IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 27<sup>h</sup> Nov 2018. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-07&issue=ISSUE-12

Title: DESIGN AN EFFICIENT ENERGY AND HIGH SPEED MULTIPLIER IN DSP BASED ON A ROUNDING METHOD

Volume 07, Issue 12, Pages: 424-438.

**Paper Authors**

#### SINGLE SREENIVASA KUMAR, S.SATYANARAYANA

SIR C.V. RAMAN Institute of Technology & Science, AP, India

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic

Bar Code

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

# DESIGN AN EFFICIENT ENERGY AND HIGH SPEED MULTIPLIER IN DSP BASED ON A ROUNDING METHOD

SINGLE SREENIVASA KUMAR<sup>1</sup>, S.SATYANARAYANA<sup>2</sup>

<sup>1</sup>PG Scholar, Dept of ECE, SIR C.V. RAMAN Institute of Technology & Science, AP, India <sup>2</sup> Assistant Professor, Dept of ECE, SIR C.V. RAMAN Institute of Technology & Science, AP, India

ABSTRACT:In this paper, we propose a surmised multiplier that is fast yet vitality effective. The approach is to round the operands to the closest example of two. Along these lines the computational concentrated piece of the duplication is overlooked enhancing velocity and vitality utilization at the cost of a little mistake. The proposed approach is appropriate to both marked and unsigned duplications. We propose three equipment executions of the inexact multiplier that incorporates one for the unsigned and two for the marked tasks. The proficiency of the proposed multiplier is assessed by contrasting its execution and those of some inexact and exact multipliers utilizing diverse plan parameters. Also, the viability of the proposed inexact multiplier is considered in two picture handling applications, i.e., picture honing and smoothing. For expansion In the convolution procedure of the FIR Filter RoBA multiplier is utilized.

#### INTRODUCTION

Vitality minimization is one of the primary necessities in any frameworks, particularly the compact ones, for example, advanced cells, tablets, distinctive devices [1]. exceedingly wanted to accomplish this minimization with insignificant execution (speed) punishment [1]. Computerized flag handling (DSP) squares are key segments of these versatile gadgets acknowledging different sight and sound applications. The computational center of these squares is the number juggling rationale unit where augmentations have the best offer among every single numbercrunching activity performed in these DSP frameworks [2]. Consequently, enhancing the speed and power/vitality proficiency qualities of multipliers assumes a key part enhancing the productivity processors. A large number of the DSP centers actualize picture and video handling calculations where last yields are either pictures or recordings arranged for human utilizations. This reality empowers us to utilize approximations for enhancing the speed/vitality productivity. This starts from the constrained perceptual capacities of individuals in watching a picture or a video. Notwithstanding the picture and video handling applications, there are different zones where the precision of the number-crunching tasks isn't basic to the usefulness of the framework (see [3], [4]). Having the capacity to utilize the surmised figuring furnishes the architect with the capacity of making tradeoffs between the exactness and the speed and additionally utilization [2]. control/vitality Applying the estimation to the math units can be performed at various outline deliberation levels including circuit, rationale, and design levels, and in addition calculation and programming layers [2]. The guess might be performed utilizing distinctive systems, for example, permitting some planning infringement (e.g., voltage over scaling or over timing) and capacity estimation techniques (e.g.,

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

altering the Boolean capacity of a circuit) or a blend of them [4], [5]. In the class of various capacity guess techniques, approximating number juggling building squares, for example, adders multipliers, at various outline levels have been proposed (see [6]–[8]). In this paper, we center around proposing a rapid low power/vitality yet inexact multiplier proper for mistake flexible DSP applications. The proposed estimated multiplier, which is additionally region proficient, is developed by adjusting the ordinary duplication approach at the calculation level expecting adjusted info esteems. We call this adjusting based inexact (RoBA) multiplier. The proposed duplication approach is relevant to both marked and unsigned increases for which three enhanced structures are exhibited. The efficiencies of these structures are surveyed by contrasting the postponements, power and vitality utilizations, vitality defer items (EDPs), and regions with those of some surmised and precise (correct) multipliers. The commitments of this paper can be abridged as takes after: 1) exhibiting another plan for RoBA increase by adjusting the ordinary augmentation approach; 2) portraying three equipment designs of the proposed inexact duplication conspire for sign and unsigned tasks.

# **BACKGROUND AND MOTIVATION** 3.1Basics of Multiplier:

Increase is a scientific task that at its most straightforward is an abridged procedure of adding a whole number to itself a predetermined number of times. A number (multiplicand) is added to itself various circumstances as indicated by another number (multiplier) to shape an outcome (item). In primary school,

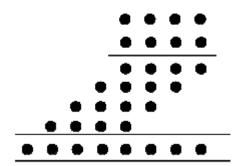

understudies figure out how to duplicate by putting the multiplicand over the multiplier. The multiplicand is then increased by every digit of the multiplier starting with the furthest right, Least Significant Digit (LSD). Middle outcomes (halfway items) are put one on the other, balance by one digit to adjust digits of a similar weight. The last item is controlled by summation of all the incomplete items. Albeit a great many people consider augmentation just in base 10, this system applies similarly to any base, including twofold. Figure 1.1 demonstrates the information stream for the essential duplication strategy simply depicted. Each dark speck speaks to a solitary digit.

Figure 3.1: basic Multiplication

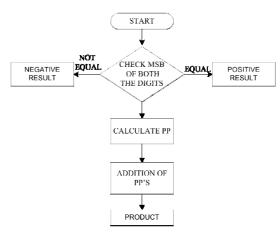

Here, we assume that MSB represent the sign of the digit. The operation of multiplication is rather simple in digital electronics. It has its origin from the classical algorithm for the product of two binary numbers. This algorithm uses addition and shift left operations to calculate the product of two numbers. Based upon the above procedure, we can deduce an algorithm for any kind of multiplication which is shown in figure 3.2. We can check at the initial stage also that whether the product will be positive or negative or after getting the whole result, MSB of the results tells the sign of the product.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

Figure 3.2 Signed Multiplication Algorithm

#### 3.2 Binary Multiplication

In the parallel number framework the digits, called bits, are restricted to the set [0, 1]. The consequence of increasing any twofold number by a solitary paired piece is either 0, or the first number. This makes framing the middle of the road fractional straightforward and effective. Summing these incomplete items is the tedious assignment for double multipliers. One coherent approach is to shape the halfway items each one in turn and entirety them as they are created. Frequently executed by programming on processors that don't have an equipment multiplier, this method works fine, however is moderate on the grounds that no less than one machine cycle is required to whole each extra halfway item. For applications where this approach does not give enough execution, multipliers can be actualized straightforwardly in equipment. The two fundamental classes of double duplication incorporate marked and unsigned numbers. Digit augmentation is a progression of bit movements and arrangement increments, where the two numbers, the multiplicand and the multiplier consolidated into the outcome. Considering the bit portrayal of the

multiplicand x = xn-1....x1 x0 and the multiplier y = yn-1....y1y0 keeping in mind the end goal to shape the item up to n moved duplicates of the multiplicand are to be included for unsigned increase. The whole procedure comprises of three stages, halfway item age, incomplete item lessening and last expansion.

#### 3.3 Multiplication Process

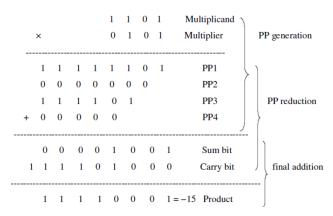

The simplest multiplication operation is to directly calculate the product of two numbers by hand. This procedure can be divided into three steps: partial product generation, partial product reduction and the final addition. To further specify the operation process, let us calculate the product of 2 two's complement numbers, for example,  $1101_2$  ( $-3_{10}$ ) and  $0101_2$  ( $5_{10}$ ), when computing the product by hand, which can be described according to figure 1.3.

|      |   |   |   |   |   |   | 0 |         | Multiplicand |

|------|---|---|---|---|---|---|---|---------|--------------|

|      |   |   | × | _ |   |   | 0 | 1       | Multiplier   |

|      | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1       | PP1          |

|      | 0 | 0 | 0 | 0 | 0 | 0 | 0 |         | PP2          |

|      | 1 | 1 | 1 | 1 | 0 | 1 |   |         | PP3          |

| +    |   | 0 | 0 | 0 | 0 | 0 |   |         | PP4          |

| <br> |   |   |   |   |   |   |   |         |              |

| 1    | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 = -15 | Product      |

Fig 3.3 Multiplication calculations by hand

The striking italic digits are the sign expansion bits of the incomplete items. The main operand is known as the multiplicand and the second the multiplier. The transitional items are called halfway items and the last outcome is known as the item. Be that as it may, the increase procedure, when this technique is straightforwardly mapped to equipment, is appeared in figure 3.2. As can been found in the figures, the augmentation activity in equipment comprises of PP age, PP diminishment and last expansion steps.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

The two columns previously the item are called whole and convey bits. The task of this strategy is to take one of the multiplier bits at any given moment from ideal to left, duplicating the multiplicand by the single piece of the multiplier and moving the halfway item one position to one side of the prior middle of the road items.

Every one of the bits of the incomplete items in every segment are added to get two bits: whole and convey. At last, the aggregate and convey bits in every section must be summed. Likewise, for the duplication of a n-bit multiplicand and a m-bit multiplier, an item with n + m bits long and m incomplete items can be created. The technique appeared in figure 3.3 is additionally called a non-Booth encoding plan.

Fig 3.4: Multiplication Operation in hardware

# **3.4 Importance of Approximate Multiplier.**

A portion of the past works in the field of rough multipliers are quickly checked on. In an inexact multiplier and an estimated viper in light of a method named brokencluster multiplier (BAM) were proposed. By applying the BAM estimate technique for to the ordinary changed Booth multiplier, an inexact marked Booth multiplier was exhibited in The surmised

multiplier gave control utilization investment funds from 28% to 58.6% and region decreases from 19.7% to 41.8% for various word lengths in correlation with a standard Booth multiplier proposed a rough multiplier comprising of various 2 × 2 off base building hinders that spared the power by 31.8% – 45.4% over an exact multiplier. An inexact marked 32-bit multiplier for hypothesis purposes in pipelined processors was composed in It was 20% speedier than a full-snake based tree multiplier while having a likelihood of mistake of around 14%. In a blunder tolerant multiplier, which figured the estimated come about by separating the duplication into one precise and one inexact part, was presented, in which the exactnesses for various piece widths were accounted for. On account of a 12-bit multiplier, a power sparing of over half was accounted for. In two estimated 4:2 blowers for using in a general Dadda multiplier were composed and dissected.

The utilization of rough multipliers in picture preparing applications, prompts decreases in control utilization, postponement, and transistor contrasted and those of a correct multiplier configuration, has been talked about in the writing. In a precision configurable multiplier design (ACMA) was proposed for blunder flexible frameworks. To build its throughput, the ACMA made utilization of a method called convey in forecast that worked in view of a Precomputation rationale. At the point when contrasted and the correct one, the proposed rough duplication brought about almost half lessening in the inertness by decreasing the basic way. Displayed a surmised Wallace tree multiplier (AWTM). Once more, it conjured the convey in expectation to

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

decrease the basic way. In this work, AWTM was utilized as a part of an ongoing benchmark picture application appearing around 40% and diminishments in the power and region, separately, with no picture misfortune contrasted and the instance of utilizing an exact Wallace tree multiplier (WTM) structure. In inexact unsigned augmentation and division in view of a rough logarithm of the operands have been proposed. In the proposed duplication, the summation of the surmised logarithms decides the aftereffect of the activity. Consequently, the augmentation improved to some move and includes tasks. In a strategy for expanding the exactness of the increase approach of was proposed. It depended on the deterioration of the info operands. This technique significantly enhanced the normal mistake at the cost of expanding the equipment of the inexact multiplier by around two times. In a dynamic fragment technique (DSM) is displayed, which plays out the increase activity on a m-bit portion beginning from the main one piece of the info operands. A dynamic range fair multiplier (DRUM) multiplier, which chooses a m-bit section beginning from the main one piece of the information operands and sets the minimum noteworthy piece of the truncated qualities to one, has been proposed. In this structure, the truncated qualities are increased and moved to left to create the last yield. In an inexact 4 ×4 WTM has been recommended that uses an off base 4:2 counter. Furthermore, a mistake adjustment unit for redressing the yields has been proposed. To develop bigger multipliers, this 4 × 4 mistaken Wallace multiplier can be utilized as a part of a cluster structure.

The majority of the beforehand proposed estimated multipliers depend on either changing the structure or multifaceted nature diminishment of a particular precise multiplier. In this like we propose playing out the surmised augmentation through disentangling the task. The contrast between our work and is that, despite the fact that the standards in the two works are relatively comparative for unsigned numbers. the mean mistake of our proposed approach is littler. Furthermore, we recommend some estimation systems when the augmentation is performed for marked numbers.

#### PROPOSED SYSTEM

## 4.1 Introduction to Approximate multiplier.

We are at the limit of a blast in new information, created not just by vast, great logical and business PCs, yet in addition by the billions of low-control gadgets of different sorts. While conventional workloads including value-based and database preparing keep on growing unassumingly, there is a blast in the computational impression of a scope of uses that intend to extricate profound knowledge from huge amounts organized and unstructured information. There is a precision suggested by conventional figuring that isn't required in the handling of most sorts of these information. However today, these intellectual applications keep on being executed on universally useful quickening agent) stages that are exceedingly exact and outlined with unwavering quality starting from the earliest stage. Rough figuring expects to unwind these imperatives objective of acquiring huge picks up in computational throughput - while as yet

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

keeping up a satisfactory nature of results. An essential objective of research in rough registering is to figure out what degrees of approximations in the few layers of the framework stack (from calculations down to circuits and semi-conductor gadgets) are achievable so that the delivered comes about are adequate, yet conceivably not quite the same as those got utilizing exact calculation. Rough figuring methods examined by different specialists have concentrated essentially on improving one layer of the framework stack and have demonstrated advantages in power or execution time. In this work we set out to examine if consolidating numerous estimate strategies spreading over in excess of one layer of the framework stack intensified the advantages, and if these advantages aggravated are broadly material crosswise various over application areas. With a specific end goal to give a solid exhibition, we concentrated on three estimate classes: calculations, guess of number juggling calculations themselves, and estimate of correspondence between computational components. As delegates of every classification we assessed circle aperture, lessened math exactness, and unwinding of synchronization. We chose applications that are computationally costly however can possibly essentially affect our lives in the event that they ended up modest and inescapable. Our applications spread over the spaces of computerized flag handling, apply autonomy, and machine learning. Over the arrangement of utilizations examined, our outcomes demonstrate that we could puncture hot circles in the contemplated applications by a normal of half, with relative decrease in by and large execution time, while as yet delivering

satisfactory nature of results. Moreover, we could decrease the width of the information utilized as a part of the calculation to 10-16 bits from the as of now normal 32 or even 64 bits, with potential for noteworthy execution and vitality benefits. In the parallel applications we considered, we could lessen execution time by half through incomplete disposal of synchronization overheads.

t last, our outcomes likewise show that the advantages from these systems are aggravated when connected simultaneously. That is, joined wisely, the various methods don't essentially diminish the viability of each other. As the advantages of rough registering are not confined to a little class of uses these outcomes spur a reconsidering of the broadly useful processor design to locally bolster various types of guess to more readily understand the possibility to surmised figuring.

# **4.2** Multiplication Algorithm of RoBA Multiplier.

The main idea behind the proposed approximate multiplier is to make use of the ease of operation when the numbers are two to the power n (2n). To elaborate on the operation of the approximate multiplier, first, let us denote the rounded numbers of the input of A and B by Ar and Br, respectively. The multiplication of A by B may be rewritten as

$$A \times B = (Ar - A) \times (Br - B) + Ar \times B +$$

$$Br \times A - Ar \times Br \dots (1)$$

The key observation is that the multiplications of  $Ar \times Br$ ,  $Ar \times B$ , and  $Br \times A$  may be implemented just by the shift operation. The hardware implementation of  $(Ar - A) \times (Br - B)$ , however, is rather complex. The weight of this term in the

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

final result, which depends on differences of the exact numbers from their rounded ones, is typically small. Hence, we propose to omit this part from (1), helping simplify the multiplication operation. Hence, to perform the multiplication process, the following expression is used:

$$A \times B \sim = Ar \times B + Br \times A - Ar \times Br \dots (2)$$

one can perform multiplication operation using three shift and two addition/subtraction operations. In this approach, the nearest values for A and B in the form of 2n should be determined. When the value of A (or B) is equal to the  $3 \times 2p-2$  (where p is an arbitrary positive integer larger than one), it has two nearest values in the form of 2n with equal absolute differences that are 2p and 2p-1. While both values lead to the same effect on the accuracy of the proposed multiplier, selecting the larger one (except for the case of p = 2) leads to a smaller hardware implementation for determining nearest rounded value, and hence, it is considered in this paper. It originates from the fact that the numbers in the form of  $3 \times$ 2p-2 are considered as do not care in both rounding up and down simplifying the process, and smaller logic expressions may be achieved if they are used in the rounding up

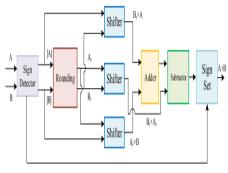

Fig. 4.1. Block diagram for the hardware implementation of the proposed multiplier

The main special case is for three, which for this situation, two is considered as its closest incentive in the proposed rough multiplier. It ought to be noticed that in spite of the past work where the estimated result is littler than the correct outcome, the last outcome ascertained by the RoBA multiplier might be either bigger or littler than the correct outcome relying upon the sizes of Ar and Br contrasted and those of An and B, separately. Note that in the event that one of the operands (say An) is littler than its relating adjusted esteem while the other operand (say B) is bigger than its comparing adjusted esteem, at that point the estimated result will be bigger than the correct outcome. This is because of the way that, for this situation, the increase aftereffect of  $(Ar - A) \times (Br - B)$ will be negative. Since the contrast somewhere in the range of (1) and (2) is correctly this item, the rough outcome winds up bigger than the correct one. Correspondingly, if both An and B are bigger or both are littler than Ar and Br, at that point the inexact outcome will be littler than the correct outcome.

At last, it ought to be noticed the benefit of the proposed RoBA multiplier exists just for positive data sources on the grounds that in the two's supplement portrayal, the adjusted estimations negative of information sources are not as 2n. Thus, recommend before that, augmentation activity begins, the supreme estimations of the two sources of info and the yield indication of the increase result in view of the information sources signs be resolved and after that the task be performed for unsigned numbers and, at the last stage, the best possible sign be connected to the unsigned outcome. The

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

equipment usage of the proposed estimated multiplier is clarified straightaway.

# 4.3 Hardware Implementation of RoBA Multiplier

In view of (2), we give the square graph to the equipment usage of the proposed multiplier in Fig. 4.1 where the sources of info are spoken to in two's supplement arrange. To start with, the indications of the data sources resolved, and for each negative esteem, the outright esteem is created. Next, the adjusting square concentrates the closest incentive for every total an incentive as 2n. It ought to be noticed that the bit width of the yield of this square is n (the most noteworthy piece of the supreme estimation of a n-bit number in the two's supplement arrange is zero). To discover the closest estimation of info A, we utilize the accompanying condition to decide each yield bit of the adjusting square:

$$A_{r}[n-1] = \overline{A[n-1]} \cdot A[n-2] \cdot A[n-3] + A[n-1] \cdot \overline{A[n-2]}$$

$$+ A[n-1] \cdot \overline{A[n-2]}$$

$$A_{r}[n-2] = (\overline{A[n-2]} \cdot A[n-3] \cdot A[n-4] + A[n-2] \cdot \overline{A[n-3]}) \cdot \overline{A[n-1]}$$

$$\vdots$$

$$A_{r}[i] = (\overline{A[i]} \cdot A[i-1] \cdot A[i-2] + A[i] \cdot \overline{A[i-1]}) \cdot \prod_{i=i+1}^{n-1} \overline{A[i]}$$

$$\vdots$$

$$A_{r}[3] = (\overline{A[3]} \cdot A[2] \cdot A[1] + A[3] \cdot \overline{A[2]}) \cdot \prod_{i=4}^{n-1} \overline{A[i]}$$

$$A_{r}[2] = A[2] \cdot \overline{A[1]} \cdot \prod_{i=3}^{n-1} \overline{A[i]}$$

$$A_{r}[1] = A[1] \cdot \prod_{i=2}^{n-1} \overline{A[i]}$$

$$A_{r}[0] = A[0] \cdot \prod_{i=1}^{n-1} \overline{A[i]}.$$

(3)

In the proposed condition, Ar[i] is one out of two cases. In the primary case, A[i] is every last one the bits on its left side are zero while A[i-1] is zero. In the second case, when A[i] and all its left-side bits are zero, A[i-1] and A[i-2] are both

one. Having decided the adjusting esteems, utilizing three barrel shifter hinders, the items Ar  $\times$  Br, Ar  $\times$  B, and Br  $\times$  An are ascertained. Consequently, the measure of moving is resolved in light of  $\log Ar 2 - 1$ (or logBr 2 - 1) on account of An (or B) operand. Here, the info bit width of the shifter squares is n, while their yields are 2n. A solitary 2n-bit Kogge-Stone viper is utilized to ascertain the summation of Ar × B and Br  $\times$  A. The yield of this viper and the consequence of Ar × Br are the contributions of the subtractor hinder whose yield is the total estimation of the yield of the proposed multiplier. Since Ar and Br are as 2n, the contributions of the subtractor may take one of the three info designs appeared in Table I. The relating yield designs are additionally appeared in Table I. The types of the data sources and yield propelled us to consider straightforward circuit in light of the accompanying articulation:

OUT=(P XOR Z) AND ({(P 1) XOR (P XOR Z)} or {(P AND Z) <<1}).....(4)

| Input 1 $(A_r \times B + B_r \times A)$ | Input 2 $(A_r \times B_r)$ | Output   |

|-----------------------------------------|----------------------------|----------|

| 00011xxx                                | 00010000                   | 00001xxx |

| 00011xxx                                | 00001000                   | 00010xxx |

| 00010xxx                                | 00001000                   | 00001xxx |

where P is  $Ar \times B + Br \times An$  and Z is  $Ar \times Br$ . The comparing circuit for actualizing this articulation is littler and speedier than the regular subtraction circuit. At last, if the indication of the last augmentation result ought to be negative, the yield of the subtractor will be refuted in the sign set square. To nullify values, which have the two's supplement portrayal, the comparing circuit in light of

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

X<sup>-</sup> +1 ought to be utilized. To expand the speed of invalidation activity, one may avoid the incrementation procedure in the refuting stage by tolerating its related mistake. As will be seen later, the centrality of the blunder diminishes as the info widths increments. In this paper, if the refutation is performed precisely (around), the usage is called marked RoBA (S-RoBA) multiplier surmised S-RoBA (AS-RoBA) multiplier. For the situation where the sources of info are constantly positive, to build the speed and lessen the power utilization, the sign finder and sign set squares are overlooked from the design, giving us the engineering called unsigned RoBA (U-RoBA) multiplier. For this situation, the yield width of the adjusting square is n + 1 where this bit is resolved in view of  $Ar[n] = A[n-1] \cdot A[n-2]$ . This is on account of on account of unsigned 11x ... x (where x signifies couldn't care less) with the bit width of n, its adjusting esteem is 10...0 with the bit width of n + 1. Subsequently, the information bit width of the shifters is n + 1. In any case, in light of the fact that the most extreme measure of moving is n - 1, 2n is considered for the yield bit width of the shifters.

#### 4.4 Accuracy of RoBA Multiplier.

In this section, inaccuracies of the three architectures discussed above are considered. The inaccuracies of the U-RoBA multiplier and S-RoBA multiplier, which originate from omitting the term (Ar -A)× (Br -B) from the accurate multiplication of A × B, are the same. Hence, the error is

$$\operatorname{error}(A, B) = \frac{(A_r - A)(B_r - B)}{AB}.$$

Assuming Ar and Br are equal to 2n and 2m, respectively, the maximum error

occurs when A and B are equal to  $3 \times 2n$  and  $3 \times 2m$ , respectively. In this case, both Ar and Br have the maximum arithmetic difference from their corresponding inputs. Thus

$$\max\{\text{error}(A,B)\} = \frac{(2^n - 3 \times 2^{n-2})(2^m - 3 \times 2^{m-2})}{(3 \times 2^{n-2}) \times (3 \times 2^{m-2})} = \frac{1}{9}.$$

.....(6)

Therefore, the maximum error for these two architectures is %11.1<sup>-</sup>, which is the same as that of [12].

Fig. 4.2. Numbers (top numbers) and their corresponding possible round values.

In the case of the AS-RoBA multiplier, the error includes an additional term due to the approximate negation (approximate negation). Therefore, in the worst case (where both inputs are negative), one may obtain the maximum error from

$$\operatorname{error}(A,B) = \frac{(\bar{A}_r - \bar{A})(\bar{B}_r - \bar{B})}{AB} + \frac{\bar{A} + \bar{B} + 1}{AB}.$$

...(7)

Compared with (5), the second term comes from the negation approximation obtained from the following relation:

$$A \times B = (A^{-}+1)(B^{-}+1) = A^{-} + B^{-} + 1 + A^{-} \times B^{-} \approx A^{-} \times B^{-}.....(8)$$

which demonstrates the mistake as A<sup>-</sup> + B<sup>-</sup> +1. Thus, for the situation where no less than one of the sources of info is negative, the AS-RoBA multiplier blunder is bigger than that of the two other RoBA multiplier composes. Likewise, when both of the data sources are negative, in spite of the fact that the last outcome will be sure, regardless one needs to refute the negative information sources. In light of this detailing, when one of the sources of info

(5)

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

is −1, the greatest blunder, which is 100%, happens. To diminish the most extreme mistake of this case, one may utilize an indicator to distinguish the situation when one of the information sources is −1, and sidestep the augmentation procedure and create the yield by nullifying the other information. Plainly this arrangement has some postponement and power utilization overhead.

Notwithstanding the greatest mistake, the event rate of the most extreme blunder condition (which we will just call the greatest mistake rate) is acquired as the proportion of the quantity of most extreme blunder events to the aggregate number of yields. This blunder rate is another precision estimation parameter. Here, all the info blends are accepted to happen. On account of n-bit U-RoBA multiplier, there are n - 1 cases for each information where the adjusted esteem has the greatest contrast to the genuine number (see Fig. 2). The greatest blunder happens when these numbers are the info operands. This compares to (n-1)2 cases. On account of S-RoBA multiplier, for every operand, there are 2(n-2) situations where the adjusted operand has the most extreme blunder. Consequently, like the U-RoBA multiplier, the most extreme mistake happens when both of the adjusted operands have the greatest blunder that makes the quantity of greatest blunder event equivalent to (2(n-2))2. At last, on account of the AS-RoBA multiplier, as said previously, the most extreme blunder happens when one of the data sources is -1. Henceforth, the quantity of most extreme mistake events is equivalent to 2  $\times 2n-1-1 (2n-1)$ .

Table II demonstrates the most extreme mistake rates for the three RoBA

multiplier structures for the info bit width of 8-, 16-, 24-, and 32-bit multipliers. As the outcomes appear, the rate of the greatest blunder diminishes as the bit length increments. Additionally, among the models, the AS-RoBA multiplier has the most extreme blunder rate.

Then again, in the instances of the U-RoBA and S-RoBA multipliers when the supreme estimation of the info operand of

# TABLE II MAXIMUM ERROR RATES (%) FOR THE ROBA MULTIPLIER ARCHITECTURES

| Input bit width →  | 8        | 16      | 24      | 32      |

|--------------------|----------|---------|---------|---------|

| U-RoBA multiplier  | 7.40e-04 | 5.2e-06 | 1.8e-12 | 5.2e-15 |

| S-RoBA multiplier  | 0.21     | 1.8e-05 | 6.8e-12 | 1.9e-14 |

| AS-RoBA multiplier | 0.39     | 1.5e-03 | 5.9e-06 | 2.3e-08 |

# TABLE III PASS RATES (%) FOR THE RoBA MULTIPLIER ARCHITECTURES

| Input bit width →  | 8    | 16      | 24       | 32        |

|--------------------|------|---------|----------|-----------|

| U-RoBA multiplier  | 6.9  | 0.050   | 2.98e-6  | 1.5e-6    |

| S-RoBA multiplier  | 12.1 | 0.097   | 5.72e-4  | 2.98e-6   |

| AS-RoBA multiplier | 3.02 | > 0.024 | > 1.4e-4 | > 7.45e-7 |

# TABLE IV MRE, MED, NMED, MSE, ACCinf, VARIANCE, AND ERROR RATE OF DIFFERENT 32-bit APPROXIMATE MULTIPLIER DESIGNS

|               | MRE   | MED     | NMED   | MSE     | $ACC_{inf}$ | Variance | Error<br>rate |

|---------------|-------|---------|--------|---------|-------------|----------|---------------|

| U-RoBA        | 2.92% | 1.3E+17 | 0.0069 | 4.8E+34 | 60.0%       | 6.0E-04  | ~1            |

| S-RoBA        | 2.91% | 3.2E+16 | 0.0017 | 3.0E+33 | 58.0%       | 6.0E-04  | ~1            |

| AS-RoBA       | 2.93% | 3.2E+16 | 0.0017 | 3.0E+33 | 58.0%       | 6.0E-04  | ~1            |

| Mitchell [12] | 3.86% | 1.7E+17 | 0.0093 | 7.7E+34 | 58.8%       | 1.2E-06  | ~1            |

| DSM8 [16]     | 0.53% | 2.2E+16 | 0.0012 | 1.0E+33 | 60.8%       | 5.6E-06  | ~1            |

| DRUM6 [17]    | 1.47% | 6.3E+16 | 0.0034 | 1.0E+34 | 60.0%       | 1.1E-04  | ~1            |

| HAAM [18]     | 2.04% | 3.8E+17 | 0.0188 | 4.5E+35 | 85.8%       | 1.0E-03  | 0.29          |

the multiplier is as the 2m, the yield aftereffect of the RoBA multiplier is

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

correct [see (5)]. Thus, the quantities of right yields in the instances of the U-RoBA multiplier and S-RoBA multipliers are 2(n+1)2n-(n+1)2 and n2n+2-4n2, individually. On account of the AS-RoBA multiplier, when the two sources of info are certain, the multiplier acts like the other two RoBA multiplier structures, and thus, when one of the data sources is as 2m, the yield is correct. Moreover, there are some different mixes that prompt the right yield. One case of such cases is (A - $AR) (B^{-} - B^{-} R) + A = 1$ . Scientifically discovering every one of the blends with amend (correct) yield is amazingly troublesome, and henceforth, for the AS-RoBA multiplier, we utilize the lower bound of the right yield number that is equivalent to n2n - n2.

Next, the passing rates, characterized as the proportion of the quantity of right yield events to the aggregate number of particular yields [19], for the proposed multiplier models are given in Table III. As the outcomes appear, by expanding the bit width, the rate of right outcomes is decreased. Contrasted and the most extreme blunder, be that as it may, the rate at which the right outcomes are created (i.e., the passing rate) is higher. As could be normal, the AS-RoBA multiplier has the least pass rate, while the pass rate of the S-RoBA multiplier is bigger than the others. It ought to be noticed that the pass rate of the technique proposed in [12] is the same as that of the U-RoBA multiplier. Table IV demonstrates mean relative blunder (MRE), mean mistake remove (MED), standardized MED (NMED) [21], mean square blunder (MSE), ACCinf (which the measures blunder noteworthiness the Hamming separation) [19], change, and mistake rate

of various estimated multiplier plans. For extricating these measurements, 100K info blends of information sources were chosen from a uniform dispersion. Here, we think about the precision of the proposed multipliers with DSM8 (DSM with a portion size of 8) [16], DRUM6 (DRUM with a fragment size of 6) [17], the strategy proposed in [12] (signified by Mitchell), and the surmised multiplier proposed in [18] (indicated by HAAM). Note that, DSM8, DRUM6, Mitchell, and HAAM all are unsigned multipliers.

# TABLE V PERCENTAGES OF THE OUTPUTS WITH RE SMALLER THAN A SPECIFIC VALUE FOR DIFFERENT 32-bit APPROXIMATE MULTIPLIER DESIGNS

|               | RE<0.5% | RE<1% | RE<2%  | RE<4%  | RE<6%  | RE<8%  | RE<10% | RE<12% |

|---------------|---------|-------|--------|--------|--------|--------|--------|--------|

| U-RoBA        | 18.1%   | 29.9% | 47.5%  | 71.0%  | 85.8%  | 94.8%  | 99.3%  | 100.0% |

| S-RoBA        | 18.1%   | 30.0% | 47.7%  | 71.0%  | 86.0%  | 94.9%  | 99.4%  | 100.0% |

| AS-RoBA       | 17.9%   | 30.0% | 47.7%  | 71.3%  | 86.1%  | 95.0%  | 99.4%  | 100.0% |

| DSM8 [16]     | 47.2%   | 97.6% | 100.0% | 100.0% | 100.0% | 100.0% | 100.0% | 100.0% |

| DRUM6 [17]    | 21.1%   | 40.3% | 70.8%  | 98.3%  | 100.0% | 100.0% | 100.0% | 100.0% |

| HAAM [18]     | 70.4%   | 70.4% | 70.5%  | 72.0%  | 72.0%  | 100.0% | 100.0% | 100.0% |

| Mitchell [12] | 12.1%   | 20.9% | 35.3%  | 57.4%  | 74.6%  | 88.1%  | 97.5%  | 100.0% |

As Table IV appears, with the exception of the mistake rate and ACCinf, the DSM8 gives the most elevated precision regarding all the blunder measurements. The base blunder rate has a place with the HAAM design, while the base an incentive for ACCinf is for (A)S-RoBA. Likewise, the qualities for U-RoBA, DSM8, and DRUM6 are relatively equivalent. It ought to be noticed that the precision of the U-RoBA multiplier is somewhat littler than that of the (A)S-RoBA multiplier. This is because of the littler scope of the marked numbers

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

contrasted and that of the unsigned numbers for a similar piece width. Moreover, despite the fact that the precision of the U-RoBA is littler than those of the DSM8 and DRUM6, its postponement and vitality esteems are lower. At last, the rates of the yields with the relative mistake (RE) littler than a particular incentive for the 32-bit surmised multiplier plans are appeared in Table V. They demonstrate that the best (the following best) exactness has a place with DSM8 (DTUM6) whose the greater part of its yields have REs littler than 2% (6%). In the instances of the proposed multipliers in this paper, the majority of the rough yields have RE esteems littler than 10%.

#### Extension.

# Implementation of the proposed RoBA multiplier in FIR Filter.

#### FIR FILTER.

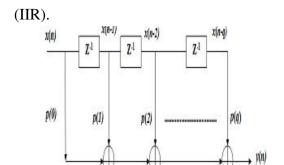

A channel is a gadget or process that expels some undesirable segment or highlight from a flag. Separating is a class of flag preparing, the characterizing highlight of channel being the total or fractional concealment of some part of the flag. There are two fundamental sorts of channel, simple and advanced. Channels can be arranged in a few distinct gatherings, contingent upon what criteria are utilized for grouping. The two noteworthy kinds of advanced channels are limited drive reaction computerized channels (FIR channels) and endless motivation reaction computerized channels

Fig 4.3. Finite Impulse

#### Response Filter Realization

FIR channels are one of the essential kinds of channels utilized as a part of Digital Signal Processing. FIR channels are said to be limited since they don't have any criticism. In this manner, on the off chance that we send a drive through the framework (a solitary spike) at that point the yield will perpetually wind up zero when the motivation goes through the channel. A non-recursive channel has no input. The Finite Impulse Response Filter Realization is as appeared in figure 4.3.

**IMPULSE** Limited reaction (FIR) advanced channel is generally utilized as a part of a few computerized flag handling applications, for example, discourse preparing, boisterous speaker leveling, reverberate wiping out, versatile clamor retraction, and different correspondence applications, including programming characterized radio (SDR) et cetera. A large number of these applications require FIR channels of huge request to meet the stringent recurrence particulars. All the time these channels need to help high inspecting rate for rapid advanced correspondence. The quantity duplications and augmentations required for each channel yield, be that as it may, increments straightly with the channel arrange. Since there is no repetitive calculation accessible in the FIR channel

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

calculation, continuous execution of a substantial request FIR channel in an asset obliged condition is a testing errand. Channel coefficients all the time stay steady and known apiarian flag handling applications. Limited Impulse Response (FIR) channels are broadly utilized as a part of advanced flag preparing. A N-tap FIR channel is characterized by the accompanying information yield condition 1

out(n) =

$$\sum_{i=0}^{N-1} x(n-i) h(i)$$

Where  $\{h (i): i = 0... N-1\}$  are the filter coefficients.

A FIR channel executes a convolution task [1], which is regularly based on the supposition of endless length signals. Limited length signals (e.g. pictures) then again, have discontinuities at the limits. In this manner develops the issue of which esteems to use at these districts. An ordinarily prescribed arrangement is to broaden each column by reflection at the flag edges. The quantity of additional examples presented at the flag limits is equivalent to N-1. They can be parceled unequally between the left and the correct side flag. We will allude by  $\alpha$  and  $\mu$ to the quantity of tests presented individually at the left side and the correct side info flag  $(\alpha + \mu = N-1)$ . In the convolution procedure of the FIR Filter RoBA multiplier is utilized.

#### CONCLUSION

In this paper, we proposed a highspeed yet energy efficient approximate multiplier called RoBA multiplier. The proposed multiplier, which had high accuracy, was based on rounding of the inputs in the form of 2n. In this way, the computational intensive part of the multiplication was omitted improving speed and energy consumption at the price of a small error. The proposed approach was applicable to both signed and unsigned multiplications. Three hardware implementations of the approximate multiplier including one for the unsigned and two for the signed operations were discussed. The efficiencies of the proposed multipliers were evaluated by comparing them with those of some accurate and approximate multipliers using different design parameters. The results revealed that, in most (all) cases, the RoBA multiplier architectures outperformed the corresponding approximate (exact) multipliers. Also, the efficacy of the proposed approximate multiplication approach was studied in two image processing applications of sharpening and smoothing. The comparison revealed the same image qualities as those of exact multiplication algorithms.

#### REFERENCES

[1] M. Alioto, "Ultra-low power VLSI circuit design demystified and explained: A tutorial," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 59, no. 1, pp. 3–29, Jan. 2012.

[2] V. Gupta, D. Mohapatra, A. Raghunathan, and K. Roy, "Low-power digital signal processing using approximate adders," IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., vol. 32, no. 1, pp. 124–137, Jan. 2013.

[3] H. R. Mahdiani, A. Ahmadi, S. M. Fakhraie, and C. Lucas, "Bio-inspired imprecise computational blocks for efficient VLSI implementation of soft-computing applications," IEEE Trans.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

- Circuits Syst. I, Reg. Papers, vol. 57, no. 4, pp. 850–862, Apr. 2010.

- [4] R. Venkatesan, A. Agarwal, K. Roy, and A. Raghunathan, "MACACO: Modeling and analysis of circuits for approximate computing," in Proc. Int. Conf. Comput.-Aided Design, Nov. 2011, pp. 667–673.

- [5] F. Farshchi, M. S. Abrishami, and S. M. Fakhraie, "New approximate multiplier for low power digital signal processing," in Proc. 17th Int. Symp. Comput. Archit. Digit. Syst. (CADS), Oct. 2013, pp. 25–30.

- [6] P. Kulkarni, P. Gupta, and M. Ercegovac, "Trading accuracy for power with an underdesigned multiplier architecture," in Proc. 24th Int. Conf. VLSI Design, Jan. 2011, pp. 346–351.

- [7] D. R. Kelly, B. J. Phillips, and S. Al-Sarawi, "Approximate signed binary integer multipliers for arithmetic data value speculation," in Proc. Conf. Design Archit. Signal Image Process., 2009, pp. 97–104.

- [8] K. Y. Kyaw, W. L. Goh, and K. S. Yeo, "Low-power high-speed multiplier for error-tolerant application," in Proc. IEEE Int. Conf. Electron Devices Solid-State Circuits (EDSSC), Dec. 2010, pp. 1–4.

- [9] A. Momeni, J. Han, P. Montuschi, and F. Lombardi, "Design and analysis of approximate compressors for multiplication," IEEE Trans. Comput., vol. 64, no. 4, pp. 984–994, Apr. 2015.

- [10] K. Bhardwaj and P. S. Mane, "ACMA: Accuracy-configurable multiplier architecture for error-resilient system-on-chip," in Proc. 8th Int. Workshop Reconfigurable Commun.-Centric Syst.-Chip, 2013, pp. 1–6.

- [11] K. Bhardwaj, P. S. Mane, and J. Henkel, "Power- and area-efficient approximate wallace tree multiplier for error-resilient systems," in Proc. 15th Int. Symp. Quality Electron. Design (ISQED), 2014, pp. 263–269.

- [12] J. N. Mitchell, "Computer multiplication and division using binary logarithms," IRE Trans. Electron. Comput., vol. EC-11, no. 4, pp. 512–517, Aug. 1962.

- [13] V. Mahalingam and N. Ranganathan, "Improving accuracy in Mitchell's logarithmic multiplication using operand decomposition," IEEE Trans. Comput., vol. 55, no. 12, pp. 1523–1535, Dec. 2006.

- [14] Nangate 45nm Open Cell Library, accessed on 2010. [Online]. Available: <a href="http://www.nangate.com/">http://www.nangate.com/</a>

- [15] H. R. Myler and A. R. Weeks, The Pocket Handbook of Image Processing Algorithms in C. Englewood Cliffs, NJ, USA: Prentice-Hall, 2009.

- [16] S. Narayanamoorthy, H. A. Moghaddam, Z. Liu, T. Park, and N. S. Kim, "Energy-efficient approximate multiplication for digital signal processing and classification applications," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 23, no. 6, pp. 1180–1184, Jun. 2015.

- [17] S. Hashemi, R. I. Bahar, and S. Reda, "DRUM: A dynamic range unbiased multiplier for approximate applications," in Proc. IEEE/ACM Int. Conf. Comput.-Aided Design (ICCAD), Austin, TX, USA, 2015, pp. 418–425.

- [18] C.-H. Lin and I.-C. Lin, "High accuracy approximate multiplier with error correction," in Proc. 31st Int. Conf. Comput. Design (ICCD), 2013, pp. 33–38.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

[19] A. B. Kahng and S. Kang, "Accuracy-configurable adder for approximate arithmetic designs," in Proc. 49th Design Autom. Conf. (DAC), Jun. 2012, pp. 820–825.

[20] Z. Wang, A. C. Bovik, H. R. Sheikh, and E. P. Simoncelli, "Image quality assessment: From error visibility to structural similarity," IEEE Trans. Image Process., vol. 13, no. 4, pp. 600–612, Apr. 2004.

[21] J. Liang, J. Han, and F. Lombardi, "New metrics for the reliability of approximate and probabilistic adders," IEEE Trans. Comput., vol. 62, no. 9, pp. 1760–1771, Sep. 2013.