A Peer Revieved Open Access International Journal

www.ijiemr.org

### **COPY RIGHT**

2018IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 27<sup>h</sup> Nov 2018. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-07&issue=ISSUE-12

Title: SYNTHESIS OF LOW POWER HIGH PERFORMANCE MIXED -LOGIC LINE DECODERS

Volume 07, Issue 12, Pages: 395-403.

**Paper Authors**

JINKA GURUNATHA BABU, M.AMARANATH REDDY

SIR C.V. RAMAN Institute of Technology & Science, AP, India

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic

Bar Code

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

## SYNTHESIS OF LOW POWER HIGH PERFORMANCE MIXED -LOGIC LINE DECODERS

JINKA GURUNATHA BABU<sup>1</sup>, M.AMARANATH REDDY <sup>2</sup>

<sup>1</sup>PG Scholar, Dept of ECE, SIR C.V. RAMAN Institute of Technology & Science, AP, India <sup>2</sup> Assistant Professor, Dept of ECE, SIR C.V. RAMAN Institute of Technology & Science, AP, India

**ABSTRACT:** This task presents a blended rationale plan technique for line decoders, joining transmission door rationale, pass transistor double esteem rationale and static CMOS. Two tale topologies are exhibited for the 2-4 decoder: a 14-transistor topology pointing on limiting transistor tally and power dispersal and a 15-transistor topology pointing on high power-defer execution. Both an ordinary and an altering decoder are executed for each situation, yielding an aggregate of four new plans. Besides, four new 4-16 decoders are planned, by utilizing blended rationale 2-4 predecoders joined with standard CMOS post-decoder. All proposed decoders have full swinging ability and lessened transistor tally contrasted with their ordinary CMOS partners.

#### 1 INTRODUCTION

Power administration has turned into a noteworthy issue in the advancement of a computerized framework particularly, in the convenient gadgets in which improvement of the battery life time and decreasing the charging time are turning into a testing issues step by step. The significant issue is control scattering. Innovation prompts Increase spillage current, which prompts increment in sub edge spillage current. It is foremost that these high computational capacities are set in a lowpower, versatile condition. Thus, a very much organized low vitality plan system must be set up. As the thickness of the coordinated circuits and size of the chips and frameworks sustain to develop, it turns out to be increasingly burdensome to give sufficient cooling to the frameworks.

In mix to warm reflection, there are monetary and ecological issues for low power advancement. In the Amalgamated States, PC hardware represents around 2-3%

of aggregate power utilization. This figure is relied upon to increase as there is huge increment in family unit PC applications, Web telephones, handheld PCs, and interior These financial and natural terminals. reasons have constrained the essential for vitality effective PCs. With the end goal to meet the injunctive approval in high computational applications, the clock rate is consistently augmenting and clock skew being an inexorably fundamental piece of the clock cycle. The vitality devoured by low-skew clock dispersion systems is neverendingly developing. Clock-related power utilization can achieve more than 30-40% of the aggregate intensity of microchip and is turning into an all the more cosmically massive division of the chip strength. In mix, the quantity of rationale entryway delays in a clock period is diminished by 25% per age. Accordingly, idleness of flip tumbles or locks is turning into an all the more cosmically colossal part of the process

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

duration.Static CMOS circuits are utilized for by far most of rationale entryways in incorporated circuit. They comprise of integral nMOS pulldown pMOS pullup systems and present great execution and also protection from commotion and gadget variety. In this manner, CMOS rationale is portrayed by power against voltage scaling and transistor measuring and in this manner solid activity at low voltages and little transistor sizes. Information signals are associated with transistor entryways just, offering lessened plan intricacy assistance of cellbased rationale combination and structure. Pass-transistor rationale was predominantly created during the 1990s, when different plan styles were presented, expecting to give a feasible option in contrast to CMOS rationale and enhance speed, power and territory. Its primary plan contrast is that inputs are connected to both the entryways and the source/deplete dissemination terminals of transistors. Pass transistor circuits are with executed either individual nMOS/pMOS pass transistors or parallel nMOS pMOS of and transmission doors. This work builds up a blended rationale plan technique for line decoders, joining entryways of various rationale to a similar circuit, with an end to acquire enhanced execution contrasted with single-style structure. Line decoders are basic circuits, generally utilized in the fringe hardware of memory exhibits (e.g. SRAM), multiplexing structures, usage of Boolean rationale capacities and different applications. Regardless of their significance, a generally little measure of

writing is devoted to their advancement, with some ongoing work including.

### 2 Overview Of Line Decoder Circuits

In advanced frameworks, discrete amounts of data are spoken to by parallel codes. A n-bit paired code can speak to up to 2n unmistakable components of coded information. A decoder is a combinational circuit that changes over paired data from n input lines to a greatest of 2n one of a kind yield lines or less, if the n-bit coded data has unused mixes. The circuits inspected in this work are called n-to-m line decoders, and their motivation is to produce the m = 2n minterms of n input factors.

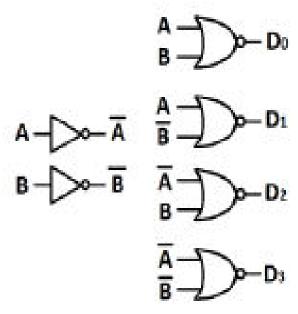

### 2-4 Line Decoder

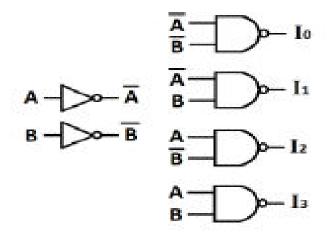

A 2-4 line decoder creates the 4 minterms D0-3 of 2 input factors An and B. Its rationale activity is condensed in Table I. Contingent upon the info mix; one of the 4 yields is chosen and set to 1 while the others are set to 0. An altering 2-4 decoder produces the corresponding minterms I0-3, hence the chosen yield is set to 0 and the rest are set to 1, as appeared in Table II.

**Table 1: Truth Table of 2-4 Decoder**

| A | В | $D_0$ | $\mathbf{D}_1$ | $D_2$ | $D_3$ |

|---|---|-------|----------------|-------|-------|

| 0 | 0 | 1     | 0              | 0     | 0     |

| 0 | 1 | 0     | 1              | 0     | 0     |

| 1 | 0 | 0     | 0              | 1     | 0     |

| 1 | 1 | 0     | 0              | 0     | 1     |

Table 2: Truth Table of Inv. 2-4 Decoder

Vol 07 Issue12, Nov 2018

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

| Α | В | $I_0$ | $I_1$ | $I_2$ | $I_3$ |

|---|---|-------|-------|-------|-------|

| 0 | 0 | 0     | 1     | 1     | 1     |

| 0 | 1 | 1     | 0     | 1     | 1     |

| 1 | 0 | 1     | 1     | 0     | 1     |

| 1 | 1 | 1     | 1     | 1     | 0     |

In traditional CMOS plan, NAND and NOR doors are liked to and additionally, since they can be actualized with 4 transistors, rather than 6, along these lines executing capacities rationale with effectiveness. A 2-4 decoder can be actualized with 20 transistors utilizing 2 inverters and 4 NOR entryways, as appeared in Fig. 1(a). The comparing modifying decoder can likewise actualized with 20 transistors utilizing 2 inverters and 4 NAND entryways, as appeared in Fig. 1(b).

Fig1 : 2-4 Non Inverting NOR-Based Decoder

Fig 2: 2-4 Inverting NAND-Based Decoder

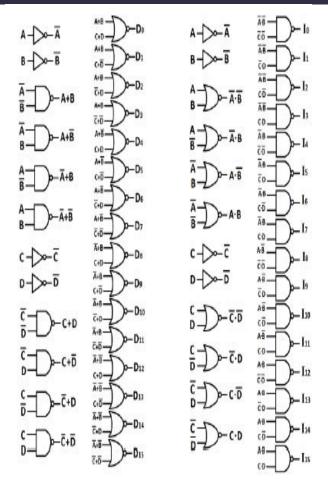

# 3.1.1 4-16 Line Decoder with 2-4 Predecoders

A 4-16 line decoder produces the 16 minterms D0-15 of 4 input factors A, B, C and D, and a transforming 4-16 line decoder creates the correlative minterms I0-15. A direct execution of these circuits would require 16 4-input NOR and NAND entryways. In any case, a more effective structure can be gotten utilizing predecoding method, as indicated by which squares of n address bits can be predecoded into 1-of-2n predecoded lines that fill in as contributions to the last stage decoder. With this strategy, a 4-16 decoder can be executed with 2-4 reversing decoders and 16 2-input NOR doors and a modifying one can be actualized with 2-4 decoders and 16 2-input NAND entryways. In CMOS rationale, these structures require 8 inverters and 24 4-input doors, yielding an aggregate of 104 transistors each.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

Fig 3:104Transistor 4-16 Line Decoders Implemented With CMOS Logic and Predecoding

## 3 New Mixed-Logic Designs

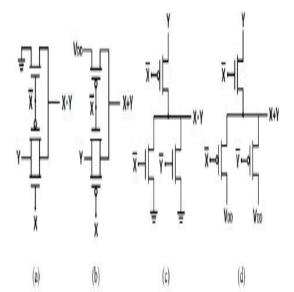

In combinational rationale, transmission entryways have generally been utilized in XOR-based circuits, for example, full adders and as the essential switch component in multiplexers. Be that as it may, we consider their utilization in the usage of AND/OR rationale, as showed in, which can be productively connected in line decoders.

The 2-input TGL AND/OR doors are appeared in Figs. They are full-swinging, yet not reestablishing for all information blends. With respect to transistor rationale, there are two principle circuit styles: those that

utilization nMOS just pass-transistor circuits, as CPL and those that utilization both nMOS and pMOS pass transistors, as DPL and DVL. The style we consider in this work is DVL, which offers an enhancement for DPL, safeguarding its full swing activity with lessened transistor tally. The 2-input DVL AND/OR doors are appeared in Figs. Like the TGL doors, they are full-swinging however non-reestablishing.

Fig4: TGL AND gate Fig 4.1(b) TGL OR gate Fig4.1(c) DVL AND gate Fig4.1(d): DVL OR gate

Accepting that reciprocal information sources are accessible, the TGL/DVL doors require just 3 transistors, rather than the 4 required in CMOS NAND/NOR entryways. Decoders are high fan out circuits, where couple of inverters can be utilized by various entryways, in this manner utilizing the TGL/DVL doors can result to decreased transistor check. An imperative regular normal for these doors is their uneven nature, i.e the way that they don't have adjusted info loads. As appeared in Fig.4.1, we named the 2 entryway inputs X and Y.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

In TGL doors, input X controls the entryway terminals of every one of the 3 transistors, while input Y engenders to the yield hub through the transmission door. In DVL entryways, input X controls 2 transistor door terminals, while input Y controls 1 door terminal and engenders through a pass transistor to the yield. We will allude to X and Y contributions as the control flag and the engender flag of the entryway, separately. This hilter kilter highlight gives an originator the adaptability to perform flag game plan, I. e picking which input is utilized as control and which as engender motion in each entryway. Having a reciprocal contribution as spread flag is anything but a decent practice, since the inverter added to the engendering way builds delay altogether. Along these lines, while actualizing the restraint (A'B) or suggestion (A'+B) work, it is more proficient to pick the reversed variable as control flag. While actualizing the AND (AB) OR (A+B) work, either decision is similarly effective. At last, while actualizing the NAND (A'+B') or NOR (A'B') work, either decision results to a correlative spread flag, perforce.

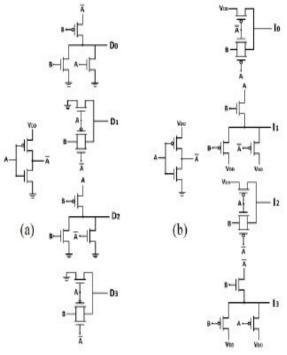

# 4 The 14-transistor 2-4 Low-Power Topology

Planning a 2-4 line decoder with either TGL or DVL doors would require an aggregate of 16 transistors (12 for AND/OR entryways and 4 for inverters). In any case, by blending both AND entryway types into a similar topology and utilizing legitimate flag game plan, it is conceivable to dispose of one of the two inverters, along these lines lessening the aggregate transistor tally to 14. Give us a chance to accept that, out of the two

information sources, in particular An and B, we mean to dispose of the B inverter from the circuit. The Do minterm (A'B') is actualized with a DVL entryway, where An is utilized as spread flag. The D1 minterm (AB') is executed with a TGL door, where B is utilized as engender flag. The D2 minterm (A'B) is executed with a DVL entryway, where An is utilized as proliferate flag. At long last, The D3 minterm (AB) is executed with a TGL entryway, where B is utilized as spread flag. These specific decisions totally away the utilization of the turn corresponding B flag, consequently the B inverter can be wiped out from the circuit bringing about a 14-transistor topology (9 nMOS, 5 pMOS). Following a comparative technique with OR doors, a 2-4 rearranging line decoder can be executed with 14 transistors (5 nMOS, 9 pMOS), also: I0, I2 are actualized with TGL (utilizing B as spread flag) and I1, I3 are executed with DVL (utilizing An as engender flag). The B inverter can indeed be omitted. The inverter disposal decreases transistor tally, intelligent exertion and generally exchanging action of the circuits, in this way limiting force dissemination. To the extent the creators are concerned, 14 is the base number of transistors required to understand a fullswinging 2-4 line decoder with static (non timed) rationale. The two new topologies are named '2-4LP' and '2-4LPI', where 'LP' remains for 'low power' and 'I' 'transforming'. Their schematics appeared in Fig. 4.2(a) and Fig. 4.2(b), individually.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

Fig 5: New 14-transistor 2-4 line decoders: (a) 2-4LPI

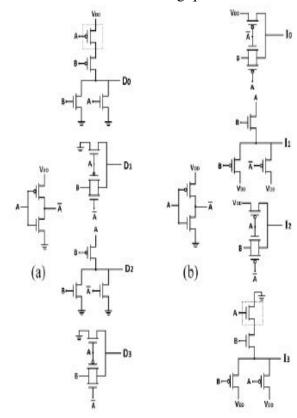

## 5 THE 15-TRANSISTOR 2-4 HIGH-PERFORMANCE TOPOLOGY

The low-control topologies introduced above have a disadvantage with respect to most pessimistic scenario delay, which originates from the utilization of integral An as the proliferate motion on account of D0 and I3. In any case, acknowledging D0 and I3 can be executed all the more productively by utilizing standard CMOS entryways, since there is no requirement for reciprocal signs. In particular, D0 can not be actualized with a CMOS NOR door and I3 with a CMOS NAND entryway, adding one transistor to every topology. The new structures coming about because of this alteration blend 3 unique sorts of rationale into a similar circuit and present a noteworthy enhancement in postponement while just somewhat expanding force dispersal. They are named '2-4HP' (9 nMOS, 6 pMOS) and '2-4HPI' (6 nMOS, 9 pMOS), where 'HP' remains for 'elite' and 'I' for 'reversing'. The thinking behind the 'HP' assignment is that these decoders present both low power and low defer qualities, thusly accomplishing a general decent execution.

The 2-4HP and 2-4HPI schematics are appeared in Fig. 4.3(a) and Fig. 4.3(b), separately, where the extra transistors are featured for less demanding qualification.

Fig 6: New 15-transistor 2-4 line decoders: (a) 2-4HP (b) 2-4HPI.

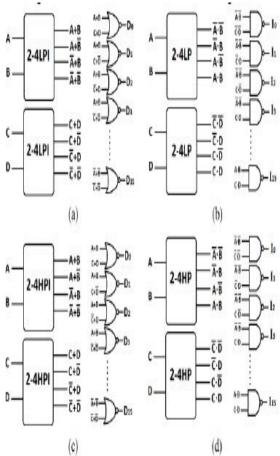

# 6 INTEGRATION IN 4-16 LINE DECODERS

At a little scale, circuits dependent on pass transistor rationale can understand rationale capacities with less transistors and enhanced execution contrasted with static CMOS. In any case, falling a few non-reestablishing circuits causes a quick corruption in convey ideal outcomes, consolidating the positive

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

describes of both. Receiving this structure procedure, and regarding the hypothesis introduced on area II, we actualized four 4-16 decoders by utilizing the four new 2-4 as predecoders related to CMOS NOR/NAND entryways to create the decoded yields. The new topologies got from this mix are: 4-16LP (Fig.a), which joins two 2-4LPI predecoders with a NOR-based postdecoder, 4-16HP ( Fig.b which ), consolidates two 2-4HPI predecoders with a NOR-based post-decoder, 4-16LPI (Fig.c), which consolidates two 2-4LP predecoders with a NAND-based post decoder and, at long last, 4-16HPI (Fig.d), which joins two 2-4HP predecoders with a NAND-based post-decoder.

Fig 7: New 4-16 line decoders: (a) 4-16LP, (b) 4-16LPI, (c) 4-16HP, (d) 4-16HPI.

### 7 RESULTS AND ANALYSIS

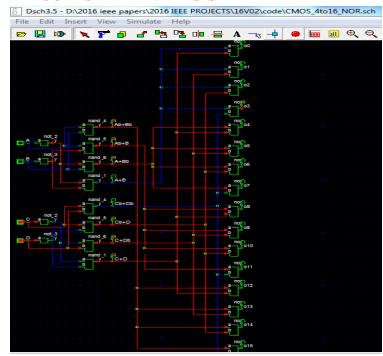

Fig 8: Schem9atic of 4to16 Decoder Using CMOS

Click on the input buttons to set them to 1 or 0. Red color in a switch indicates a '1'. As shown in above.

### **8 CONCLUSION**

This paper presented a proficient blended rationale structure for decoder circuits, joining TGL, DVL and static CMOS. By utilizing this procedure, we created four new 2-4 line decoder topologies, specifically 2-4LP, 2-4LPI, 2-4HP and 2-4HPI, which offer lessened transistor check (in this way conceivably littler design region) and enhanced power-defer execution in connection to traditional CMOS decoders.

### 9 FUTURE SCOPE

Besides, four new 4-16 line decoder topologies were introduced, in particular 4-16LP, 4-16LPI, 4-16HP and 4-16HPI, acknowledged by utilizing the blended rationale 2-4 decoders as predecoding

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

circuits and joining them with post-decoders actualized in static CMOS rationale. These plans join the enhanced execution attributes of pass transistor rationale with the reestablishing capacity of static CMOS An assortment of similar zest recreations was performed at the 32 nm, checking, as a rule, a clear preferred standpoint for the proposed plans. The 2-4LP and 4-16LPI topologies are generally reasonable for applications where territory and power minimization is of essential concern. The 2-4LPI, 2-4HP and 2-4HPI, and additionally the comparing 4-16 topologies (4-16LP, 4-16HPI, 4-16HP), ended up being practical and all-around proficient plans, along these lines they can adequately be utilized as building hinders in of the structure bigger decoders, and other combinational multiplexers circuits of differing execution necessities. In addition, the exhibited lessened transistor tally and low power attributes can profit both mass CMOS and SOI configuration also. The acquired circuits are to be executed on format level, making them appropriate for standard cell libraries and RTL structure.

### REFERENCES

- [1] N. H. E. Weste and D. M. Harris, "CMOS VLSI Design, a Circuits and Systems Perspective," 4<sup>th</sup> ed., 2011: Addison-Wesley.

- [2] R. Zimmermann and W. Fichtner, "Low-Power Logic Styles: CMOS Versus Pass-Transistor Logic", *IEEE Journal of Solid State Circuits*, vol. 32, no. 7, pp.1079 -1090, 1997.

- [3] K. Yano, et al., "A 3.8-ns CMOS 16x16-b multiplier using complementary pass-transistor logic," *IEEE J. Solid-State Circuits*, vol. 25, pp.388 393,1990.

- [4] M. Suzuki, et al., "A 1.5ns 32b CMOS ALU in double pass-transistor logic," *Proc. 1993 IEEE Int. Solid-State Circuits Conf.*, pp.90 -91 1993.

- [5] X. Wu, "Theory of transmission switches and its application to design of CMOS digital circuits," *International J. Circuit Theory and Application*, vol. 20, no. 4, pp.349 -356, 1992.

- [6] V. G. Oklobdzija and B. Duchene, "Pass-transistor dual value logic for low-power CMOS," *Proc. of the Int. Symp. on VLSI Technology*, pp.341 -344 1995.

- [7] M. A. Turi and J.G. Delgado-Frias, "Decreasing energy consumption in address decoders by means of selective precharge schemes," *Microelectronics Journal*, vol. 40, no. 11, pp.1590-1600, 2009.

- [8] V. Bhatnagar, A. Chandani and S. Pandey, "Optimization of row decoder for 128×128 6T SRAMs," 2015 International Conference on VLSI Systems, Architecture, Technology and Applications (VLSI-SATA), pp. 1-4. IEEE, 2015.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

- [9] A. K. Mishra, D. P. Acharya and P. K. Patra, "Novel design technique of address Decoder for SRAM," 2014

International Conference on Advanced Communication

Control and Computing Technologies (ICACCCT), pp. 1032-1035, IEEE, 2014.

- [10] D. Mar ovi, B. Ni oli and V.. O lobd i a, "A general method in synthesis of pass-transistor circuits," *Microelectronics Journal*, vol 31, pp. 991-998,2000.

- [11] Available at: http://ptm.asu.edu/

[12] N. Lotze and Y. Manoli, "A 62

mV 0.13 µm CMOS StandardCell- Based Design Technique

Using Schmitt-Trigger Logic,"

IEEE Journal

ofSolidStateCircuits,vol.47,no.1

,pp.47-60,Jan.2012.