A Peer Revieved Open Access International Journal

www.ijiemr.org

### **COPY RIGHT**

2018IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 12<sup>th</sup> Nov 2018. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-07&issue=ISSUE-12

Title: AN EFFICIENT ARX-BASED CRYPTOGRAPHY USING SCP PROCESSOR

Volume 07, Issue 12, Pages: 109-114.

**Paper Authors**

THUMMALA RAMACHANDRA KAVYASREE, V. THRIMURTHULU

Chadalawada Ramanamma Engineering College, Tirupati, India.

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic

Bar Code

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

### AN EFFICIENT ARX-BASED CRYPTOGRAPHY USING SCP PROCESSOR

<sup>1</sup>THUMMALA RAMACHANDRA KAVYASREE, <sup>2</sup>V. THRIMURTHULU

<sup>1</sup>PG scholar (M.Tech (VLSI-SD)), Dept. of ECE, Chadalawada Ramanamma Engineering College, Tirupati, India.

<sup>2</sup>Professor, Dept. of ECE, Chadalawada Ramanamma Engineering College, Tirupati, India.

thummalakavya@gmail.com<sup>1</sup>, vtmurthy.v@gmail.com<sup>2</sup>

Abstract— This article illustrates SPARX is an ARX-based block cipher. It was published in Asia crypt as one of the instantiations of a family of ARX-based block ciphers with provable security against single-characteristic differential and linear cryptanalysis. ARX-based cryptographic algorithms are composed of only three elemental operations - addition, rotation and exclusive or - which are mixed to ensure adequate confusion and diffusion properties. ARX based cryptography, that intrinsically guarantees SCA resistance of any implemented algorithm. The protecting the complete data path using a Boolean masking scheme with three shares, the sparx is enhancement is we are implement the efficient adder in the module to reduce the area occupation in LUTS.

Index Terms— SPARX, Side Channel Resistance, Boolean Masking, Cryptography, Block Cipher.

#### I. INTRODUCTION

SPARX is a family of ARX-based block ciphers that was published in Asia crypt 2016. It was designed with the goal of putting forward a general strategy for designing ARX-based symmetric-key primitives with provable security against single-characteristic differential and linear cryptanalysis. As a dual to the wide trail strategy adopted by many S-box based block ciphers, the designers proposed the long strategy. This strategy promotes the use of a rather weak but large S-box, an ARX-based S-box, along with a very light linear layer. Fostering the existence of long trails, that involve an uninterrupted sequence of calls to the S-box interleaved with key additions, rather than having maximum diffusion in each linear layer is at the core of this proposed strategy. The long trail strategy allowed the designers to bound the maximum differential and linear probabilities. We are implementing the SPARX processor for protracting the side Chanel attack, so Their main advantage is that they are hard to detect because usually a sidechannel attacker does not interact with the target device. Security plays a major role in many applications of the upcoming Internet of Things (IoT), when security critical digital devices are also potentially exposed to physical attacks, such as sidechannel analysis (SCA) and intentional fault-

injection. In this regard, the security system designer is often faced with two contradictory challenges. On the one hand, he is required to build and integrate a robust cryptographic subsystem that is efficient but resistant against any type of (physical) attack. On the other hand, he must create a lifetime-secure but agile system with included migration paths to allow updates of cryptographic components in the field, if necessary. While the first requirement indicates a implementation hardware that combines computational efficiency and physical protection, the second update criterion demands a software-like implementation. In this context Field- Programmable-Gate-Arrays can be one viable solution for some situations, but in many lightweight contexts they are not applicable for several reasons. Simon is a block cipher currently published through NSA as a lightweight possibility to the substantially-used AES. Simon can be very promising for hardware-primarily based embedded programs as its internal shape is quite easy and bit-orientated. Indeed, its authors show that the ASIC implementation of Simon calls for best 1234 GE (Gate Equivalent) for 128 bits of security, in comparison to 2400 GE for the smallest AES to date. Also, it turned into shown that a piece-serialized FPGA implementation of Simon units a present-day

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

location file with simplest 36 slices for 128 bits of protection, in comparison to 264 same slices for AES (in conjunction with the BRAMs) and 117 slices for Present. However, to truly enforce Simon on practical embedded platforms, protection in opposition to facet-channel evaluation must be taken under consideration. Side-channel evaluation (SCA) can break cryptosystems with the aid of exploiting vulnerabilities inside the realistic implementation of cryptographic schemes.

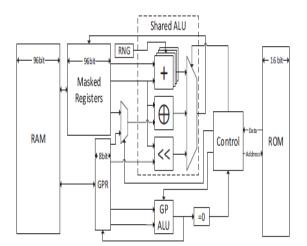

Fig 1: SPARX Structure

SCA harvests the information leaked through variations in the power intake, electromagnetic radiation, or execution time. Typically, the adversary builds an electricity model using a key speculation and compares the result with the actual strength intake until the proper secret is determined. An SCA attack that is established the usage of a single hint is known as Simple Power Analysis (SPA). The proposed system is the processor to protect the data from the side channel attacks with occupying the less area then the existing system.

### II. EXISTING SYSTEM

# A. SCA protected co-processor platform for ARX cipher:

Side-channel attack is a kind of physical attack against cryptographic devices to obtain secret keys stored inside the hardware by analyzing information leakage in power and EM (Electro-Magnetic) waveforms during cryptographic operations. To establish a security evaluation methodology and to

evaluate efficiency of countermeasures against the side-channel attack using common experimental environment, SASEBO (Side-channel Attack Standard Evaluation Board and SAKURA (Side-channel Attack User Reference Architecture) boards were developed.

## B. General - Purpose ALU and ARX-Specific ALU:

The architecture developed the SPARX processor that is protected form side channel attacks, that contains many blocks those are designed for data protection. SPARX incorporate unprotected Arithmetic and logical unit which performs mathematical and logical operations with high performance. This gives all single cycle operations. For controlling cause this auxiliary ALU is used without occupying the primary adders. It also can adequately calculate round constants and different inputs to the cryptographic set of rules. Easily corrupted statistics can't be locked and particularly included via ALU. Unmasked values are loaded and saved in RAM to allow top interplay. This is useful to dynamically choose a cipher set of policies or to generate an "encryption-executed" flag for an outdoor major CPU.

Fig 2: Block diagram of SPARX

It consists of a TI-protected adder, an xor and a rotation unit and is connected to a dedicated register file. Because both, the xor and rotation operations are linear, ensuring that each share is processed independently is sufficient for the masked implementation. However, addition in Z232 is non-

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

linear. The construction of a TI-conform shared representation of the addition is non-trivial. Schneider et al. proposed two different types of addition circuits for Boolean-masked values which follow the TI principle. For our purpose, we use a similar variant of their proposal based on the ripple-carry adder as it is far more area-efficient for lightweight application than their presented Kogge - Stone adder, while only requiring four bits of fresh randomness per operation. The fourfold pipelined architecture is based on a RISC approach hand incorporates two separate ALUs. The side-channel protected ALU performs all elementary ARX operations on a protected register file with direct access to a source of randomness that is required for the addition operation. We further identified that a dedicated unprotected ALU, which operates on a dedicated register file, is beneficial to increase the overall performance at reasonable costs. Load and store instructions are available for moving data between the RAM and the register files. The adder consumes 32 cycles to complete 32 additions, which indicates that it's far the slowest adder on this layout. To provide high throughput the clock is greater with excessive frequency with the aid of doubling the primary clock. This ends in installation in postpone by using decreasing to sixteen cycles. The retrieve operation doesn't consider about the operation it simply gives the modern nation. This is the most effective one operation which offers statistics that the retrieve operation after each sixteen cycles. This mission is trivial and may without problems be automated due to the fact in each cycle exactly one new guidance is fetched. Parallel addition operations are instanced for excessive through put, which reduces the average quantity of required cycles. Incorporating more than 4 adders offers diminishing returns in overall performance and couldn't be efficiently exploited with the aid of most ARX algorithms.

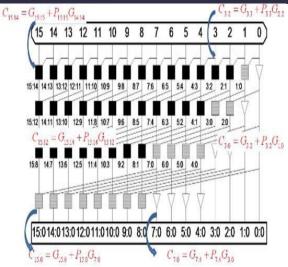

Fig 3: Kogge stone Adder

The main module adder is design like Kogge stone adder is adder implementation is the most straightforward, and it has one of the shortest critical paths of all tree adders. The two different in the way their carry generation block Is implemented. The parallel prefix carry look ahead adder was first proposed some twenty years ago as a means of accelerating n-bit addition in VLSI technology. It widely considered as the fastest adder and used for high performance arithmetic circuits in the industries. A three-step process is generally involved in the construction of a Kogge stone Adder. The first step involves the creation of generate and propagate signals for the input operand bits. The second step involves the generation of carry signals. In the final step, the sum bits of the adder following stages of the operand bits and the preceding stage carry bit using a xor gate. The adders in third are built from generate and propagate (GP) blocks, black cells (BC) blocks, eight grey cell (GC) blocks. The drawback with the Kogge- Stone adder implementation is the large area consumed and the more complex routing (Fan-Out) of interconnects.

#### III.PROPOSED SYSTEM

The proposed design is the reduce the area then the existing system the processor to protect the data from the side channel attacks with occupying the less area then the existing system. In this proposed system the adder architecture will be change that is the spanning tree adder that is occupy the less area then the

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

existing system. This proposed design is a same processor, but one architecture is different. In the previous design ALU used the adder is Kogge stone adder it occupies the more area and time take to the operation is more but in this design, we are using the spanning tree it occupy the less area (in LUTs). Spanning tree, known for having minimal logic depth and fanout. Here we designate BC as the black cell which generates the ordered pair; the grey cell (GC) generates the left signal only, following the interconnect area is known to be high, but for an FPGA with large routing overhead to begin with, this is not as important as in a VLSI implementation. The regularity of the spanning tree prefix network has built in redundancy which has implications for faulttolerant designs. This hybrid design completes the summation process with a 4-bit RCA allowing the carry prefix network to be simplified. This step involves computation of generate and propagate signals corresponding too each pair of bits in A and B.

This step involves computation of carries corresponding to each bit. It uses group propagate and generate as intermediate signals which are given by the logic equations below:

In the adder generate and propagate (GP) blocks, black cells (BC) blocks are very less than the previous system the blocks are constructs the generate and propagate block takes a pair of operand bits (a, b) as inputs. Computes a pair of generate and propagate signals (g, p) as output. Generate (Gi) indicates whether a carry is generated from that bit.

Fig 4: Spanning tree Adder

Propagate (Pi) indicates whether a carry is propagated through that bit. Ai Bi Generate Propagate Block Gi Pi. BC block The black cell takes two pairs of generate and propagate signals (gi, pi) and (gj, pj) as input. computes a pair of generate and propagate signals (g, p) as output.

$$Gi.j = Gi + (Pi . Gj) Pi.j = Pi . Pj .$$

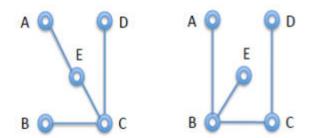

The grey cell takes two pairs of generate and propagate signals (Gi, Pi) and (Gj, Pj) as inputs. Computes a generate signal "G" as output. One simple definition is that a tree is a connected graph with no cycles, where a cycle lets you go from a node to itself without repeating an edge. A spanning tree for a connected graph G is a tree containing all the vertices of G. Below are two examples of spanning trees for our original example graph.

Fig 5: Examples of Spanning trees.

When dealing with a new kind of data structure, it is a good strategy to try to think of as many different characterizations as we can. This is somewhat like the problem of coming up with good representations of the data; different ones may be appropriate for different purposes. Here are some alternative

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

characterizations the class came up with spanning tree adder is the occupy the less area using tree structure the blocks in adder are less than the previous adder, so this adder is give the efficient results then the existing systems. While, to our knowledge, the proposed design is the first side-channel resistant, flexible ARX accelerator. several hardware implementations of ARX ciphers have been introduced in the literature. Compared to previous architecture the proposed architecture gives more security for side channels, i.e.it protects more in side channels. Along with this the data protection can be done for more number of bits and less area.

#### IV. RESULTS

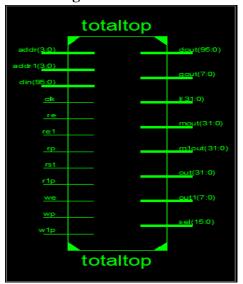

### A. Block Diagram:

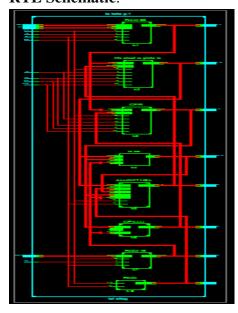

### B. RTL Schematic:

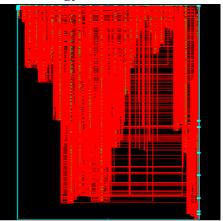

### C. Technology Schematic:

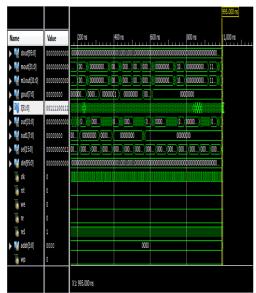

#### D. Simulation:

### E. Comparison Table:

| Parameters   | Existing<br>System | Proposed system |

|--------------|--------------------|-----------------|

| Area (LUTS)  | 996                | 979             |

| Delay (ns)   | 2.198              | 2.198           |

| Power(watts) | 0.177              | 0.522           |

### V. CONCLUSION

In this paper presents a flexible ARX-ASIP processor that essentially protects all implemented algorithms against timing and first-order side-channel attacks. The well-established leakage scheme is applied for practical demonstration of resistance. Block cipher, stream ciphers and hash functions are done at same time and updated by cryptography using proposed multiple ARX algorithms. By changing minimal

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

requirements securely data is adapted. And the change the adder architecture the design is efficient than the previous designs.

#### VI. REFERENCE

- 1. R. Beaulieu, D. Shors, J. Smith, S. Treatman-Clark, B. Weeks, and L. Wingers, "The SIMON and SPECK Families of Lightweight Block Ciphers.," IACR Cryptology ePrint Archive, vol. 2013, p. 404, 2013.

- A. Moradi, A. Poschmann, S. Ling, C. Paar, and H. Wang, "Pushing the Limits: A Very Compact and a Threshold Implementation of AES," in Advances in Cryptology EUROCRYPT 2011 (K. G. Paterson, ed.), vol. 6632 of Springer LNCS, pp. 69–88, 2011.

- 3. A. Aysu, E. Gulcan, and P. Schaumont, "SIMON Says: Break Area Records of Block Ciphers on FPGAs," Embedded Systems Letters, IEEE, vol. 6, pp. 37–40, June 2014.

- 4. T. Good and M. Benaissa, "AES on FPGA from the Fastest to the Smallest," in Cryptographic Hardware and Embedded Systems CHES 2005 (J. Rao and B. Sunar, eds.), vol. 3659 of Springer LNCS, pp. 427–440, 2005.

- 5. P. Yalla and J. Kaps, "Lightweight Cryptography for FPGAs," in International Conference on Reconfigurable Computing and FPGAs, 2009. ReConFig '09., pp. 225–230, Dec 2009.

- 6. S. Bhasin, T. Graba, J.-L. Danger, and Z. Najm, "A look into SIMON from a side channel perspective," in IEEE International Symposium on Hardware-Oriented Security and Trust (HOST), 2014, pp. 56–59, May 2014.

- D. Shanmugam, R. Selvam, and S. Annadurai, "Differential Power Analysis Attack on SIMON and LED Block Ciphers," in Security, Privacy, and Applied Cryptography Engineering (R. Chakraborty, V. Matyas, and P. Schaumont, eds.), vol. 8804 of Springer LNCS, pp. 110– 125, 2014.

- 8. S. Nikova, C. Rechberger, and V. Rijmen, "Threshold Implementations Against Side-

- Channel Attacks and Glitches," in Information and Communications Security (P. Ning, S. Qing, and N. Li, eds.), vol. 4307 of Springer LNCS, pp. 529–545, 2006.

- 9. B. Mazumdar, S. S. Ali, and O. Sinanoglu, "Power analysis attacks on ARX: an application to Salsa20," in *IOLTS*, pp. 40–43, IEEE, 2015.

- 10. N. Veyrat-Charvillon, M. Medwed, S. Kerckhof, and F. Standaert, "Shuffling against side-channel attacks: A comprehensive study with cautionary note," in *ASIACRYPT*, vol. 7658 of *Lecture Notes in Computer Science*, pp. 740–757, Springer, 2012.

- 11. E. Prouff and M. Rivain, "Masking against side channel attacks: A formal security proof," in *EUROCRYPT*, vol. 7881 of *Lecture Notes in Computer Science*, pp. 142–159, Springer, 2013.

- 12. A. Poschmann, A. Moradi, K. Khoo, C. Lim, H. Wang, and S. Ling, "Side-channel resistant crypto for less than 2, 300 GE," *J. Cryptology*, vol. 24, no. 2, pp. 322–345, 2011.