A Peer Revieved Open Access International Journal

www.ijiemr.org

## **COPY RIGHT**

2018IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 28<sup>h</sup> Nov 2018. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-07&issue=ISSUE-12

Title: DESIGN AND IMPLEMENTATION OF HIGH SPEED AND LOW POWER ERSFQ DECODER FOR MEMORIES

Volume 07, Issue 12, Pages: 452-456.

**Paper Authors**

### Y SAHITHI LEELA, SK.BABAFARIDDIN

St. Mary's Women's Engineering College, Budampadu, GUNTUR (Dt); A.P., India.

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic

Bar Code

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

# DESIGN AND IMPLEMENTATION OF HIGH SPEED AND LOW POWER ERSFQ DECODER FOR MEMORIES

<sup>1</sup>Y SAHITHI LEELA, <sup>2</sup>SK.BABAFARIDDIN

<sup>1</sup>M-tech Student Scholar, Department of Electronics and communication Engineering, St. Mary's Women's Engineering College, Budampadu, GUNTUR (Dt); A.P, India.

<sup>2</sup>Assistant Professor, Department of Electronics and communication Engineering, St. Mary's Women's Engineering College, Budampadu, GUNTUR (Dt); A.P, India.

<sup>1</sup>sahithileelayadla3@gmail.com, <sup>2</sup>sbabafariddin@gmail.com

**Abstract**: We have designed and tested at high speed and low power RSFQ-decoder, the critical component of an 8-bit RSFQ processor data path. The memory design is based on an asynchronous wave-pipelined approach scalable for wide datapath processors. We report on the development of energy-efficient decoders for memory and register file. To reduce the pitch, area, and energy, our decoder employs scalable binary tree architecture. We implemented these decoders using ERSFQ logic controlled by magnetically coupled address lines. These lines are driven by energy-efficient drivers based on the current-stirring technique. We experimentally confirmed the functionality of the circuits achieves better performance compared to the previous designs.

Index Terms: energy-efficient logic, random access memory, RSFQ

#### 1. INTRODUCTION

A high-performance arithmetic-logic unit (ALU) is a fundamental building block for any special- or generalpurpose processor. The reported ALU is a key processing component for the RSFQ-based [1] 8-bit processor datapath [2]. This is the first attempt to build a superconductor parallel processor in contrast to the bit-serial approaches [3, 4]. The ALU design is based on Kogge-Stone adder (KSA) [5]. A set of logic operations is integrated into the adder structure. The ALU is switched between arithmetic and logic operations by control signals. A similar approach to build an adder-based ALU was reported in [6]. However, that ALU was based on a simple ripple-carry adder and, therefore, was hardly scalable to a large number of bits. The current ALU employs a wavepipeline synchronization approach [7].

According to this approach, a pipeline stage is allowed to start its operation on two independent data operands as soon as both operands arrive. There is no clock pulse used to advance the computation from one stage to another. Instead, a clock pulse that follows data is used to reset cells in the stage to make it ready to process the data wave. This type synchronization makes it different from the previous RSFQ-based pipeline ripplecarry adder [6] and KSA [8], where a coflow timing technique was used to clock data throughout the entire adder requiring a clock distribution tree for every stage. We have already reported low-frequency functionality test results of the 8-bit ALU in [9]. This paper focuses on high-speed test results. Typically RAM and register file are organized as a memory cell matrix

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

using n-to-2 addressable address decoders, where n is a number of address bits. For the efficient design, the decoder has to be low power and match dimensions (pitch) of that of memory cell rows or columns as close as possible. There are several known decoder design types implemented using superconducting circuits: loop decoders, tree decoders, NOR and NAND decoders [11]-[22]. The first decoder based on energy-efficient ERSFQ logic [1] was described in [23]. This 4-to-16 bit decoder was implemented using Hypres 4- layer process with 4.5 kA/cm2 critical current density, occupied 0.7 x 1.8 mm2 and dissipated ~70 aJ per one address decode operation. In this paper, we present a new ERSFQ decoder based on a binary tree architecture featuring 2 n scaling and with significantly more compact layout enabled by advanced fabrication processes developed at Hypres and at MIT-LL.

#### 2. DESIGN

# **2.1 Decoder with Binary Tree Architecture**

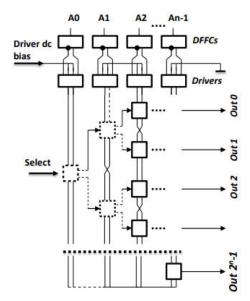

Fig. 1 shows a block diagram of the n-to-2 n bit address decoder with a binary tree architecture. It consists of n address line drivers. In contrast to our previous decoder design with n2 n decoder cells [23], the binary tree architecture requires only 2 n - 1 decoder cells. With energy efficiency being one of the primary goals of this design, the binary tree approach has a significant power scaling advantage (~ factor of n) comparing to the previous matrix design

Fig. 1: Block diagram of the binary tree decoder.

An address line driver [23] comprises an ERSFQ D flip-flop with complementary outputs (DFFC) that generates SFQ control signals for the dc-powered current steering loop driver [22]. For each column of the decoder, two complementary superconductive lines (An andĀn) traverse the entire vertical dimension of the decoder (Fig. 1). Each cell of the decoder cell tree is magnetically coupled to one of the complementary lines. By commutating an and a lines in the proper order, a unique combination of control currents can be achieved to address all 2n outputs. This addressing allows for the select signal to propagate to the appropriate output, thus performing address decoding. Similarly to the earlier demonstrated decoder [23], once the address is set, the decoder settings do not change until another address is applied, allowing this circuit to be used also as a switch.

### 2.2 Decoder Cell

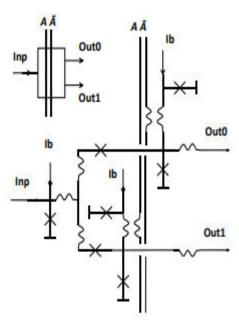

Fig. 2 shows a decoder cell based on SFQ switches controlled by dc currents via magnetic coupling. Each decoder cell (Fig. 2) consists of two dc-current driven SFQ

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

switches. Each switch is magnetically coupled to one of two complementary lines. When the current is present in the line, the switch is in ON position - the incoming SFO pulse can propagate through the switch. On the contrary, the absence magnetically induced current puts the switch in the OFF position, and the SFQ pulse escapes via the buffer junction. Thus, the decoder cell commutates its input to one of two outputs. When the corresponding address bit is "1" (line A is carrying current), the cell sends the input SFQ pulse to its output Out1. And when the address bit is "0" (line A is carrying current), the cell sends the input SFQ pulse to its output Out0.Each decoder output from Out0 to Out2n -1 has a unique combination of true and complement address lines, thus connecting it to the input of the tree.

Fig. 2: Decoder cell symbol and schematics.

The addressing time of the decoder (i.e., time of address setting) is the time to charge/discharge current from control lines, that is estimated as ~100 ps [23]. The select time is the time delay for SFQ

pulse propagating from input to output. For n = 4 and at 10 kA/cm2 process, it can be estimated based on our simulations as 30 ps at nominal bias.

## 2.3 Low-Speed Functionality Test

We have performed functionality testing of the decoder matrix fabricated using MIT-LL process. The fabricated chips were mounted in flip-chip cryoprobe. The chip was measured at 4.2 K temperature with multilayer mu-metal providing necessary magnetic shielding. Evaluation of 4-bit decoder functionality and dc bias current margins measurements were performed with multifunctional test system OCTOPUX [31].

For the ERSFQ circuitry the dc bias is provided by Josephson transmission line through large superconducting inductors. We estimate that FJTL should exceed ~25% of total dc bias current [32]. The decoder with the larger FJTL has already been designed for HYPRES 10 kA/cm2 6layer process with HKI NbN layer. Although, the introduction of the feeding JTL reduced the overall energy-efficiency of the stand-alone decoder by raising the required bias current with ~30% of total bias being drawn by FJTL; it is also resulted in improvement of the operational bias margins. When decoder is integrated into a larger circuit, e. g., into MRAM or register file, the role of FJTL will be taken by other circuits such as a clock distribution network.

## 2.4 High-speed test

In order to perform high-speed test, we employed a similar to one demonstrated in [33], [34] technique. We apply a highspeed select signal from the high-frequency generator, while the address switch was applied at fairly low speed. The output data stream is monitored on toggling-type SFO/dc converters.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

#### 3. SIMULATION RESULTS

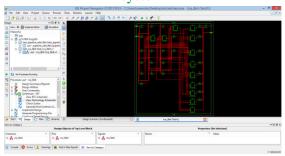

Fig 3: Simulation result for the proposed system

Fig 4: Technology schematic of the proposed system

Fig 5: Summary report of the proposed system

#### 4. CONCLUSION

We have developed new decoder circuits using a scalable binary-tree architecture optimized for perspective register file implemented applications. We two different decoder designs using this architecture. The first design was implemented using HYPRES Integrated Memory Process and optimized to have a small vertical pitch of output decoder rows to match dimensions of the word rows in MRAM. The second design implemented for MIT-LL process and optimized for integration with a register file in a microprocessor. The common objective of both designs was to minimize energy consumption. This was achieved using a spaceefficient current-steering addressing scheme dissipating no power in static regime and requiring relatively small power for the address change. The address decoding is done by the controlled SFQ pulse propagation with power dissipation typical for any ERSFQ circuit. 5.

#### REFERENCES

- [1] D. Kirichenko, S. Sarwana, A. Kirichenko, "Zero static power dissipation biasing of RSFQ circuits," IEEE Trans. Appl. Supercon., vol. 21, pp.776-779, Jun. 2011

- [2] O. A. Mukhanov, "Energy-efficient Single Flux Quantum technology," IEEE Trans. Appl. Supercond., vol. 21, pp.760-769, Jun. 2011.

- [3] Q. Herr, A. Herr, O. Oberg, A. Ioannidis, "Ultra-low-power superconductor logic," J. Appl. Phys., vol. 109, 2011. Art. No. 103903.

- [4] M. A. Manheimer, "Cryogenic Computing Complexity Program: Phase 1 Introduction," IEEE Trans. Appl. Supercond., vol. 25, no. 3, Jun. 2015, Art. No. 13017004.

- [5] D. S. Holmes, A. L. Ripple, M. A. Manheimer, "Energy-efficient superconducting computing power budgets and requirements," IEEE Trans. Appl. Supercond., vol. 23, Jun. 2013, Art. No. 1701610.

- [6] L. Ye, D. B. Gopman, L. Rehm, D. Backes, G. Wolf, T. Ohki et al., "Spintransfer switching of orthogonal spin-valve devices at cryogenic temperatures," J. Appl. Phys., vol. 115, 2014. Art. No. 17C725.

- [7] I. V. Vernik, V. V. Bol'ginov, S. Bakurskiy, A. A. Golubov et al., "Magnetic Josephson junctions with superconducting interlayer for cryogenic

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

memory," IEEE Trans. Appl. Supercond., vol. 23, Jun. 2013, Art. No. 1701208.

[8] B. Niedzielski, S. Diesch, E. Gingrich, Y. Wang, R. Loloee et al., "Use of Pd–Fe and Ni–Fe–Nb as Soft Magnetic Layers in Ferromagnetic Josephson Junctions for Nonvolatile Cryogenic Memory," IEEE Trans. Appl. Supercond., vol. 24, no. 4, Aug. 2014, Art. No. 1800307.

[9] B. Baek, W. Rippard, S. Benz, S. Russek, and P. Dresselhaus, "Hybrid superconducting-magnetic memory device using competing order parameters," Nature Comms., vol. 5, May 2014, Art. No. 3888. [10] A. F. Kirichenko, A. Sahu, T. V. Filippov, O. A. Mukhanov, A. Dotsenko, Dorojevets, A. K. Kasperek, M. "Demonstration of an 8×8-bit RSFQ multiport register file," 2013 IEEE 14th Int. Supercond. Electron. Conf. (ISEC), p. A2, 7-11 July 2013.

[11] W. Henkels and H. Zappe, "An experimental 64 bit decoded Josephson NDRO random access memory array," IEEE J. Solid-State Cir. vol. 13, no. 5, pp. 591-600, Oct. 1978.

[12] S. Nagasawa, Y. Hashimoto, H. Numata, S. Tahara, "A 380 ps, 9.5 mW Josephson 4-Kbit RAM operated at a high bit yield," Applied IEEE Trans. Appl. Supercond. vol. 5, no. 2, pp. 2447-2452, Jun. 1995.

[13] P. F. Yuh, "A 2-kbit superconducting memory chip, IEEE Trans. Appl.

Supercond. vol. 3, no. 2, pp. 3013-3021, Jun. 1993.

[14] T. Van Duzer, L. Zheng, S. Whiteley, H. Kim, J. Kim, et al., "64-kb hybrid Josephson-CMOS 4 Kelvin RAM with 400 ps access time and 12 mW read power," IEEE Trans. Appl. Supercond. vol. 23, no. 3, Jun. 2013, Art.No. 1700504.

#### **Author's Profile:**

Y.SAHITHILEELA received B.Tech St.Mary's degree from Women's Engineering College in the year 2014 and I'm pursuing M.Tech with specialization in VLSI having Roll No:15ND1D5713 at St.Mary's Womens Engineering College, Budampadu, My area of interest in VLSI.

SK.BabaFariddin working as Asst. Professor in the Department of Electronics and Communication Engineering St.Mary's Women's Engineering College, Budampadu..