A Peer Revieved Open Access International Journal

www.ijiemr.org

### **COPY RIGHT**

2018 IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 25<sup>th</sup> Sept 2018. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-7&issue=ISSUE-10

Title: FAULT TOLERANT OF FIFO BUFFERS OF NOC ROUTER

Volume 07, Issue 10, Pages: 114-121.

**Paper Authors**

### GUNTUPALLI LALITHA SINDHURYA, SK. SHAKEELABI

Krishnaveni Engineering College for Women, Kesanupalli.

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic

Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

## FAULT TOLERANT OF FIFO BUFFERS OF NOC ROUTER

GUNTUPALLI LALITHA SINDHURYA<sup>1</sup>,SK.SHAKEELABI<sup>2</sup>

<sup>1</sup>PG Scholar, ECE Department, Krishnaveni Engineering CollegeFor Women, Kesanupalli <sup>2</sup> Associate Professor, ECE Department, Krishnaveni Engineering College ForWomen, Kesanupalli

**Abstract:** This concise proposes an on-line direct test framework for disclosure of idle hard accuses which make in first information first yield backings of switches in the midst of field activity of NoC. The technique incorporates repeating tests discontinuously to hinder gathering of insufficiencies. A model use of the proposed test computation has been consolidated into the switch channel interface and on-line test has been performed with made self-similar data action. The execution of the NoC after extension of the test circuit has been investigated the extent that throughput while the area overhead has been considered by incorporating the test hardware. In like manner, an on-line test technique for the coordinating method of reasoning has been proposed which considers utilizing the header ricochets of the data movement improvement in transporting the test plans.

**Keywords:** FIFO Cushions, In-Field Test, NoC, Changeless Blame, Straightforward Test.

### I. INTRODUCTION

All through the latest decade, compose onchip (NoC) has ascended as a predominant correspondence establishment differentiated and transport based correspondence mastermind complex chip traces vanquishing the inconveniences related to information exchange limit, respectability, and power dispersal [1]. In any case, like each and every other structure on-a-chip (SoCs), NoC-based SoCs ought to similarly be striven for distortions. Testing the segments of the NoC system incorporates testing switches and interrouter joins Significant proportion of zone of the NoC data transport medium is controlled by switches, which is overwhelmingly required by FIFO underpins and coordinating method of reasoning. In like way, the probabilities run-time of distortions occurring in backings and reason through and through higher are differentiated and interchange portions of

the NoC. Along these lines, test plan for the NoC structure must begin with preliminary of supports androuting basis of switches. Likewise, the test must be performed at times to ensure that no fault gets gathered. The coincidental run-time useful issues have been one of the noteworthy stresses in the midst of testing significantly scaled **CMOS**-based memories. These deficiencies are eventual outcome of physical effects, for instance, environmental susceptibility, developing, and low supply voltage and in this manner are unpredictable (nonpermanent indicating contraption damage or glitch) in nature [2]. In any case, these spasmodic faults generally show a for the most part high occasion rate and over the long haul tend to twist up unmistakably unchanging [2]. What's more, devastate of memories in like manner cause sporadic defects to wind up particularly visit enough

A Peer Revieved Open Access International Journal

www.ijiemr.org

to be assigned invariable. Along these lines, there is a prerequisite for online test technique that can recognize the run-time deficiencies, which are unpredictable in nature yet a tiny bit at a time get the chance to be particularly immutable after some time.

#### A. Contribution

In this concise, we have proposed an online straightforward test technique for first-input first-yield (FIFO) bolsters and coordinating method of reasoning present inside the switches of the NoC structure. responsibilities are according to accompanying. A direct SOA-MATS++ test time figuring has proposed centering in-field ceaseless weaknesses made in SRAM based FIFO memories and it has been utilized to perform on the web and discontinuous preliminary of FIFO memory display inside the switches of the NoC. Moreover, we have also proposed an online test strategy for the coordinating method of reasoning that is played out at the same time with the preliminary of pads. The recommendation incorporates two techniques for utilizing the unused fragment of the header skips of the moving toward data distributes transporting the test plans. In any case, deterministic test plans for the coordinating basis delivered by Tetramax are set in the unused fields of the header ripple and are transported in the midst of the standard cycle. Second, the pseudorandom plans in the built data action used in the midst of customary activity and connecting at the controlling method of reasoning are considered as test precedents. Accuse extension is assessed for both of the two suggestions.

### II. RELATED WORK

As error obstruction in NoC design has gotten hugeness among inquire about gathering, different papers have been dispersed covering assorted parts of blame versatility, for instance, dissatisfaction segments, blame illustrating, finding, and so on. A point by point diagram laying out the investigation work in these papers has been provided in [3]. Consistently, masters have proposed different Design-For-Testability (DFT) techniques for NoC system (testing switches and what's more NoC interconnect) [7] and for NoC based focus testing [8]. Worked in singular test (BIST)- based frameworks have been used for testing switches and furthermore NoC interconnect, for instance, [8]. A late paper on NoC and switch testing in [9] gives an outline of the DFT systems used for testing NoC interconnects and switches particularly. Despite novel test plans, blame tolerant controlling computations have also been proposed [10]. FIFO supports in NoC structure are far reaching in number and spread wherever all through the chip. In like manner, probability of shortcomings is higher generally for the supports differentiated and distinctive parts of the switch. Both on the web and separated test frameworks have been proposed preliminary of FIFO underpins in NoC. The suggestion in [11] is a detached test strategy (proper for the ID of gathering issue in FIFO pads) that proposes a typical BIST controller for FIFO supports. Online test procedures for the area of shortcomings in FIFO supports of NoC switches have been proposed in [12]. In any case, the technique considers standard cell-based FIFO pads, while we consider SRAM-based FIFO

A Peer Revieved Open Access International Journal

www.ijiemr.org

designs. Thusly, flaws considered in this brief are special in connection to those centered in [12]. To the best of our understanding, work no has been represented in the composition that proposes online preliminary of SRAM-based FIFO pads appear inside switches of NoC structure. Henceforth, we examined online test frameworks for SRAM-based FIFOs all considered. The investigation revealed that SRAM based FIFOs are had a go at using both of the going with two strategies, committed BIST approach as proposed by Barbagallo et al. in [13] and in addition passed on BIST proposed by Grecu et al. in [11]. Regardless, both submitted and flowed BIST strategies being separated test frameworks disregard to perceive unchanging flaws, whichdevelop after some time.

# III. PROPOSED TRANSPARENT TEST GENERATION

The shortcomings considered in this brief, whenever associated for SRAMs or DRAMs, can be recognized using standard March tests [6]. In any case, if a comparative plan of deficiencies are considered for SRAM-sort FIFOs, March test can't be used particularly as a result of the location control in SRAM-sort FIFOs said in [14] and subsequently we were impelled to pick single-ask for address MATS++ test (SOA-MATS++) [14] for the area of flaws considered in this brief. The wordoriented SOA-MATS++ addressed as { (wa);  $\uparrow$  (ra,wb);  $\downarrow$  (rb,wa)}; (ra)} where, an is the data establishment and b is the supplement of the data establishment. ↑ and ↓ are extending and decreasing tending to demand of memory, independently. \_implies memory having a

tendency to can augment or lessening. Usage of SOA-MATS++ test to the FIFO incorporates making outlines into the FIFO memory and understanding them back. In this way, the memory substance are destroyed. In any case, online memory test frameworks require the reconstructing of the memory substance after test. Thusly, investigators have modified the March tests to direct March test [15] so tests can be performed without the essential of outside data establishment and the memory substance can be restored after test. We have in this way changed the SOA-MATS++ test to clear SOA-MATS++ (TSOA-MATS++) test that can be associated for online preliminary of FIFO bolsters. The direct SOA-MATS++ test delivered is addressed as  $\{\uparrow (rx,w^-x, r^-x,wx, rx)\}$ . The activities performed in the midst of the test address three times of the test, specifically, steamed stage, restore stage, and read arrange. The underlying two activities outline a read create coordinate (rx, wx) addressing the modify organize where the fundamental substance (content before start of test) of the FIFO pad region under test (lut) is scrutinized and its supplement is made back to a comparable zone. The steamed stage is trailed by restore organize including the activities (r - x, wx), where the substance of lut are examined and reinverted. Presently of the test, the substance of lut have been flipped twice to get back the primary substance. The last stage, (rx) incorporates examining the substance of lut with no create task to take after.

## A. Test Algorithm

The algorithmic explanation of the clear SOA-MATS++ test is presented in Algorithm 1. It portrays the very much

A Peer Revieved Open Access International Journal

www.ijiemr.org

arranged framework to play out the three times of the direct SOA-MATS++ test for each zone of the FIFO memory. The target region for test is given by the circle record I that changes from 0 to N-1, where N is the amount of regions in the FIFO memory. By the day's end, I addresses the location of the FIFO memory zone right away under test. For each region, the three preliminaries are performed in the midst of three emphasess of the circle document j. For a particular FIFO memory zone (show estimation of I), the essential cycle of i (address run1) plays out the adjust arrange, where the substance of the FIFO region is changed. The alter test arrange incorporates scrutinizing substance of lut into a fleeting variable temp and after that sponsorship it up in novel. By then, the agitated substance of temp is made back to lut. Presently, the substance of lut is inversion of substance of one of a kind. In the accompanying cycle of i (address run2), the restore arrange is performed. The substance of lut is go over into temp and differentiated and the substance of novel. The examination should achieve all 1's plan. In any case, deviation from the all 1's precedent at any piece position demonstrates blame at that particular piece position. Next, the turned around substance of temp is formed back to lut. Thus, the substance of lut, which were turned around after the vital accentuation get restored after the second. The third cycle of j performs only a read task of lut, where the substance of lut is scrutinized into temp and differentiated and the substance of special. At this period of the test, all 0's precedent in the result indicates blame free territory, deviation at any piece position from all 0's model infers blame at that particular piece

position. The last read activity ensures the area of shortcomings, which remained undetected in the midst of the before two preliminaries. At the finish of the three preliminaries (cycles of j), the circle list I is increased by one to check the start of test for the accompanying territory.

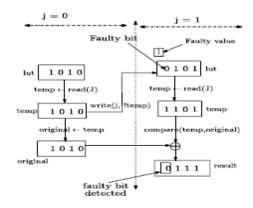

# **B.** Fault Coverage of the Proposed Algorithm

The clear SOA-MATS++ count anticipated preliminary of stuck to blame, move blame, and read disturb blame tests made in the midst of field task of FIFO memories. The blame extent of computation is showed up in Fig. 1. In both the figures, the word size of FIFO memory is believed to be of 4 bits. The substance in italics against the jolts exhibits the task performed, while the substance in solid printed style analyzes to the variables used as a piece of Algorithm 1. As showed up in Fig. 1, acknowledge the data word appear in lut be 1010. The test cycles begin with the resentful stage (memory address pointer j with 0 regard) in the midst of which the substance of territory had a tendency to is examined into temp and after that went down in the first.

Fig.1. Fault Detection during Invert Phase and Restore Phase of the Transparent SOA.MATS++ Test

A Peer Revieved Open Access International Journal

www.ijiemr.org

The data made back to lut is the supplement of substance of temp. Thus, around the finish of the cycle, the data display in temp and novel is 1010, while lut contains 0101. Expect a stuck-at-1 blame and not any more basic piece (MSB) position of the word set away in lut. In like manner, instead of securing 0101, it truly stores 1101 and along these lines, the stuck to blame at the MSB gets invigorated. In the midst of the second accentuation of j, when lut is readdressed, the data read into temp is 1101. Presently, the data show in temp and exceptional are considered (bitwise XORed). An all 1's precedent is ordinary as result. Any 0 inside the model would mean a stuck to blame at that bit position. This condition is showed up in Fig. 1, where the XOR of 1010 and 1101 yields a 0 at the MSB position of the result demonstrating a stuck to blame at the position. **MSB** In any case, circumstances where the basic data for a bit position isn't exactly the same as the broken piece regard, the stuck to blame can't be perceived for the bit position after the restore time of the test. It thusly requires one more test cycle to invigorate such blames.

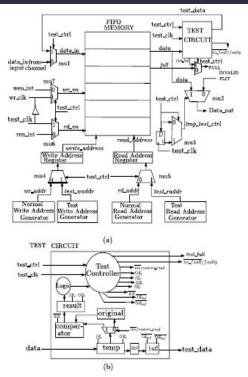

Fig. 2. (a) Hardware implementation of the test process for the FIFO buffers. (b)

Implementation of test circuit.

In this fragment, we display the technique used for executing the proposed direct SOA-MATS++ test on a work sort NoC. Data groups are divided into stream control units (shudders) and are transmitted in pipeline shape [1]. The shudder advancement in a work sort NoC establishment considered for this work is relied upon to require buffering exactly at the information channels of switches. In this way, for a data movement improvement beginning with one focus then onto the following, the online test is performed just on the information channel FIFO underpins, which lie en route. The pads work in two modes, the common mode and the test mode. The conventional mode and test strategy for task of a FIFO bolster are synchronized with two special tickers. The clock used for test reason (insinuated as test\_clk in this brief) is a snappier clock

A Peer Revieved Open Access International Journal

www.ijiemr.org

differentiated and the clock required for common mode (switch clock). The FIFO bolsters are allowed to be specialist in run of the mill mode for sufficient proportion of time before beginning their test strategy. This elay in test begin gives sufficient time to run-time broken shortcomings made in FIFO pads to change into enduring deficiencies. The test technique of a concentrated on FIFO pad is begun by a counter, which switches the FIFO bolster from ordinary mode to test mode. The trading of FIFO supports from normal mode to test mode occurs after a particular time span without considering the present circumstance with the FIFO bolster. It may be battled that right now of trading, the support may not be full, and consequently not all territories would be attempted in the midst of the test cycle. In any case, test begin after the support gets full would achieve the going with issues. In any case, hold up for the cushion to get full would superfluously postpone the test inception process and would enable deficiencies to get collected. Second, trial of the whole support would drag out the test time and would contrarily influence the ordinary method of activity. A test burst includes arrangement of test read and compose cycles. It requires three read and two compose cycles, or at the end of the day three cycles of the quicker test clock to play out a straightforward SOA-MATS++ test on a solitary area of a FIFO cushion. It might be contended that amid a test burst, not all FIFO cradle areas are tried or a trial of an area can get interfered. These two issues can maintained a strategic distance from by occasionally testing the FIFO cradles. Occasional testing of a FIFO cradle permits

trial of an alternate arrangement of areas of the FIFO cushion in each test burst. Each time the cradle is changed to test mode, the ordinary procedure gets intruded. The FIFO memory area right now tended to in typical mode, at the moment of exchanging, turns into the objective area for test. Since ordinary activity is hindered at various moments in various test blasts, the areas tried in each burst would be extraordinary. In this manner, rehashing the test blasts for a number occasions on a FIFO support would cover the trial of every area as the quantity of areas in a FIFO cradle is few. In addition, intermittent testing avoids aggregation of blame in the cushion.

**EXPERIMENTAL RESULTS** A model usage of the proposed test circuit has been incorporated into the switch channel interface and online straightforward SOA-MATS++ test is performed with engineered self-comparative information movement. The switch configuration considered in this brief has been taken from [16].

Fig.3. Simulated Output for In-Field Test for Permanent Faults in FIFO at fault 0

A Peer Revieved Open Access International Journal

www.ijiemr.org

### VII. CONCLUSION

In this short, we have proposed a clear SOA-MATS++ btest period computation that can distinguish run-time enduring deficiencies made in SRAM-based FIFO memories. The proposed clear test is utilized to perform on the web and irregular preliminary of FIFO memory present inside the switches of the NoC. Infrequent testing of cradles abstains from social affair of shortcomings besides allows preliminary of each territory of the cushion. Reenactment comes to fruition show that irregular testing of FIFO supports don't have much effect on the general throughput of the NoC beside when cradles are attempted too once in a while. We have in like manner proposed an online test framework for the coordinating method of reasoning that is played out at the same time with the preliminary of cradles and incorporates utilization of the unused fields of the header ricochets of the moving toward data groups for test configuration encoding. As future work, we should need to change the proposed FIFO testing framework that will allow moving toward data bundles to the switch under test without barging in on the test.

#### VIII. REFERENCES

[1]W. J. Dally and B. Towles, "Route packets, not wires: On-chip interconnection networks," in Proc. 38th Annu. Design Autom. Conf., 2001, pp. 684–689.

[2]A. Bondavalli, S. Chiaradonna, F. Di Giandomenico, and F. Grandoni, "Threshold-based mechanisms to discriminate transient from intermittent faults," IEEE Trans. Comput., vol. 49, no. 3, pp. 230–245, Mar. 2000.

[3]M. Radetzki, C. Feng, X. Zhao, and A. Jantsch, "Methods for fault tolerance in

networks-on-chip," ACM Comput. Surv., vol. 46, no. 1, pp. 1–38, Jul. 2013, Art. ID 8. [4]S. Ghosh and K. Roy, "Parameter variation tolerance and error resiliency: New design paradigm for the nanoscale era," Proc. IEEE, vol. 98, no. 10, pp. 1718–1751, Oct. 2010.

[5]S. Borri, M. Hage-Hassan, L. Dilillo, P. Girard, S. Pravossoudovitch, and A. Virazel, "Analysis of dynamic faults in embedded-SRAMs: Implications for memory test," J. Electron. Test., vol. 21, no. 2, pp. 169–179, Apr. 2005. [6]M. Bushnell and V. Agrawal, Essentials of Electronic Testing for Digital, Memory and Mixed-Signal VLSI Circuits (Frontiers in Electronic Testing). New York, NY, USA: Springer-Verlag, 2000.

[7]D. Xiang and Y. Zhang, "Cost-effective power-aware core testing in NoCs based on a new unicast-based multicast scheme," IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., vol. 30, no. 1, pp. 135–147, Jan. 2011. [8]K. Petersen and J. Oberg, "Toward a scalable test methodology for 2D-mesh network-on-chips," in Proc. Design, Autom., Test Eur. Conf Exhibit., Apr. 2007, pp. 1–6.

[9]D. Xiang, "A cost-effective scheme for network-on-chip router and interconnect testing," in Proc. 22nd Asian Test Symp. (ATS), Nov. 2013, pp. 207–212.

[10]M. Ebrahimi, M. Daneshtalab, J. Plosila, and H. Tenhunen, "Minimal-path fault-tolerant approach using connection-retaining structure in networks-on-chip," in Proc. 7th IEEE/ACM Int. Symp. Netw. Chip (NoCS), Apr. 2013, pp. 1–8.

[11]C. Grecu, P. Pande, B. Wang, A. Ivanov, and R. Saleh, "Methodologies and algorithms for testing switch-based NoC interconnects," in Proc. 20th IEEE Int.

A Peer Revieved Open Access International Journal

www.ijiemr.org

Symp. Defect Fault Tolerance VLSI Syst., Oct. 2005, pp. 238–246.

[12] M. R. Kakoee, V. Bertacco, and L. Benini, "A distributed and topologyagnostic approach for on-line NoC testing," in Proc. 5th ACM/IEEE Int. Symp. Netw. Chip, May 2011, pp. 113–120.