A Peer Revieved Open Access International Journal

www.ijiemr.org

### COPY RIGHT

**2018 IJIEMR**.Personal use of this material is permitted. Permission from IJIEMR must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 25<sup>th</sup> Sept 2018. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-7&issue=ISSUE-10

Title: A NEW HARDWARE AND ENERGY EFFICIENT STOCHASTIC LUD SCHEME FOR MIMO TECHNOLOGY

Volume 07, Issue 10, Pages: 99–104. Paper Authors

### KANDIMALLA ANITHA, U.V.SIVAIAH

Krishnaveni Engineering College for Women, Kesanupalli

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

### A NEW HARDWARE AND ENERGY EFFICIENT STOCHASTIC LUD SCHEME FOR MIMO TECHNOLOGY KANDIMALLA ANITHA, U.V.SIVAIAH

PG Scholar, ECE Department, Krishnaveni Engineering College for Women, Kesanupalli Associate Professor, ECE Department, Krishnaveni Engineering College for Women, Kesanupalli.

**Abstract:** In this paper, we design a hardware and energy-efficient stochastic lower–upper decomposition (LUD) scheme for multiple-input multiple-output receivers. By employing stochastic computation, the complex arithmetic operations in LUD can be performed with simple logic gates. With proposed dual partition computation method, the stochastic multiplier and divider exhibit high computation accuracy with relative short length stochastic stream

#### I. INTRODUCTION

fundamental Framework decay is a calculation in the direct arrangement issue. Particularly, in the numerous info different (MIMO) frameworks, vield lattice deterioration is the principle load for the execution of equipment and the vitality proficient MIMO finder. The current framework disintegration advancement strategies go for huge size networks, for example, measurement with 16 kB. Nonetheless. in the viable MIMO frameworks, the size of radio wires is constrained by the zone of recieving wire cluster. For instance, in the long haul development (LTE) measures, the MIMO frameworks utilize a 4×4 measurement radio wire cluster. Indeed, even in the expansive scale MIMO framework, the required reversal grid measurement is close to 100. The MIMO frameworks are occupied with more equipment productive and vitality proficient VLSI usage of lattice decay calculation. For the most part, there are two methodologies fundamental for the framework disintegration technique in MIMO frameworks: 1) QR deterioration and 2) lower-upper decay (LUD). QR decay

calculation, which moves a framework into a symmetrical network and an upper triangular lattice, is broadly utilized in the look based **MIMO-identification** way calculation. In the other angle, LUD calculation factorizes a lattice into a lower triangular grid and an upper triangular framework. LUD has a similar capacity asQR deterioration, which serves for a way seek based MIMO location. Also, LUD is a crucial handling in the zero-compel (ZF) and the base mean square mistake (MMSE)based MIMO framework. In this paper, we center around the execution of LUD calculation. A lot of LUD strategies have been, for example, parallel-preparing based, roundabout straight exhibit based, and blocking-construct designs that objective in light of extensive size grids with high throughput. Be that as it may, vitality utilization and equipment unpredictability are two lethal plan measures in the remote correspondence frameworks, particularly for the portable terminals. Thus, it is important to plan an elite LUD plot particular for the MIMO frameworks. In a LUD in view of calculation sharing multiplier (CSHM) is

A Peer Revieved Open Access International Journal

www.ijiemr.org

proposed, which has significant vitality sparing limit. A surmised framework reversal structure for expansive scale MIMO uplink is proposed in, which must be utilized in the framework with gigantic getting reception apparatuses. In this paper, we plan and actualize the LUD by a fascinating calculation technique, stochastic rationale. The stochastic rationale has been proposed decades prior and broadly utilized in the neural system framework. Most as of late, specialists utilized the stochastic calculation correspondence flag in the handling frameworks and accomplished motivated outcomes. А stochastic low-thickness equality check (LDPC) code decoder proposed in accomplishes 61.3 Gbit/s, and a stochastic turbo decoder proposed in [15] has a throughput of 4 Gbit/s.

The achievement of applying stochastic calculation in decoder fortifies us to actualize а more extensive class correspondence calculation with stochastic rationale, for example, MIMO location. As a key handling of ZF and MMSE, a superior LUD processor is required. In this paper, we propose a few new procedures to take care of these issues. To begin with, we propose a double segment calculation (DPC) strategy to speak to and process the high quantization bit-width motion with a moderately short length stream. For instance, we just need a 128-length stochastic stream to speak to and process a 12-bit FP motion rather than 4096. Obviously, we can segment the stream into different areas, for example, three or four. Be that as it may, the more segments prompt higher calculation multifaceted nature of stochastic calculations.

#### **II. EXISTING SYSTEM**

By and large, there are two principle approaches for the lattice disintegration technique in MIMO frameworks: 1) QR decay and 2) lower- upper deterioration (LUD). QR deterioration calculation, which moves a framework into a symmetrical grid and an upper triangular network, is generally utilized in the way seek based MIMOidentification calculation. In the other angle, LUD calculation factorizes a grid into a lower triangular network and an upper triangular lattice. LUD has indistinguishable capacity from QR decay, which serves for a way seek based MIMO recognition. In addition, LUD is a key handling in the zeroconstrain (ZF) and the base mean square mistake (MMSE)- based MIMO framework. In this paper, we center around the execution of LUD calculation. The principle difficulties of LUD usage with stochastic rationale are as per the following. Long Computation Latency: The quantization bitwidth of LUD flag ought to be higher than that of decoders. Consequently, an any longer stochastic stream is required in the calculation procedure. For instance, a 12-bit settled point (FP) flag is spoken to as a stochastic arrangement with the length of 212 = 4096 in stochastic calculation space. It will take 4096 clock cycles to process the stream in the serial calculation mode. Huge Computation Variance: Since bits in a stochastic stream are produced with irregular appropriations, as initially imagined, the outcome processed by the stochastic stream has expansive change, which will lessen the exactness broadly. Consequently, stochastic calculation is difficult to be connected in the calculation that requires high calculation exactness.

A Peer Revieved Open Access International Journal

www.ijiemr.org

Difficult to reach for Stochastic Division: The investigations of stochastic calculation for the most part center around augmentations and increases. The examination for stochastic division is restricted. In [16], a J- K trigger-based stochastic divider (SD) is proposed. Nonetheless, the calculation mistake is too huge to possibly be connected into the pragmatic framework.

### **III.PROPOSED SYSTEM**

The proposed stochastic LUD is reproduced and checked by motion to-clamor proportion (SNR) execution. We likewise apply the stochastic LUD to the MMSE-based MIMO framework to give the execution examination. We blend the stochastic LUD in the TSMC 130-nm innovation and give a point by point equipment examination results in this paper. In synopsis, our commitments are appeared as takes after.

1) The proposed DPC technique can lessen the calculation inactivity from 2k to 2k/2+1. With DPC, stochastic calculation can be connected in a more extensive class of high quantization width-based flag handling framework, for example, quick Fourier change and limited drive reaction channel.

2) The proposed elite multiplier and divider for DPC have high calculation precision with short stream and moderately low equipment cost. For instance, the proposed stochastic multiplier and SD can accomplish the SNR of 70 and 65 dB with 128-length stream, separately. Additionally, the proposed stochastic multiplier and SD can be connected to other flag handling frameworks.

3) The proposed stochastic LUD can be connected in the functional MIMO locator,

which is confirmed by SNR and MMSEbased bundle mistake rate (PER) execution. 4) The stochastic LUD is actualized in a completely parallel frame. Accordingly, with stochastic rationale, the proposed LUD has a basic control and a calculation structure. As per the execution report, in the wake of setting and steering, the equipment productivity is  $1.5 \times$  as the current LUD structures. The vitality productivity additionally outperform the CSHM-based LUD when the measurement is  $8 \times 8$  or higher.

We propose a few new methods to solvethese issues. To begin with, we propose a double parcel calculation (DPC) technique to speak to and process the highquantization bit-width motion with a moderately short lengthstream. For instance, we just need a 128-length stochastic stream to speak to and process a 12-bit FP flag insteadof 4096. Obviously, we can segment the stream into multiplesections, for example, three or four. Be that as it may, the more parcels prompt higher calculation intricacy of stochasticcomputations. calculation strategies will be tended to infuture work. Second, we propose a high-exactness stochastic multiplier in view of DPC. In, a few deterministic stochastic calculation (DSC)methods are proposed to improve the increase exactness. In light of DSC and DPC, we proposed a superior stochastic multiplier. Third, a high-exactness divider in view of DPC is additionally proposed in this paper. Stochastic calculation is a groundbreaking apparatus for flag preparing frameworks. Data is spoken to by the factual mean of an arbitrary piece stream. In this paper, we apply a marked stochastic stream to speak to the FP motion in two's

A Peer Revieved Open Access International Journal

#### www.ijiemr.org

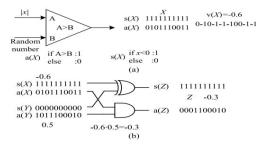

supplement framework (TCS). As appeared in Fig. 1(a), the outright estimation of x is contrasted and a positive irregular number with uniform appropriations. A twofold piece stream X is acquired at the yield of the comparator with the esteem bit a(X), while the marked piece of the TCS signals x is yielded specifically as a stream s(X). For instance, with a specific end goal to speak to an estimation of -0.6, six out of ten bits are 1 in a(X), and the bits in the marked stream s(X) are

Fig.1. Stochastic logic, (a) Sequence generator scheme, (b) Stochastic signed multiplier.

Hence, the value of a stochastic stream X represented is given by

$$v(X) = \frac{1}{L} \sum_{t=1}^{L} X(t) = \frac{1}{L} \sum_{t=1}^{L} (1 - 2 \cdot s(X)) \cdot a(X)$$

(1)

1.

Where, L denotes the stochastic stream length the multiplication of X and Y can be performed with bitwise operation as shown in Fig. 1(b).

The AND gate is used to perform the absolute multiplication, and the exclusive OR gate is employed to obtain the signed stream. Thus, the complex arithmetic operation can be implemented by simple logic gates in stochastic domain. We first review the LUD algorithm in this section (Algorithm 1). Suppose a nonsingular matrix A with  $N \times N$  dimension is decomposed by LUD algorithm A = LU. The LUD algorithm involves three arithmetic operations: multiplication, addition, and division

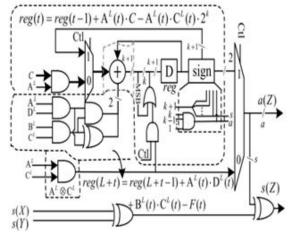

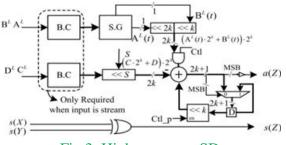

#### A. DPC-Based Stochastic Multiplier

The hardware scheme of DPC-based stochastic multiplier is given in Fig2. We highlight the logic gates with corresponding function to help understand the structure.

Fig.2. High-accuracy stochastic multiplier.

The hardware implementation scheme of proposed SD is given in Fig3. The back converter (B.C.) which converts stochastic stream to FP signal can be bypassed when the input signal is already a TCS signal.

#### Fig.3. High-accuracy SD.

The proposed stochastic LUD is recreated and confirmed by motion to-clamor proportion (SNR) execution. We additionally apply the stochastic LUD to the MMSE-based MIMO framework to give the execution investigation. We blend the

A Peer Revieved Open Access International Journal

www.ijiemr.org

stochastic LUD in the TSMC 130-nm innovation and give a point by point equipment correlation results in this paper. In outline, our commitments are appeared as takes after.

1) The proposed DPC strategy can lessen the calculation dormancy from 2k to 2k/2+1. With DPC, stochastic calculation can be connected in a more extensive class of high quantization width-based flag handling framework, for example, quick Fourier change and limited drive reaction channel.

2) The proposed elite multiplier and divider for DPC have high calculation precision with short stream and generally low equipment cost. For instance, the proposed stochastic multiplier and SD can accomplish the SNR of 70 and 65 dB with 128-length stream, separately. Additionally, the proposed stochastic multiplier and SD can be connected to other flag preparing frameworks.

3) The proposed stochastic LUD can be connected in the down to earth MIMO locator, which is checked by SNR and MMSE-based parcel blunder rate (PER) execution.

4) The stochastic LUD is actualized in a completely parallel shape. Subsequently, with stochastic rationale, the proposed LUD has a basic control and a calculation structure. As indicated by the usage report, in the wake of putting and steering, the equipment proficiency is  $1.5 \times$  as the current LUD designs. The vitality proficiency additionally outperform the CSHM-based LUD when the measurement is  $8 \times 8$  or higher.

#### **IV. SIMULATION RESULTS**

### **V. CONCLUSION**

In this paper, we proposed a stochasticbased LUD conspire with high equipment productivity and power effectiveness. To accomplish high exactness, we displayed a few novel systems to enhance stochastic calculation execution. The proposed DPC has decreased the calculation idleness from 2k to 2k/2+1. The high-precision SM and SD can accomplish SNR execution of 60 dB, which is equipped for utilizing the proposed stochastic rationale to the framework that requires high calculation. The plan proposed in this paper can likewise be utilized in other DSP frameworks.

#### References

[1] J. N. Franklin, Matrix Theory (Dover Books on Mathematics). Englewood Cliffs, NJ, USA: Prentice-Hall, 2000.

[2] C. Studer, S. Fateh, and D. Seethaler, "ASIC implementation of soft-input softoutput MIMO detection using MMSE parallel interference cancellation," IEEE J. Solid-State Circuits, vol.46, no.7, pp.1754– 1765, Jul. 2011.

[3] G. Wu, Y. Dou, J. Sun, and G. D. Peterson, "A high performance and memory efficient LU decomposer on FPGAs," IEEE Trans. Comput., vol. 61, no. 3, pp. 366–378, Mar. 2012.

A Peer Revieved Open Access International Journal

www.ijiemr.org

[4] M. K. Jaiswal and N. Chandrachoodan, "FPGA-based high-performance and scalable block LU decomposition architecture," IEEE Trans. Comput., vol. 61, no. 1, pp. 60–72, Jan. 2012.

[5] G. Govindu, S. Choi, V. Prasanna, V. Daga, S. Gangadharpalli, and V. Sridhar, "A high-performance and energy-efficient architecture for floating-point based LU decomposition on FPGAs," in Proc. 18th Int. Parallel Distrib. Process. Symp., Apr. 2004, pp. 149–156.

[6] P. Salmela, A. Burian, H. Sorokin, and J. Takala, "Complex-valued QR decomposition implementation for MIMO receivers," in Proc. IEEE Int. Conf. Acoust., Speech, Signal Process., Mar./Apr. 2008, pp. 1433–1436.

[7] C. K. Singh, S. H. Prasad, and P. T. Balsara, "VLSI architecture for matrix inversion using modified Gram-Schmidt based QR decomposition," in Proc. 20th Int. Conf. VLSI Design, Jan. 2007, pp. 836–841.

[8] M. Shabany, D. Patel, and P. G. Gulak, "A low-latency low-power QR-decomposition ASIC implementation in 0.13 μm CMOS," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 60, no. 2, pp. 327–340, Feb. 2013.

[9] J.-W. Choi, J. Lee, B. G. Min, and J. Park, "Energy efficient hardware architecture of LU triangularization for MIMO receiver," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 57, no. 8, pp. 632–636, Aug. 2010.