A Peer Revieved Open Access International Journal

www.ijiemr.org

### **COPY RIGHT**

2018 IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors IJIEMR Transactions, online available on 22 April 2018. Link:

http://www.ijiemr.org/downloads.php?vol=Volume-6&issue=ISSUE-3

**Title:** Design a Congestion Aware Routing Algorithm for Synchronous Cam Design Volume 07, Issue 04, Pages: 109 – 117.

**Paper Authors**

P. MOUNICA, R. UMAMAHESWARI, R. MADHAVI, R. NISCHALA, N.RAMESH BABU

Dept of ECE, Sri Sai Institute of Engineering and technology, Bhimavaram, AP, India.

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

# DESIGN A CONGESTION AWARE ROUTING ALGORITHM FOR SYNCHRONOUS CAM DESIGN

<sup>1</sup>P. MOUNICA, <sup>2</sup>R. UMAMAHESWARI, <sup>3</sup>R. MADHAVI, <sup>4</sup>R. NISCHALA, <sup>5</sup>N.RAMESH BABU

<sup>1,2,3,4</sup>B.Tech-Scholar, Dept of ECE, ST. Mary's Women's Engineering College, Guntur, India. <sup>5</sup>Assistant Professor, Dept of ECE, ST. Mary's Women's Engineering College, Guntur, India.

ABSTRACT: The effect of process variation (PV) on delay is a major reason to decay the performance in advanced technologies. The performance of front routing algorithms is determined with or without PV for different traffic patterns. The saturation throughput and average message delay are used as performance metrics to evaluate the throughput. PV decreases the saturation throughput and increases the average message delay. Adaptive routing algorithm should be manipulated with the PV. A novel PV delay and congestion aware routing (PDCR) algorithm is presented for asynchronous network-on-chip (NOC) design. The routing algorithm performs various adaptive routing algorithms in the average delay and saturation throughput for different traffic patterns. A low-power content-addressable memory (CAM) by a new algorithm is proposed for associativity between the input tag and the corresponding address of the output data. The proposed architecture is depends on a recently developed sparse clustered network by utilizing binary connections that on-average eliminates most of the parallel comparisons performed during a search.

ISSN: 2456 - 5083

### INTRODUCTION

for International Technology roadmap Semiconductors presented the process variation (PV) parameters as a critical challenge for manufacturing IC. Systematic and random variations are two sources for PV with technology scaling down random variation becomes significantly larger than systematic

variation. Random variation appears in logic gates and interconnectors. The impact of random PV emerged on low and high levels of designs.

One of the key factors of designing network on chip (NOC) is the routing algorithm. An efficient routing algorithm is required to achieve high performance. Hence, ignoring the impact of PV during the design of any

A Peer Revieved Open Access International Journal

www.ijiemr.org

routing algorithm results in unexpected average message delay and saturation throughput is used as two metrics to evaluate the performance of a routing algorithm. The saturation throughput occurs when no additional messages can be injected successfully to the network. Prior to the saturation throughput, the average message delay slightly increases with the injection load. However, the average message delay increases exponentially beyond the network situation.

As a hardware solution, a new router design is existed to mitigate PV impact. A variation-adaptive variable-cycle configures its cycle latency adaptively according to the spatial PV for increasing the network frequency in the asynchronous network. Adaptive routing algorithm for multi-core NOC architectures is presented for reducing saturation bandwidth degradation which is caused by PV's. The source routing algorithm is introduced for enhancing the speed of communication in an NOC based on PV.

To the best of our knowledge, the work presented in this paper is the first work to investigate the impact of PV on different routing algorithms. Moreover, an adaptive

ISSN: 2456 - 5083

routing algorithm that is aware of the PV and congestion for asynchronous NOC designs is introduced in this paper.

In this paper, a novel adaptive routing algorithm is proposed for asynchronous NOC designs to reduce the effect of PV. The presented algorithm is applicable with any source of PV. The technique is insensitive for the source of the variation. The novel routing algorithm utilizes the PV and congestion information as metrics to select the suitable output port (OP). In addition, the realistic values of average message delay and saturation throughput under high PV for different routing algorithms are compared with that of nominal value (without PV).

#### II.EXISTED SYSTEM

The existed algorithm can be divided into two procedures: 1) Determining target node (TN) and 2) selection criterion for the OP. The details of the procedure are described in sections.

1. Determining the Target Node (TN): At source router, a random intermediate (IM) router is chosen between the source and the destination as an IM station during the message trip. Thereby the message has two phases (ph-1, ph-0) when it is routed from the source to the destination. At ph-0 the

A Peer Revieved Open Access International Journal

www.ijiemr.org

message is routed from the source to the IM node ph-1 is used when the message is forwarded from the IM router to the destination router. In PDCR, a uniform random distribution function is used to select a random IM router between the source and destination. In addition, phase (PH) and IM fields are added into each message to retain the values of the message phase and the IM router identification (Id).

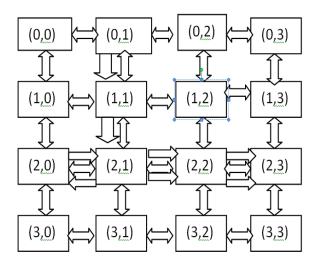

Fig 1: Exploiting the same path for more than one time

Each router needs to declare the TN whether it is the IM or destination router. When each router forwards the message to the TN, it applies XY and YX routing algorithms to calculate the OP direction (i.e., N=0). The integer value of the output direction is denoted by Pxy when XY routing algorithm

is used. Pyx denotes the integer value of the output direction when YX routing algorithm is used to route the message for TN. The default value of ph field of the message is set to zero. However, ph field of the message is assured from ph0 to ph1 in one of the following cases:

- 1) If the current router is the IM router;

- 2) If the current router exists in the same row of the destination router (rx==dx);

- 3) If the current router exists in the same column of the destination router (ry==dy);

Where the coordinates of current router are rx for X coordinator and ry for Y coordinator. In addition, dx is utilized for the X coordinator of the destination node and dy is used for the Y coordinator of the destination node. If one of the three conditions is true, this is sufficient to make ph field equal to one, and hence the TN is assigned to the destination router ID. On the other hand, when none of the three conditions is achieved, ph field is equals zero and hence the TN is assigned IM field of the message.

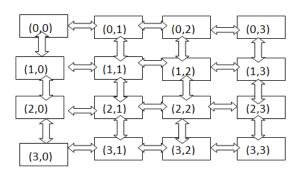

2) Selection Criterion for the Output Port (OP): After applying XY and YX routing algorithms, PDCR distinguishes between

A Peer Revieved Open Access International Journal

www.ijiemr.org

these two output direction (Pxy,Pyx) bases on the congestion and Delay with PV (DPV). At each router, the congestion (Cxy) of the neighbor router and the DPV between the current router and the neighbor router (if XY routing algorithm is used) are compared with the congestion (Cyx) of the neighbor router and the DPV of (yxPV) between the currR and the neighbor router (if yx routing algorithm is used). By comparing two ports using six parameters there are three main scenarios that should be handled.

Fig 2: example for same direction of OP

#### **III.PROPOSED SYSTEM**

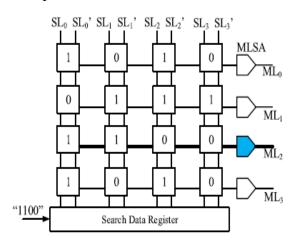

In a conventional CAM array, each entry consists of a tag that, if matched with the input, points to the location of a data word in a static random access memory (SRAM) block. The actual data of interest are stored in the SRAM and a tag is simply a reference to it. Therefore, when it is required to search for the data in the SRAM, it suffices to

search for its corresponding tag. Consequently, the tag may be shorter than the SRAM-data and would require fewer bit comparisons.

An example of a typical CAM array, consisting of four entries having 4 bits each, is shown in Fig. 3. A search data register is used to store the input bits. The register applies the search data on the differential SLs, which are shared among the entries. Then, the search data are compared against all of the CAM entries. Each CAM-word is attached to a common match line (ML) among its constituent bits, which indicates, whether or not, they match with the input bits. Since the MLs are highly capacitive, a sense amplifier is typically considered for each ML to increase the performance of the search operation.

Fig. 3. 4×4 CAM array

A Peer Revieved Open Access International Journal

www.ijiemr.org

As an example, in TLBs, the tag is the virtual page number (VPN), and the data are the corresponding physical page number (PPN). A virtual address generated by the CPU consists of the VPN, and a page offset. The page offset is later used along with PPN to form the physical address. Since most translation look-aside buffers (TLBs) are fully associative, in order to find the corresponding PPN, a fully parallel search among VPNs is conducted for every generated virtual address.

A BCAM cell is typically the integration of 6-transistor (6T)SRAM cell circuitry. The comparator comparator circuitry is made out of either an XNOR or an XOR structure, leading to a NAND-type or a NOR-type operation, respectively. The selection of the comparing structure depends the performance and the power requirements, as a NAND-type operation is slower and consumes less energy as opposed to that of a NOR type.

In a NAND-type CAM, the MLs are precharged high during the precharge phase. During the evaluation phase, in the case of a match, the corresponding ML is pulled down though a series of transistors performing a login NAND in the comparison process. In a NOR-type CAM

the MLs are also precharged high during the precharge phase. However, during the evaluation phase, all of the MLs are pulled down unless there is a matched entry such that the pull-down paths M3-M4 and M5-M6 are disabled. Therefore, a NORtype CAM has a higher switching activity compared with that of a NAND type since there are typically more mismatched entries than the matched ones. Although a NANDtype CAM has the advantage of lower energy consumption compared with that of the NOR-type counterpart, it has two drawbacks: 1) a quadratic delay dependence on the number of cells due to the serial pulldown path and 2) a low noise margin.

#### IV.RESULTS

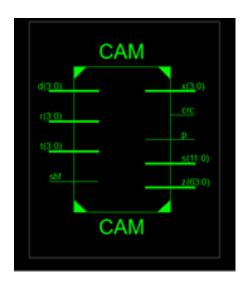

Fig 4:RTL Schematic

A Peer Revieved Open Access International Journal

www.ijiemr.org

Fig 5: Technology Schematic

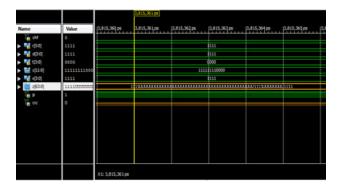

Fig 6: Output Waveform

#### **V.CONCLUSION**

Delay variation in logic gates and inter connect is produced as a result of PV which impacts NOC design. The delay variation is major reason to deteriorate performance of routing algorithms. The PV decreases the saturation throughput and increases average message delay relative to nominal. This paper presents the first study of the influence of PV on different routing algorithms. In this paper, the algorithm and the architecture of a low-power CAM are introduced. The proposed architecture employs a novel associativity mechanism based on a recently developed family of associative memories. CAM is suitable for low-power applications, where frequent and parallel look-up operations are required. Depending on the application, non-uniform inputs result in higher may consumptions, but does not affect the accuracy of the final result. In other words, a few false-positives may be generated by the SCN-based classifier, which are then filtered by the enabled CAM sub-blocks. Therefore, no false-negatives are ever generated.

#### **VI.REFERENCES**

- [1] A. Agarwal *et al.*, "A 128×128 b high-speed wide-and match-line content addressable memory in 32 nm CMOS," in *Proc. ESSCIRC*, Sep. 2011, pp. 83–86.

- [2] Y.-J. Chang and M.-F. Lan, "Two new techniques integrated for energyefficient TLB design," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 15, no. 1, pp. 13–23, Jan. 2007.

- [3] H. Chao, "Next generation routers," *Proc. IEEE*, vol. 90, no. 9, pp. 1518–1558, Sep. 2002.

- [4] N.-F. Huang, W.-E. Chen, J.-Y. Luo, and J.-M. Chen, "Design of multifield IPv6 packet classifiers using ternary CAMs," in

A Peer Revieved Open Access International Journal

www.ijiemr.org

*Proc. IEEE Global Telecommun. Conf.*, vol.3. 2001, pp. 1877–1881.

[5] M. Meribout, T. Ogura, and M. Nakanishi, "On using the CAM concept for parametric curve extraction," *IEEE Trans. Image Process.*, vol. 9, no. 12, pp. 2126–2130, Dec. 2000.

[6] M. Nakanishi and T. Ogura, "A real-time CAM-based Hough transform algorithm and its performance evaluation," in *Proc. 13th Int. Conf. Pattern Recognit.*, vol. 2. Aug. 1996, pp. 516–521.

[7] L.-Y. Liu, J.-F. Wang, R.-J. Wang, and J.-Y. Lee, "CAM-based VLSI architectures for dynamic Huffman coding," *IEEE Trans. Consum. Electron.*, vol. 40, no. 3, pp. 282–289, Aug. 1994.

[8] C.-C. Wang, C.-J. Cheng, T.-F. Chen, and J.-S. Wang, "An adaptively dividable dual-port BiTCAM for virus-detection processors in mobile devices," *IEEE J. Solid-State Circuits*, vol. 44, no. 5, pp. 1571–1581, May 2009.

[9] B. Wei, R. Tarver, J.-S. Kim, and K. Ng, "A single chip Lempel–Ziv data compressor," in *Proc. IEEE ISCAS*, May 1993, pp. 1953–1955.

PUNNA. MOUNICA

Studying B.Tech in

ST.Mary's women's

engineering college

during 2014-2018. Her area of interest is communication.

RAJAMANNAR.UMAMA

HESWARI Studying

B.Tech in ST.Mary's

women's engineering

college during 2014-2018.

Her area of interest is communication.

RAJUPALEM MADHAVI Studying B.Tech in ST.Mary's women's engineering college during 2014-2018. Her area of

interest is communication.

ISSN: 2456 - 5083

RAMAKURU NISCHALA Studying B.Tech in ST.Mary's women's engineering college during

2014-2018. Her area of interesst is communication.

A Peer Revieved Open Access International Journal

www.ijiemr.org

N.RAMESH BABU, M. Tech working as ASST. Professor in ST. Mary's women's engineering in department of area of interest is embedded