A Peer Revieved Open Access International Journal

www.ijiemr.org

### **COPY RIGHT**

2018 IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 10<sup>th</sup> January 2018. Link:

http://www.ijiemr.org/downloads.php?vol=Volume-7&issue=ISSUE-01

**Title**: A New Nested Neutral Point-Clamped (NNPC) Inverter for a Simple Capacitor Voltage balancing.

Volume 07, Issue 01, Page No: 20 - 26.

**Paper Authors**

### \*GADDAMEEDHI MAHENDHAR, V.KRISHNAMURTHY.

\* Dept of EEE, Tudi Ramreddy Institute of Science and Technology.

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

# A NEW NESTED NEUTRAL POINT-CLAMPED (NNPC) INVERTER FOR A SIMPLE CAPACITOR VOLTAGE BALANCING

### \*GADDAMEEDHI MAHENDHAR, \*\*V.KRISHNAMURTHY

\*PG Scholar, Dept of EEE, Tudi Ramreddy Institute of Science and Technology

\*\*Assistant Professor, Dept of EEE, Tudi Ramreddy Institute of Science and Technology

#### **ABSTRACT**

Balancing of capacitor voltage by using logic switching table for nested neutral point clamped (NNPC) inverter is proposed in this thesis. NNPC inverter is a four level voltage source inverter in conversion of medium voltages, in range of (2.2-7.4kv) without using semiconductor devices in series it, to obtain high output voltage. NNPC network consists of two flying capacitors in each phase. So that inverter can operator balancing condition and voltage across each switching device can have same voltage drop, controlled maintained 1/3 DC supply voltage the balancing of capacitor voltage in this way makes the advantages of less switching losses, controlled and balancing the flying capacitor voltage. For this process a simply logic tables are constructed for balancing voltage controlled technique. So that in this way balance the capacitor voltage needs less calculation compared to other techniques. This method is also suitable to integrate with different modulation schemes like pulse width modulation space sector modulation and sinusoidal pulse width modulation etc., these results are verified by using simulation technique.

### **INTRODUCTION:**

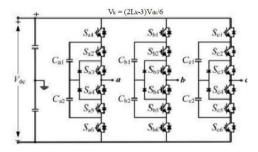

Nowadays, Multilevel inverters are very popular in medium voltage applications and motor drives due to reduction of harmonics, low voltage stress on switches, low switching frequency, and less switching losses [1]. The multilevel inverters categorized into neutral point clamped (NPC) inverter, flying capacitor (FC) inverter, cascaded Hbridge inverter, and modular multilevel converter [2]–[3]. Several control techniques and modulation strategies including capacitor voltage-balancing methods have developed in the literature for multilevel inverters [4]. In this paper a new multilevel topology is proposed. i.e, nested neutral point clamped (NNPC) inverter shown in Fig. 1.

Fig. 1. Three phase nested neutral-point clamped (NNPC) inverter.

# NESTED NEUTRAL POINT CLAMPED INVERTER

### **Operation of the NNPC inverter:**

Figure(1) shows the three phase NNPC inverter .Each phase of NNPC consists of two FCS, six switches and two clamping diodes .keep the fcs voltage at Vdc/3 to produce four output levels in phase voltage so that all the switches can share equal voltage stress. Table 1 shows the output level Lk, phase voltage Vk and corresponding switching state Sk. The four different voltages -Vdc/2, -Vdc/6, Vdc/6 and Vdc/2 for levels 0,1, 2 and 3.The relation between Vk and Kk is given below.

Vk = (2Lk-3)Vdc/6

For level 3 and level 0, there is no unwanted switching state. for level 1 have two unwanted switching states 1A and 1B .the two unwanted switching states produce equal output voltage -Vdc/6 for different ON and OFF switching's .for level 2 also have

A Peer Revieved Open Access International Journal

www.ijiemr.org

two unwanted switching's states, they are 2A and 2B and produce equal output voltage Vdc/6 for different ON and OFF switching's.

# Behaviour analysis of the capacitor voltages in the NNPC inverters:

The capacitors Ck1 and Ck2 are two series FCs in the phase K and Vcks are two voltages across each capacitor respectively the behavior of capacitor voltages depends on the phase current Ik and switching states S k.

There are stages in the behavior of the capacitor voltage in the NNPC inverter.

### Stage (1)

For level 0 and level 3, there is no problem on capacitor voltages because no current flows through capacitors as shown in figures 1.1 and 1.2

Figure 1.2 Switching state 0

Figure 1.3 Switching state 3

### Stage (2)

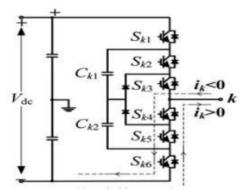

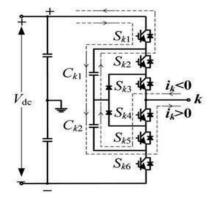

For level 1, the unwanted switching state 1A and ik>0, capacitor Ck2

discharges and capacitor Vck2 decreases.

If Ik <0, the capacitor Ck2 charges and Vck2 increases and there is no impact on capacitor Ck1, shown in figure 1.3.

Figure 1.4 Switching state 1A

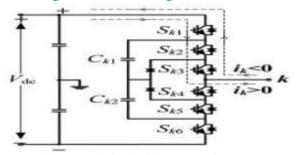

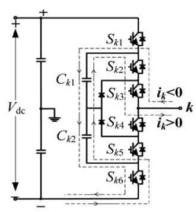

### For switching state 1B

When Ik>0, the capacitor Ck1 and Ck2 charge and capacitor voltage Vck1 and Vck2 increases.

When Ik<0, the Ck1 and Ck2 discharge and Vck1 and Vck2 decrease shown in figure 1.4.

Figure 1.5 Switching state 1B.

### Stage 3

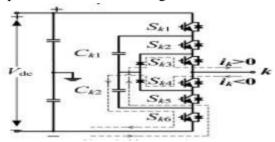

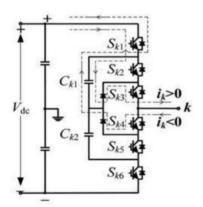

For level 2A

When Ik>0, both capacitors Ck1 and Ck2 discharges and capacitor voltage Vck1 and Vck2 decrease.

When Ik<0, both capacitors Ck1 and Ck2 charge and capacitor voltage increase, as shown in figure 1.5.

A Peer Revieved Open Access International Journal

www.ijiemr.org

Figure 1.6 switching state 2A

For level 2B

When Ik>0, capacitor Ck1 is charge and voltage Vck1 increase.

When Ik<0, capacitor Ck1 is discharge and voltage Vck1 decrease, as shown in figure 1.6.

Figure 1.7 Switching state 2B.

The above switching state of each stage is based on the simple logic table as shown below.

#### Table (1)

Phase voltages and switching states in NNPC inverter

| Phas Outp Phas     | Switching |

|--------------------|-----------|

| II masjoutpji masj | Switching |

| e<br>volta<br>ge<br>,V k | ut<br>level<br>, L k | e<br>swit<br>chin<br>g,<br>Sk | states of<br>each device |        |    |    |        |    |

|--------------------------|----------------------|-------------------------------|--------------------------|--------|----|----|--------|----|

|                          |                      |                               | S1                       | S<br>2 | S3 | S4 | S<br>5 | S6 |

| V dc /2                  | 3                    | 3                             | 1                        | 1      | 1  | 0  | 0      | 0  |

| V                        |                      | 2A                            | 0                        | 1      | 1  | 0  | 0      | 1  |

| dc/6                     | 2                    | 2B                            | 1                        | 0      | 1  | 1  | 0      | 0  |

| -V                       |                      | 1A                            | 0                        | 0      | 1  | 1  | 0      | 1  |

| dc/6                     | 1                    | 1B                            | 1                        | 0      | 0  | 1  | 1      | 0  |

| V<br>dc/2                | 0                    | 0                             | 0                        | 0      | 0  | 1  | 1      | 1  |

### Table (2)

The voltage across the flying capacitor under different phase current and switching states are summarizes in below Table2

|      | ut<br>vo<br>lta<br>ge | Phas e curre nt, I k | The behavior capacitor vol |             |

|------|-----------------------|----------------------|----------------------------|-------------|

| dc/2 | 1, L<br>k             |                      | No change                  | No change   |

|      |                       | >0                   | Decrease(2A                | Decrease(2A |

A Peer Revieved Open Access International Journal

www.ijiemr.org

|           |   |    | ),Increase(2<br>B)                | ),Nochange(<br>2B)                |

|-----------|---|----|-----------------------------------|-----------------------------------|

| dc/6      | 2 | <0 | Increase(2A)<br>,Decrease(2<br>B) | Increase(2A)<br>,Nochange(2<br>B) |

|           |   |    | No change(1A), Increase(1B)       |                                   |

| Vdc<br>/6 | 1 |    | Nochange(1<br>A),Decrease<br>(1B) | Increase(1A)<br>,Decrease(1<br>B) |

| Vdc<br>/2 | 0 | -  | No change                         | No change                         |

For balancing capacitor voltage we need to control NNPC inverters and FCs otherwise FC voltages will differ from their desired value, because there is no control over the currents flow out or into capacitors for balancing voltage the following condition is used.

Vcki = Vcki - Vdc/3

Where

Vcki=capacitor voltages

Vcki=change in capacitor voltage

K=a, b, c

i=1, 2

To balance capacitor voltage Vki is controlled nearer to zero.

How the switching states are selected,

Case (1) if Vcki>0

The switching state is selected in such way

that the capacitor voltage should be decrease

Case (2)

If Vcki<0 the switching state is selected in such way that the capacitor voltage should be increased

The above operation is given below table how the capacitor voltage is decreased and increased based on the selected level.

Table 3 shows the logic controlling of the capacitor Vck1 is given below.

Table (3)

Simplified logic table for Balanced Capacitor Voltage Vck1

| Input<br>conditions | 0             | Output results The selected switching state (Sk) |  |

|---------------------|---------------|--------------------------------------------------|--|

|                     |               | forcontrollingVck1                               |  |

| Lk                  | Vck<br>1*Ik   |                                                  |  |

| 2                   | 0             | 2B                                               |  |

|                     | <b>&gt;</b> 0 | 2A                                               |  |

Case (1) Vck1 <0,the switching state 2A is selected if ik <0,otherwise the switching state 2Bis selected if

ik>\_0,

Case (2) Vck1>\_0 the switching state 2B is selected if

ik<0 Otherwise the switching state 2A is selected if ik>\_0

In this way the capacitor voltage vck1 is completely controlled, independently the flow of current direction in the inverter. Table (4) shows the controlling of capacitor

A Peer Revieved Open Access International Journal

www.ijiemr.org

voltage Vck2.

Table (4)

Logic table for balanced capacitor voltage Vck2

| Input<br>conditio<br>ns |                 | Output<br>results                                     |

|-------------------------|-----------------|-------------------------------------------------------|

| L<br>k                  | Vck<br>2*I<br>k | The selected switching state(Sk) for controlling Vck2 |

|                         | <<br>0          | 1B                                                    |

| 1                       | >0              | 1A                                                    |

Case (1) Vck2<0

The switching state 1A is selected if ik<0, otherwise the switching state 1B is selected if

ik>\_0 Case (2) Vck2>\_0

The switching state 1B is selected if ik<0, otherwise the switching state1A is selected if ik>\_0

### SIMULATION RESULTS: EXISTING RESULTS:

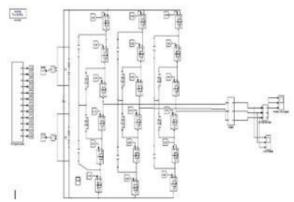

Figure 6.1 Matlab diagram of three phase NNPC inverter for controlling PMSM

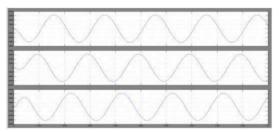

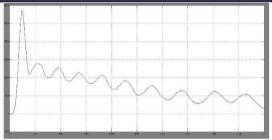

Figure 6.2 filtered voltages

Figure 6.3 Output voltages of NNPC without filter

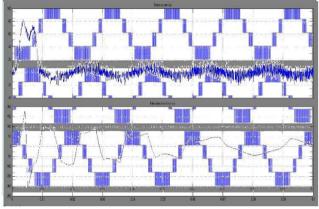

Figure 6.4 capacitor voltage

Figure 6.5 stator current and electromotive force (EMF) of PMSM

A Peer Revieved Open Access International Journal

www.ijiemr.org

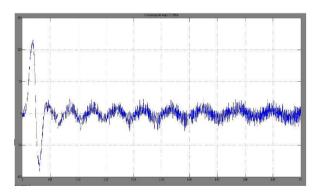

Figure 6.6 speed of the PMSM

#### **CONCLUSION:**

In this thesis we developed A capacitor voltage balancing system for four level NNPC inverter by using logic table switching's and controlling of capacitor voltage in the limited range by switching mode operation purposed. The advantage of this motor reduces the phase switching state to control and balance FC voltage. So that number of computations is reduced and also this system is easy to use with different PWM techniques. The limitations of the method are capacitor size is going on researching. After developing a four level NNPC inverter output is connected to PMSM for controlling. The output of NNPC is filter with RC low pass filter for obtaining approximant sinusoidal input to the PMSM. Finally simulation results are obtain

#### REFERENCES

- (1) B.Wu, High-Power Converters and AC Drives.New York,NY,USA:Wiley/IEEE Press,2006, ch. 1.

- (2) N.Mittal,B. singh,S. P. Singh, R. Dixit, and D. Kumar, "Multilevel inverters: A Literature survey on topologies and control strategies,"in Proc. 2nd Int.Conf. Power,Control Embedded Syst.,2012,pp. 1-11.

- (3) J.Rodriguez, J.-S. Lai, and F. Z. Peng, "Multilevel inverters: A survey of topologies controls, and applications," IEEE Trans. Ind.

(4) R. Stala, "A natural dc-link voltage balancing of diode-clamped inverters in parallel systems, "IEEE

Trans.Ind.Electron., vol.60, no.11,pp.5008-5018.Nov.2013.

- (5) J.Mei, K. Shen , B.Xiao,L. M. Tolbert,and J.Zheng, "A new selective loop bias mapping phase disposition PWM with dynamic voltage balance capability for modular multilevel converter, "IEE Trans. Ind. Electron., vol.61,no.2, pp.798-807.Feb.2014.

- (6) M. Narimani, B. Wu, Z. Cheng, and N. Zargari, "A new nested neutral point clamped (NNPC) converter formediu; voltage (MV) power conversion, "IEEE Trans. Power Electron., vol.29, no. 12, pp. 5259; 5270, Dec.2014.

- (7)A. Choudhury, P. Pillay, and S. S. Williamson, "DC; link voltage balancing for a three; level electric vechicle traction inverter using an innovative switching sequence control scheme, "IEEE Trans. Emerg.Sel.Topics Power Electron., vol.2, no 2,pp. 296;307,Jun.2014.

- (8)Z. Shu, N. Ding, J. Chen, H.Zhu, and X. He, "Multilevel SVPWM With dc; link capacitor voltage balancing control for diode; clamped multilevel converter based STATCOM,"IEEE Trans. Ind. Electron., vol.60, no. 5, pp.1884; 1896, May 2013.

- Busquets; Monge, S. Alepuz. Peracula, Boprdonau, and J. "Voltage balancing control of diode-clamped multilevel converters with passive front-ends, "IEEE Trans. Power Electron., vol. 23, no. 4, pp. 1751-1758, Jul. 2008. (10)S. Busquets-Monge, R. Maheshwari, and S. Munk-Nielsen, "Overmodulation of n-Level three-leg dc-ac diode-clamped converters with comprehensive capacitor voltage balance,"IEEE Trans. Ind. Electron., vol.60, no. 5,pp.1872-1883,May 2013.

Electron., vol.49,no.4,pp.724-738,Aug.2002.

(11)A.H Bhat and N.Langer, "Capacitor

A Peer Revieved Open Access International Journal

www.ijiemr.org

voltage balancing of three-phase neutral-point-clamped rectifier using modified reference vector, "IEEE Trans . Power Electron. vol.29, no.2, pp. 561-568, feb. 2014 (12)J.Pou,R.Pindado , and D.Boroyevich, "Voltage-balance limits in fourlevel diodeclamped converter with passive front ends,"IEEE Trans.Ind.Electrons., vol.52,no.1,pp.190-196,Feb.2005.

(13)P.Chaturvedi,S.Jain,and P. Agarwal, "Carrier-based neutral point potential regulator with reduced switching losses for three-level diode-clamped\ inverter, "IEEE Trans. Ind. Electron., vol.61.no.1, pp. 613-624,Feb. 2014.

(14)M.Khazraei, H.Sepahvand, K.Corzine, and M. Ferdowsi,"A generalized capacitor voltage balancing scheme for flying capacitor multilevel converter," in proc.25th Annu. IEEE Appl. Power Electron. Conf.Expo. 2010,pp. 58-62.

(15)M.Khazreai, H. Sepahvand, K.A.Corzine, and M.Ferdowi, 'Active capacitor voltage balancing in single-phase flying -capacitor multilevel power converter," IEEE Trans.Ind.Electron., vol.59, no.2, pp.769-778, Feb.2012.

(16)B.P.McGrath and D.G.Holmes, "Natural capacitor voltage balancing for flying capacitor converter inducing motor drive," IEEE Trans. Power Electron., vol.24, no.6, pp.1554-1561, Jun.2009.

(17)A.M.Y.M.Ghais, J.Pou, M.Ciobotaru, and V.G.Agelidis, "Voltagebalancing method using phase-shifted PWM for the flying capacitor multilevel converter," IEEE Trans. Power Electron., vol.29, no.9, pp.4521-4531, Sep.2014.

(18)S.Thielemas, T,J,Vyncke, and J.Melkebeek, "Weight factor selection for model-based predictive control of a four-level flying-capacitor inverter,"IET Power Electron., vol.5, no.3, pp.323-333, 2012.