A Peer Revieved Open Access International Journal

www.ijiemr.org

### **COPY RIGHT**

2018 IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 4<sup>th</sup> January 2018. Link:

http://www.ijiemr.org/downloads.php?vol=Volume-7&issue=ISSUE-01

Title: Implementation of ROBA Multiplier Using Approximate Multiplier for High-Speed & Energy-Efficient DSP Applications.

Volume 07, Issue 01, Page No: 6 - 12.

**Paper Authors**

\* MR. NARSAPPA REDDY, MR. SHASHI VEMIREDDY, MR. MIRZA SAJID ALI BAIG , MRS. SHAHEENA KAMRANI.

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

# IMPLEMENTATION OF ROBA MULTIPLIER USING APPROXIMATE MULTIPLIER FOR HIGH-SPEED & ENERGY-EFFICIENT DSP APPLICATIONS

<sup>1</sup>MR. NARSAPPA REDDY, <sup>2</sup>MR. SHASHI VEMIREDDY, <sup>3</sup>MR. MIRZA SAJID ALI BAIG , <sup>4</sup>MRS. SHAHEENA KAMRANI.

<sup>1</sup>Associate Professor, ECM Department, JBIET (T.S), INDIA <sup>2</sup>Working as Embedded developer, Dept of ECE (VLSI and Embedded systems), P.Indra Reddy Memorial Engineering College, (T.S),INDIA,

<sup>3</sup>Associate Professor. Dept of ECE, Patnam Rajender Reddy Memorial Engineering College (T.S), INDIA.

<sup>4</sup>Associate Professor. Dept of ECE, Dr VRK women's college of Engineering and technology, aziznagar, (T.S), INDIA.

narsapa@gmail.com advancedembedded@gmail.com

#### **ABSTRACT:**

In this project, we offer similar speeds but with energy efficiency. This approach is to fit closer to the closest momentum of two. An important part of the computer, so the removal is removed, accelerated and consumed at a small error rate. The proposed approach applies both signing and neglect. We provide three hardware implementations of approximate coefficients that exclude signing and signing for both operations. The effect of the estimated coefficients is evaluated by comparing its efficiency with the exact and exact conditions using different design parameters. In addition, analog effects are seen in two image processing applications - sharp images.

**Keywords** - Accuracy, approximate computing, energy efficient, error analysis, high speed, multiplier.

### **IINTRODUCTION**

Minimizing energy is one of the essential design requirements in most electronic systems, especially laptops such as smartphones, tablets and other devices. [1] It certainly wants this minimized with little effect (speed) [1]. Digital Digital Divisions (DSPs) are a key component of these mobile devices for multimedia applications. The core of these units is the logic of the arithmetic, where Multiply has the largest market share amongst all the operating system arithmetic DSP [2].

Thus, improving performance and efficiency, speeding / multi-effects play an important role in increasing the efficiency of the process. Many DSP servers use image and video algorithms, which ultimately are images or videos that are designed for human use. This fact allows us to use an approximation to optimize energy / energy.

This is due to the ability of people to understand when viewing images or videos. In addition to software for image processing and

[Type text] Page 6

A Peer Revieved Open Access International Journal

www.ijiemr.org

video processing, where there are other areas of operating accuracy, it is not important that the function of the system to this is (see [3] [4]). The use of estimation can give designers the ability to coordinate between accuracy and speed, as well as energy / energy usage [2] [5]. The practice of predicting the arithmetic can be performed at different levels of design, including the level of logic and logic circuits, as well as algorithms and layers [2]. Estimates can be carried out using different techniques, such as allow for some illnesses of the time (eg voltages on magnification or over clock frequency), and method for estimating functions (for example, modifying the boolean function of a chain) or a combination of [4]].

In this type of approach to approximating the function, the proposed multiplication of the arithmetic block is approximated as an addition and multiplication of the different design levels (see [6].). In this article, we focus on low power / energy energy, but still resemble a suitable coefficient for DSP-resistant applications.

### **II.LITERATURE SURVEY**

This section summarizes some of the previous work in your field of expediency. In [3], an approximate and approximate number of approximations was proposed based on a technique called BAM (BAM). Applying a method of bringing BAM [3] to a normal Budh modifier, shows commands at most [5]. Many have estimated that energy savings would be maintained by 28% and reduced by 58.6% of surface area, from 19.7% for 41.8 different lengths of words over regular letters. Kulkarni et al. [6] Proximity proposals with a 2 × 2

coefficient of building blocks were kept incorrectly, with 31.8% of power, -45.4% on the correct coefficients. The approximate 32-bit probes for processing expectation have been designed [7]. It is 20% faster than the full complement with a probability of about 14%. In [8], it is often recommended that the patient be more patient than the calculated calculated result, with the correct quality of distribution, and in an approximate region recorded accurately for the various widths of the bit. In the case of 12 bolts, more than 50% of energy savings have been reported. At two circuits 4: 2 were designed and analyzed for use in DDR3 multipliers.

The use of multiplication in applications for image manipulation, leading to reduced power consumption, delay, and number of transistors compared to real coefficers are discussed in the literature. In Proposed Multiple Architecture (ACMA) which can be configured with a precision, tolerable error.

To increase the productivity of ACMA, use a technique called predictions of practices that work on an excessive computation basis. Compared to what exactly the proposed approximate estimates result, reducing by nearly 50% by reducing the main road. Likewise, Bhardwaj Describes the number of Wallaceous Tree (AWTM) trees. Again, he referred to the transfer of predictions to reduce the main road.

#### **III EXISTING SYSTEM**

Most of the approximate delayed approaches proposed previously depend on structural changes or the reduction of the complexity of

A Peer Revieved Open Access International Journal

www.ijiemr.org

the precision. In this project, we propose similar approximations by making simple operations. The difference between our work

and is that, although both policies are the same for most non-signatories, the average error of the proposed method is smaller. We also offer some similar techniques when multiplied by multiple signatures.

### IV PROPOSED SYSTEM

approximate Proposed approximate coefficients in the region were created by conventional changing the method to multiplying the algorithms by accepting input values. We call this case of probability coefficients (RoBA). The proposed multiplication method is applicable to signed non-essentials. where three fine and architectures are displayed.

The efficiency of these structures is evaluated by comparing the use of electricity and energy, energy reductions, energy consumption, and areas of similar and appropriate cement. The contribution of this project can be summarized as follows:

- 1) Introducing a new propaganda scheme by changing the simple multiplication method

- 2) A description of the three hardware architectures of the proposed value plan for the signature and drop operation.

#### V. METHODOLOGY

A completed version of our work [3]. Expanding our project [3] By giving two simplified versions, there is MA. We have

introduced methods that can be used to maximize the maximum energy savings used, similar to the pill, to specific calibration criteria. Our contribution to this project is summarized as follows

- 1) In order to simplify the logical complication of the cell, there is a simple MA, reducing the number of transistor and integral capacity. Given this goal, we offer five different versions with a simple MA, which guarantees a minimal error in the table with the Real Factor (FA).

- 2) In order to maintain the reasonable results, we use FA cells similar to the least significant LSBs. In particular, we focus our efforts on the FA Framework structure using a base block cell base. Preferred Plane of Adder Save (CSA) and Escalator Rates (RCA).

- 3) The most popular technician is achieving great improvements in energy consumption. However, you will lead to the failure of the most significant bit delay (MSBs). This can lead to huge errors in the resulting output and seriously misrepresents the output quality of the program. We use similar FA cells, especially at LSBs, while MSBs use FA cells correctly.

- 4) We have predicted the algorithm for noise canceling (LMS algorithms) using proposed arithmetic equivalents and evaluating similar architecture in terms of quality of output and power dissipation.

- 5) Finally, we suggest methods for optimizing using systematic abortion system abortion (LMS algorithms).

A Peer Revieved Open Access International Journal

www.ijiemr.org

#### **VI.RESULTS**

### **EXISTING RESULTS**

| Device Utilization Summary                     |      |           |             |         | Ŀ |

|------------------------------------------------|------|-----------|-------------|---------|---|

| Logic Utilization                              | Used | Available | Utilization | Note(s) |   |

| Number of 4 input LUTs                         | 436  | 4,896     | 8%          |         |   |

| Number of occupied Slices                      | 225  | 2,448     | 9%          |         |   |

| Number of Slices containing only related logic | 225  | 225       | 100%        |         |   |

| Number of Slices containing unrelated logic    | 0    | 225       | 0%          |         |   |

| Total Number of 4 input LUTs                   | 437  | 4,896     | 8%          |         |   |

| Number used as logic                           | 436  |           |             |         |   |

| Number used as a route-thru                    | 1    |           |             |         |   |

| Number of bonded <u>IOBs</u>                   | 32   | 158       | 20%         |         |   |

| Average Fanout of Non-Clock Nets               | 2.78 |           |             |         |   |

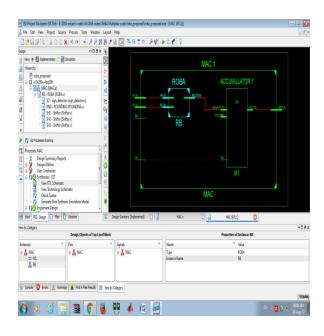

Fig 1: Design Summary

Fig 2: RTL schematic

Fig 3: synthesis report

Fig 4: simulation results

Fig 6: Technology schematic

A Peer Revieved Open Access International Journal

www.ijiemr.org

### **PROPOSED RESULTS:**

Fig 7: Design summary of proposed system

Fig 8: Schematic diagram of proposed multiplier

Fig 9: Simulation Results

Fig 10: synthesis report

A Peer Revieved Open Access International Journal

www.ijiemr.org

Fig 11: technology schematic

#### VII.CONCLUSION

In this project, we have proposed an approximate speed multiplier, but the energy is called the ROBA coefficients. The high accuracy requested multiplier is based on the input inverse of the 2n entry. This excludes the enormous calculation of this multiplication by improving the speed and power consumption at the cost of a small error. The proposed approach is applicable to the signed and unnecessary components. Three hardware implementations of approximate coefficients, including one for the unigned and two for signed transactions, were discussed. suggested multiple effects are evaluated by comparing them with a number of approximate and approximate uses of different design

parameters. The results show that, in most cases (all), the RoH multiplier architecture exceeds the approximate number (absolute). Also, the effectiveness of suggested approximate approaches is investigated in two image processing and smooth application. Comparison shows the same image properties as the number of real multiplication rules.

#### VIII. REFERENCES

- [1] M. Alioto, "Ultra-low power VLSI circuit design demystified and explained: A tutorial," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 59,no. 1, pp. 3–29, Jan. 2012.

- [2] V. Gupta, D. Mohapatra, A. Raghunathan, and K. Roy, "Low-power digital signal processing using approximate adders," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 32, no. 1, pp. 124–137, Jan. 2013.

- [3] H. R. Mahdiani, A. Ahmadi, S. M. Fakhraie, and C. Lucas, "Bio-inspired imprecise computational blocks for efficient VLSI implementation of soft-computing applications," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 57, no. 4, pp. 850–862, Apr. 2010.

- [4] R. Venkatesan, A. Agarwal, K. Roy, and A. Raghunathan, "MACACO: Modeling and analysis of circuits for approximate computing," in *Proc. Int. Conf. Comput.-Aided Design*, Nov. 2011, pp. 667–673.

- [5] F. Farshchi, M. S. Abrishami, and S. M. Fakhraie, "New approximate multiplier for low power digital signal processing," in *Proc. 17th Int. Symp. Comput. Archit. Digit. Syst. (CADS)*, Oct. 2013, pp. 25–30.

- [6] P. Kulkarni, P. Gupta, and M. Ercegovac, "Trading accuracy for power with an

A Peer Revieved Open Access International Journal

www.ijiemr.org

underdesigned multiplier architecture," in *Proc.* 24th Int. Conf. VLSI Design, Jan. 2011, pp. 346–351.

[7] D. R. Kelly, B. J. Phillips, and S. Al-Sarawi, "Approximate signed binary integer multipliers for arithmetic data value speculation," in *Proc. Conf. Design Archit. Signal Image Process.*, 2009, pp. 97–104.

### **AUTHORS**

Mr.Narsappa reddy, M.Tech(Ph.D), Associate Professor, ECM Department JBIET (T.S), INDIA. He has total Teaching Experience (UG and PG) of 17 years. He has guided and co-guided 57 P.G students. His Research areas included VLSI system Design, Digital signal Processing, Embedded system.

**Mr.Shashi Vemireddy**, PG Scholar, Dept of ECE (VLSI and Embedded systems), P.Indra Reddy Memorial Engineering College, (T.S),INDIA. 6 years of experience as EMBEDDED DEVELOPER. Now organizing "TRUEVOLTS" in Hyderabad.

Mr. Mirza Sajid Ali baig, Associate Professor. Dept of ECE, Patnam Rajender Reddy Memorial Engineering College (T.S), INDIA.

Mrs. Shaheena kamrani, Associate Professor. Dept of ECE, Dr VRK women's college of Engineering and technology, aziznagar, (T.S), INDIA.